���̃y�[�W�ł́A���ЂŊJ������IP��g�����X���[�^���g����VHDL�R�A��Verilog�ɖ|�����́AOpencores��Verilog�����Љ�Ă����܂��B

�Ƃ肠�����A�����̐v���ʂ��āACPU�A�[�L�e�N�`���AHDL�R�[�f�B���O�Z�@�̌����ɂ����ɂȂ�K���ł��B

1.�x���`�}�[�N�e�X�g

�@�@����C�\�[�X�v���O�������V�~�����[�^��œ������đ��N���b�N����]�����Ă݂܂��BC�\�[�X�v���O�����́A���[�h�\�������i�T�C���^�[���[�u�A3�d�����j�ł��B���L�I�[�v���\�[�X�R�A�ɂ��čs���܂����B

�쓮���g���̔�r�ł͂Ȃ�CPI�̔�r�ł��邱�ƂƁA�I���W�i���Ƃ̔�r�ł͂Ȃ��AOpencores��ł̔�r�ł��邱�Ƃɒ��ӂ��Ă��������B

- SH2

- T80( translated to Verilog by automatically with Veritak Translator)

- TV80 (T80�̉��ɂ���܂��B�j

- WB_Z80(T80�̉��ɂ���܂��B�j

- FZ80(T80 �̉��ɂ���܂��B�j

- AVR

- 8051�iREV.1.01�j

- MIPS R3000�iMay.12.2004 Update�F Synthesizable on Altera CYCLONE)

- H8300H( Jun.9.2004)

- Openrisc (May.6.2005�j

���ӁF�R���p�`�u���R�A�́A�I���W�i���Ɩ��߂̎��s�X�e�[�g�����قȂ�܂��B�����܂ŃI�[�v���\�[�X�R�A��̎��s���Ԕ�r�ł��邱�Ƃɒ��ӂ��Ă��������B

���̕]���̊ϓ_�Ƃ��ẮA�����N���b�N���g���ŋ쓮���Ă��܂��̂ŁiRTL�V�~�����[�V�����A���z�T�OMH���j�A���ԁ��N���b�N���ł悢�Ǝv���܂��BC�R���p�C�����܂߂�CPI�̕]���ɋ߂����ƂɂȂ�܂��B

�܂��A8�r�b�g���Z����̂Ȃ̂ŁA8�r�b�gCPU�ɂƂ��ĕs���ɂ͂Ȃ�Ȃ��i8�r�b�gCPU�����ӂȂ͂��́j�x���`�}�[�N�ɂȂ��Ă��܂��B

�@�ʔ����̂́A��̐v���㏇�ɕ���ł��邱�Ƃł��B

H8300H�́A�M�҂ɂ��vVersion�ł����A�I���W�i�����R0%�ȏ�CPI�����������Ă��邽��AVR��葬�����ʂɂȂ��Ă��܂����A�I���W�i���̎��s�X�e�[�g���ł�AVR�Ɠ����ł͂Ȃ����Ɛ��@���܂��B

����ɁAAVR�͔�r�I�ŋ߂̐ł��Q�[�g����H8�R�O�OH���͂��Ȃ菭�Ȃ��ƌ����܂��BCISC����RISC�̗���A�A�[�L�e�N�`���̐i�������̃O���t����ǂ݂Ƃ��Ǝv���܂��B

����ȗ���̒��ŁARISC�̑������I���݂ł���MIPS��80�N��̐v�ł��B

MIPS�̐挩������Ă��܂��ˁB�I���W�i��CPU��v����ɂ������Ăǂ���K�͂ɂ���ׂ����Q�l�ɂȂ�̂ł͂Ȃ��ł��傤���H

�@�Ȃ��AYACC�͕M�҂ɂ��v�ł�͂�PLASMA�Ɠ���MIPS�A�[�L�e�N�`�����K�͂ɂ��Ă��܂��B

�ڍׂ��AYACC�v���W�F�N�g�̃y�[�W�����Q�Ƃ��������B

�܂��A�I���W�i��CPU������Ă�����������܂����BYACC�Ɣ�r���Ă��������Ă��܂��B�Ȃ��200MHz�I�[�o�Ƃ�����������ł��B�������ADMIPS/MHz��1���鎖��_���Ă���Ƃ����������2�{�ł��B

�i�V���O���łP����̂́A���Ȃ�̍œK���R���p�C�����Ȃ��ƁA�������������܂��B�j

�ł��A�A�C�f�A��������ŁACPU������Ă��܂��B�B���̏��́A�����D���Ō��Ă��Ă��y�����ł��B�A�[�L�e�N�`�����玩�삷��̂́A�{���Ɋy�������̂ł��B

MAX2�œ����A�I���W�i��CPU�삵�Ă݂܂����B�͂�240�Z���œ��삵�܂��BCPU�v�̓���҂Ƃ��������ł����A16�r�b�g���Z�Ńp�^�[���������ł��A���p�����Nj����Ă��܂��B

�B�܂��AVPI�ō쐬�������͂�Visual�f�o�b�K���t�����Ă���ACPU�̓��쌴���̗����ɖ𗧂Ǝv���܂��B

<Z80�ɂ���>

PC8001�ŗL����FZ80�R�A��lj����܂����B

FZ80���AWB_Z80���čő���CPI�AZ80�R�A�ƂȂ�܂����B4�{��Z80�R�A�����낢�܂����B�����@�\������������̂ł���Ȃ���A����Coding���@�̈Ⴂ������Ɩʔ����ł��傤�BT80��TV80�́ABehavior�ŏ����Ă��܂��B

����AWB_Z80/FZ80�̓Q�[�g���x���ɋ߂������������Ă��܂��B������̍����o�₷���̂́A���ۓx�̍���Behaivor�ŁA�_�������\�ƃQ�[�g���Ō��ʂ����悢�̂́A

�Q�[�g���x���ɋ߂��i��H�}�ɋ߂��j�����������Ă�����ł��傤�BFZ80�́A�R���p�C���̕n�㐫������8051�ɔ��鐦�����̂�����܂��B�������A���̃R�A���AVersion1.04�ȑO�ł́A���̃x���`������܂���ł����B

���J�������ۂɎg���遁��Feedback�Ƃ����T�C�N���̐}��������悤�Ɏv���܂��B���̗���ɂ��܂����Ǝ��R�Ɗ����x���オ���Ă����̂ł́H�Ǝv���܂����B

���̂ق���6502���g�����R�A������̂ł����A�K����C�R���p�C���������炸�A���ۏ�ԂɂȂ��Ă��܂��B

CPU�A�[�L�e�N�`���̌����ɂ́AMIPS�A�[�L�e�N�`������͂��邱�Ƃ������߂��Ă��܂��B

Z80���͂邩�ɃV���v���ȃf�R�[�_�́A����Ƃ��čł��K���Ă���Ǝv���܂��BSimple�@is�@best�̐v�v�z���т��ꂽ�A�[�L�e�N�`���ɂȂ��Ă��܂��B���Ƃ��AH�W��ALU�L�q��YACC��ALU�L�q�A�f�R�[�_���r���Ă݂Ă��������B�@

�f�R�[�_�̔�r�́AYACC��5�i�p�C�v���C�����A������̑��x�ő����ӎ��O�ꂵ���������ɂȂ��Ă���̂ŒP���Ȕ�r�͂ł��Ȃ��̂ł����A�\�[�X�����Ă�����������̃V���v��������������ł��傤�B�@

�܂��A�L���ȃw�l�p�^�{�̃��f��CPU�@DLX�́AMIPS�A�[�L�e�N�`���̌��_�ɂȂ��Ă��܂��B�iDLX�̃R���p�C����T����茻����GCC������܂��B�j

�@�����āANios�U�i�A�[�L�e�N�`�����ύX����܂����B�j�AMicroBlaze���AMIPS�A�[�L�e�N�`���ɍ������Ă��邱�Ƃɂ��C�Â��ł��傤���H

�n�[�h�E�F�A���V���v������������̑��x���グ�₷�������쓮���g��UP����DMIPS�̌���A�Ƃ����}���ɂȂ��Ă��܂��B��}�́ACPI�ł̔�r�ł����A������̑��x�iDMIPS)�ł́A����ɍ����J�����ƂɂȂ�܂��B

SH2��RISC��RISC�Ȃ̂ł����A16�r�b�g�ɖ��߂����߂�@�\��CISC�I�Ȗ��߂��������肵�āAMIPS�A�[�L�e�N�`�����f�R�[�_�̕��S�́A�d���͂��ł��B

�@

Openrisc���U���Ȃ��̂́A1�|�[�gRAM�ŋ쓮���Ă��邱�Ƃ�����܂����A�L���b�V����MMU��ςނƂ��̕��̃I�[�o�w�b�h���傫���Ȃ邹���ł��傤�B�iPLASMA�́A1�|�[�gRAM�쓮�ŁA����Ƃ̔�r�ł��B

�����FDATA /Instruction���WKB�L���b�V���jDIV���Z��Native�ŃT�|�[�g���Ă��Ȃ����Ƃ������āA�R�[�h�T�C�Y����剻����̂��C�ɂȂ�܂����B����ɂ��Ă��A���������撣���͂��Ȃ̂ł����B�B

�蕨����ŁA�o�ꂵ�������ɂ�����Ǝ₵���C�����܂��B

�����v�����̂́Aopencores����Â���ADamjan Lampret�Ƃ����l�ŁA�����X���x�j�A�A�����u�����i��w�̈�w���Ƃ����̂́A���Q�ɒl���܂��B����AOpencores���ǂ̂悤�Ȉʒu���߂�̂������[���ł��B

�@

2. AES�R�A�i�I���j

�@�@CQ�o�ŎЂ̃f�U�C���E�F�[�u�R���e�X�g�Q�O�O�S�ɉ��債���v���|�[�g�ł��i���M�C�����Ă��܂���j�B

�@�@AES�͎������DES�ɑ���Í��R�A�ł��B�ۑ�́AAES�Ɏg����SUBBYTES�Ƃ������i��v������̂ł������A���ꂾ���ł́A���p�I�ł͂Ȃ��̂ŁAAES���̂��̂�v���Ă��܂��܂����B

���\�C�������Đv�����̂ł����A�ɂ������w�͏܂Ƃ������ʂɏI���܂����B

�Ƃ͂����ALUT2500���x�iLUT�����Ȃ�G���t�^�ɂ��Ă���FPGA�ɓ���܂��B�j�ŁACLOCK200MHz���A�X���[�v�b�g2.7G�������́AFPGA�Ƃ��Đ��E�ő��ł͂Ȃ����Ǝv���܂��B

�{�R�A�́ATOP�K�w�Ńp�C�v���C������FIFO���C���X�^���X�����Ă���̂ŁA�e�ՂɊg���ł���悤�ɂ��Ă��܂��B���_�I�ɂ́A�C���X�^���X�����P�O�ɂ���A10�{�̃X���[�v�b�g�ɂȂ锤�ł����A��������Ƃ������肷��悤�Ȍ��ʂɂȂ�܂��B

�����FPGA�ŁA���E�ɋ߂��g����������Ɣz���x�����{�g���l�b�N�ƂȂ邽�߂ł��B���ł��Ȃ��_����5ns���Ă��܂����ƂɈ��R�Ƃ��Ă��܂��܂��BFPGA�ł���K�͂ȃ��W�b�N�͂�����ƃt���[�A�v���������Ȃ��Ƃ����Ȃ��Ƃ������Ƃł��傤�B

3.H8�݊�CPU�̐v�iUnder�@Development Jul.28.2004�@Update�j

�I�[�v���R�A�Ŗ����N����ڂ����Ă��Ȃ����́A��r�I���W���[�AGCC���������̂Ƃ������ƂŁAH8300H��v���Ă݂܂��B

�Ƃ肠�����A�d�l�́A��v�Ȗ��߂���荞�T�u�Z�b�g�d�l�Ƃ��܂��B

���㕨��CPU�Ȃ̂ŁA�I���W�i��CPU�v�ׂ̃��t�@�����X�ɂ͂Ȃ蓾�܂��A��{�I�Ȑv��@�́A�}�C�N���v���Z�b�T�̎d�g�݂𗝉������ŎQ�l�ɂȂ�Ǝv���܂��B

�V�~�����[�^��Ńh���C�X�g�[���x���`���v�����܂����B

H8�@BASIC���Ȃ�ƃA�Z���u���ŏ����Ă�������݂��܂����B���̂����V��ł݂����Ǝv���܂��B

���v�]�����������Ă��܂����A������YACC�Ɣ�ׂ��DMIPS/���\�[�X�䂪1/20���炢�ɂȂ��Ă��܂��̂ŁA���`�x�[�V�������Ⴂ�ł��B

CPI�d�����̂ĂāA���S�ȃ}�C�N���R�[�h�����iROM���j���������A���\�[�X�����Ȃ��ł��AFPGA�������ȁA�Ǝv���܂��B

�RE�̃X�^�[�^�ł́A32MB��RAM����������Ă���悤�Ȃ̂ŁA

UCLINUX�̂悢�v���b�g�t�H�[���ɂȂ�\��������܂��B

�Ȃ�ƁAH8�ŁATCP/IP�������Ă�����������܂����B����́A�ʔ����ł��B�����AH8�v���W�F�N�g�œ����悤�ɂ�����AC����ƁAFPGA�ƁA

CPU�ƃA�Z���u���ƃC�[�T�l�b�g��TCP/IP��Verilog-2001���ꏏ�ɕ��ł���i�V�ׂ�j�A�������ς̂悤�Ȑ����v���W�F�N�g�ɂȂ邱�Ƃł��傤�H�I

�i�RE�́ALAN��PHY�����Ă���悤�ł��B�j

�@�J��Snapshot�@

�Ȃɂ��ς���Ă��܂��ARTL�\�[�X��Veritak�@Project�ł��B�c�[���̃\�[�X���ǂ����玝���Ă������Y��Ă��܂��܂����B

HEX�t�@�C���́A��̓����x���`�}�[�N�ɂȂ��Ă��܂��B�i�������́AAltera���C�u�������g�p���Ă��܂����A�A�[�J�C�u�́A�܂�ł��܂���B

�ʓr�Aaltera_mf.v ��COPY�Aset ���Ă��������B�j

�S�DYACC�v���W�F�N�g�iYet�@Another�@CPU�@CPU�̗�??�ł��B �@ Opencores���y�[�W�ł��B�j

=>

���̂悤�Ȏ��₪����܂����̂ŁA�����܂Ƃ��Ȋ��荞�݃R���g���[�����L�q���Ă݂����Ǝv���܂��B

Hi Tak-san,

Couple of months ago I successfully interfaced Yacc with a dsp hardware blocked. I was able to program hardware blocks configuration registers and share its RAMS.

Now I want to interface interrupts generated by the hardware block to YACC.

The main idea is that when once the hardware block has finished its job it raises the interrupt.

This interrupt causes the yacc to jump to a interrupt service routine which inspects some registers, sets up the next task and returns to normal execution.

�܂��A�}���`�^�X�N�X�C�b�`����AVCM�ɂ��f�W�^���T�[�{�R���g���[�����L�q���A�T�[�{�V�~�����[�V�������ėV��ł݂܂��傤�B�B

���}���`�^�X�N�X�C�b�`����

OS���K�v�ȃ��x���ł͂Ȃ�����ǂ��^�X�N�͕��������A����ȑg�ݍ��ݗp�r�ɂт�����ł��B�e�^�X�N�́A

�@task_switch();

���ĂԂ��ƂŐ�ւ��܂��B�@�Ⴆ�AUART�̏o�͂����Ȃ���A�R�}���h������ĉ�͂�����B�B�����̃^�X�N�́A�����̎d�����Ђƒi��������A����

�^�X�N�ɃX�C�b�`���܂��B���Ԃ�����Ă�����A�܂����������邱�Ƃ��Ď��ɓn���܂��B�^�X�N�����Ԃɉ�邾���ł����A�e�^�X�N�́A��p�̃X�^�b�N�������Ă���̂ŁA

�����̎d���ɐ�S�ł��܂��BMIPS�̏ꍇ32�����W�X�^������̂ŁA�^�X�N��ւ��̃I�[�o�w�b�h���傫���̂ł����A�����͂悵�Ƃ��܂��傤�B

�T�[�{�́A��莞�Ԗ��̏������K�v�Ȃ̂ŁA��L�Ƃ͕ʂ�Timer���荞�݂ɂ��ŗD�揈���ɂȂ�܂��B

�Ƃ肠�����A

�@�E���荞�݃R���g���[���̎d�l���߁B

�@�EHDL�L�q

�@�E���荞�݃��[�`���̐��`�L�q

�@�E�^�X�N�X�C�b�`�̋L�q

�@�E�f���T�[�{�̎d�l����

�@�E�T�[�{�R���g���[���̋L�q

�@..

���\����܂��ˁB�B

�ŏI�I�ɂ́A�V�~�����[�^��ŁACPU�������ăT�[�{���O���ɂ߂����ɖڕW�ɒǏ]����l�q�����Ă݂����Ǝv���܂��B

YACC�ɂ��ẮA�O���p�X�ɐڑ��\��CPU�̐v�Ƃ������Ƃ��������ōĐv���ł��B

DWM�f�U�C���R���e�X�g2006�㋉�ۑ������

�V�X�e��(�A���S���Y���E�A�[�L�e�N�`��)�v�Ɏn�܂�ARTL�@�R�[�f�B���O�A�Q�[�g�V�~�����[�V�����ƁA���Ƃ��Ă����܂Ƃ܂����L�q�Ƃ����̂́A

��Ƃ�E�������̉���ɂ�����̂ŁA���܂���J����Ă��Ȃ��悤�Ɏv���܂��BVerilog�@HDL�ʼn���I�������̂́A�܂���Ȃ�ɂ��P��̌���őS�Ă��L�q�ł��邱�Ƃł��B

���́A

- �V�X�e��(�A���S���Y���E�A�[�L�e�N�`��)�v

- RTL

- �Q�[�g���x��

�R���e�X�g�Ƃ������ʂ̑�ނ���āA��́i���p�I�ȁjIP���쐬���邱�Ƃ��y����ł��܂����A�����ł��Q�l�ɂȂ�L�q��������K���ł��B

�P��̃R���e�X�g�̋G�߂ɂȂ�܂����B�������_����݂̏o�肪�����̂ł����A���N�̖��́A���ł͂Ȃ��ł��傤���H

���̐ϕ����̃f�R�[�_�́A�^�[�{������LDPC�Ƃ������ŋ߂̕������_�̐��ʂ̃G�b�Z���X�ɔ�����̂ł��B

���̂悤�ɁA��M�l�̃A�i���O�l���g���Ē����m�������コ�����������iSoft Decision)�ƌĂ�ł��܂��B

�P.����

�V�X�e���̃V�~�����[�V������Verilog�@HDL�ōs�����Ƃ����AWG�iadditive white Gaussian )�@Noise������K�v������܂��BVerilog�@2001�ł́A

$dist_normal���ŁAAWGN���ł���̂ł����A�c�O�Ȃ��ƂɎd�l��A���́E�o�̓p�����[�^���Ainteger�ɂȂ��Ă��āA�ʎq���덷��

�܂Ȃ��Ƃ���œ����Ă��܂��܂��B�i�ǂ����āA���̂悤�Ȏd�l�ɂȂ������S���Ӗ��s���ł��B�j�@���z�l�Ƃ̔�r�������ł��A�ŏ���

�����́A�ʎq���덷�̓���Ȃ�real�i������ł�double)���x�ŊȒP�ɍs�������ł��ˁB�����ŁAVeritak�ł́Areal�ł�$normal_vtak��VPI�ō쐬���Ă݂܂����B(1.83����r���g�C�����Ă��܂��B�j

����ŁAC�ŏ����Ȃ��Ƃ��A�ŏI��Hard��H�̌��܂ŁAVerilog�@HDL��Ŏ��R�ɋL�q���邱�Ƃ��ł��܂��B

�P�D�P�@$dist_normal�̎g����

�T���v���ł��B

//Oct.11.2005

//random_sn.v

module random_sn;

parameter integer No=10;

real sd,mean;

real a;

integer seed1;

integer i;

real sdf_array[0:No-1] ;

real sum,avg,sd2;

real expected_mean=-10;

real expected_sd=2.0;

integer result;

initial begin

#10;

seed1=0;

sum=0;

for (i=0;i<No;i=i+1) begin

`ifdef Veritak

a=$normal_vtak(seed1,expected_mean,expected_sd);

`else

result=$dist_normal(seed1,$rtoi(expected_mean),$rtoi(expected_sd));

a=$itor(result);

`endif

sdf_array[i]=a;

sum=sum+a;

$display(" a=%f seed=%d",a,seed1);

end

avg=sum/No;

sum=0;

for (i=0;i<No;i=i+1) begin

a=sdf_array[i]-avg;

sum=sum+a*a;

end

sd2=sum/No;

`ifdef Veritak

sd=$sqrt(sd2);

$display("Total %d ",No);

$display("Expected Avg=%f SD=%f ",expected_mean,expected_sd);

$display("Results Avg=%f SD=%f SD2=%f",avg,sd,sd2);

$display("Difference Avg=%f SD=%f",$fabs(expected_mean-avg),$fabs(expected_sd-sd));

`else

$display("Total %d ",No);

$display("Expected Avg=%f SD2=%f ",expected_mean,expected_sd*expected_sd);

$display("Results Avg=%f SD2=%f",avg,sd2);

`endif

end

endmodule

Veritak�̎��s���ʂł��B���̃v���O�����ł́A���ρimean�j=-10.0, �W����=2.0�_���Ő������Ă��܂��B

F:\regression_test\complex\random_sn.v(3)::random_sn

Verilog�̃V�~�����[�V�����̏������������܂����B�X�^�[�g��,Go�{�^���������Ă��������B

------------- �V�~�����[�V�������J�n���܂��B--------------------

a=-9.107809 seed= 1082744015

a=-9.710610 seed= -958425333

a=-9.057617 seed=-2032678137

a=-7.126455 seed=-1634874387

a=-12.131116 seed= 1427361855

a=-9.270853 seed= 1735824513

a=-11.797993 seed= 1657425015

a=-7.087418 seed= 1586374365

a=-12.799056 seed=-2056026887

a=-13.158670 seed=-1872486481

Total 10

Expected Avg=-10.000000 SD=2.000000

Results Avg=-10.124760 SD=2.108805 SD2=4.447058

Difference Avg=0.124760 SD=0.108805

ModelSim�̎��s���ʂł��B

# Loading work.random_sn run -all # a=-9.000000 seed= 1082744015 # a=-10.000000 seed= -958425333 # a=-9.000000 seed=-2032678137 # a=-7.000000 seed=-1634874387 # a=-12.000000 seed= 1427361855 # a=-9.000000 seed= 1735824513 # a=-12.000000 seed= 1657425015 # a=-7.000000 seed= 1586374365 # a=-13.000000 seed=-2056026887 # a=-13.000000 seed=-1872486481 # Total 10 # Expected Avg=-10.000000 SD2=4.000000 # Results Avg=-10.100000 SD2=4.690000seed �́Arandom�̎�A�ł��ꂪrandom��SEQ�����߂Ă��܂��BVerilog�@2001�ł́A�����݊��Ȃ̂ŁA����seed��^����A

�V�~�����[�^�Ɉˑ������A��������SEQ�ɂȂ�܂��B$dist_normal���ĂԂƁAseed&�ŌĂ݂����Ɏ��̂�eed�l���Ԃ��Ă��܂��B

����Ăяo���ł́A���̕Ԃ��Ă����l�ŌĂԂ��ƂŁAAWGN�ɂȂ�܂��B$dist_normal�ł́A�����ŕԂ��Ă��Ă��܂��_��SD����̌덷��

�傫���Ȃ��Ă��܂��܂��B

�����ŁA����ȍ~�́AVeritak�Ǝ��V�X�e���^�X�N���g�����Ƃɂ��܂��B

�����A�T�[�x�C���Ă݂܂����B�ۑ�́A���������p���e�B�R�[�h��Sum-Product�A���S���Y���ʼn����Ă��܂��B�p���e�B���������Ⴄ�̂�

LDPC�ł͂���܂������@�́ALDPC���̂��̂ł��B

�Ƃ肠�����A�d����ł�1�r�b�g�̌������͂ł��܂��BHamming�@Code�́A������7�r�b�g�ŁA1�r�b�g�����ł��܂�����A���ꂾ��������ƁA

�����͂悭����܂���BBP�iBelief�@Propagation�j�����@���^��������̂́A���̂悤�ȒZ���������ł͂Ȃ�

������x�����������ł��B�������A����̕����́ALDGM�Ƃ����p���e�B�̍����ɂȂ��Ă��āALDPC�ɔ�ׂē��������m���Ă��܂��B

�d����̃X�g���e�W�̌���

���\�ŁAy0-y3���f�[�^�Aro-r1���A�s�p���e�B�Ac0-c1����p���e�B�ŁAy0-y3-r0-r1-c0-c1�̏��ő���܂��B

| y0 | y1 | r0 |

| y2 | y3 | r1 |

| c0 | c1 |

�@�P���Ƀp���e�B�}�g���N�X�����ɏ��������ƁA

�@y0+y1 +r0 =0 -(1)

y2+y3+ r1 =0 -(2)

y0+ y2+ +c0 =0 -(3)

y1+ y3 +c1=0 -(4)

�ɂȂ�܂��B�@�����ŁA������G���[�����������Ɖ��肵�܂��B

���p���e�B�r�b�g�ɔ��������ꍇ��

�@���̏ꍇ�́A�e�o���e�B�́A(1)-(4)�܂ŁA�Ɨ��������ɂȂ��Ă��܂��B���������āA(1)-(4)�܂ł̂ǂꂩ�A�ꎮ�������A�������Ȃ��P�[�X�́A

�p���e�B�r�b�g�̃G���[�ƍl���邱�Ƃ��ł��A�f�[�^�r�b�g�iy0-y3)�̒����͕K�v����܂���B

���f�[�^�r�b�g��1�̃f�[�^�G���[�����������ꍇ��

�@����y0�ɃG���[��e0���������Ƃ��܂��B��������ƁA�������Ȃ��̂́A(1)�A(3)�����ɂȂ�܂��B

���l�ɂ��Ĉȉ��̂悤�ɂ܂Ƃ߂邱�Ƃ��ł��܂��B

| 1�̃G���[ | �p���e�B�G���[�ƂȂ鎮 | ���� |

| y0 | (1),(3) | y0^=1; |

| ���P | (1),(4) | y1^=1; |

| y2 | (2),(3) | y2^=1; |

| y3 | (2),(4) | y3^=1; |

| r0 | (1) | �K�v�Ȃ� |

| r1 | (2) | �K�v�Ȃ� |

| c0 | (3) | �K�v�Ȃ� |

| c1 | (4) | �K�v�Ȃ� |

2�G���[�����������ꍇ�́A�ǂ��ł��傤���H�P���ɂ́A�s���Ȃ��ł��ˁB���Ƃ��Ay0,y1�ɃG���[�����������ƂƁAc0,c1�ɃG���[�����������Ƃ�

��ʂł��܂���B�G���[�����������Ƃ́A���o�ł������ł����A�����܂ł́A�ł��܂���B����ɁA�R�G���[����ƁA1�̃G���[�Ƌ�ʂł��Ȃ��Ȃ�A

������̉\��������܂��B4�G���[�����Ƃ���ƁA�G���[�����������Ƃ��猟�o�ł��Ȃ�\��������܂��B

�i��ʂɁA�����ƌ�����́A�m���̈Ⴂ�ł�������܂���B��������V�X�e���́A�K��������m���ɂ��čl�@����K�v������܂��B�j

���̃f�[�^�́A4�r�b�g�ł�����A�����̎�ނ́A���X16��������܂���B�������p���e�B��������8�r�b�g���Ȃ킿256��ނ�

Data��M�̉\��������܂��B��M�����A256��ނ̃f�[�^�i�A�i���O�ōl����Ɩ����ɂ���܂����j�́A���̂P6��

�ǂ�Ɉ�ԋ߂��ł��傤���H�Ƃ������ł��B�@��ԋ߂��f�[�^������A�ł��G���[�m�����������ł���悤�ȋC�����܂��ˁB

�ł́A��ԋ߂��Ƃ������Ƃ��ǂ��\���ł���ł��傤���H���ꂪ�����Ƃ����T�O�ł��B

�n�~���O�����ƃ��[�N���b�h����

����̉ۑ�ł́ALDGM��BP�Ƃ����̑��Ƀ��[�N���b�h�������r���铚�Ă����邾�낤�Ǝv���܂��B

����ł́A�n�~���O�����ɂ��Č��Ă����܂��傤�B

���̃v���O�����ł́A�����̑S���[�h���o�͂��Ă��܂��B

//�ۑ�̕�����S������

//Brute Force�ɍŏ������ׂ�

module dwm1_test;

reg [3:0] data;//Encode���錳Data��WORK

reg [7:0] code_array[0:15];//�S�R�[�h���[�h���i�[����

reg [7:0] work,a,b,c,d;

wire [7:0] encoded_data;//encoder ����̏o�͂����

integer i,j,flag,m,k,n;

encoder en1(data,encoded_data);

initial begin

//�����̗�

for (i=0;i<16;i=i+1) begin//

data=i[3:0];

#10;

code_array[i]=encoded_data;//�z��Ɋi�[

$display("Code [%d]=%b",i,encoded_data);

end

//CODE�@Word�̃r�b�g�̔C�ӂP�r�b�g��ω������ĕʕ�����Ɉ�v���邩������B

flag=0;

$display("1�r�b�g�G���[���`�F�b�N���Ă��܂��B");

for (i=0;i<16;i=i+1) begin//

work=code_array[i];//����Data��

for ( j=0;j<8;j=j+1) begin

a=work ^ (1 <<j);//1bit�@�G���[���悹��

for (m=0; m<16;m=m+1) begin//���������ꂪ���邩�ǂ������`�F�b�N

if (a==code_array[m]) flag=1;//���������ꂪ����������@�t���OON

end

end

end

if (!flag) $display( "1�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ͂���܂���ł����B�ŏ������́A�P���傫���ł��B\n");

//CODE�@Word�̃r�b�g�̔C�ӂQ�r�b�g��ω������ĕʕ����Ɉ�v���邩������B

flag=0;

$display("2�r�b�g�G���[���`�F�b�N���Ă��܂��B");

for (i=0;i<16;i=i+1) begin//

work=code_array[i];//����Data��

for ( j=0;j<8;j=j+1) begin

a=work ^ (1 <<j);//1bit�@�G���[���悹��

for (k=0;k<8;k=k+1) begin

b=a ^(1<< k);//����1�r�b�g�G���[���悹��

if (work !=b) begin//���������͏�����

for (m=0; m<16;m=m+1) begin//���������ꂪ���邩�ǂ������`�F�b�N

if (b==code_array[m]) flag=1;//���������ꂪ����������@�t���OON

end

end

end

end

end

if (!flag) $display( "2�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ͂���܂���ł����B�ŏ������́A2���傫���ł��B\n");

//CODE�@Word�̃r�b�g�̔C��3�r�b�g��ω������ĕʕ����Ɉ�v���邩������B

flag=0;

$display("3�r�b�g�G���[���`�F�b�N���Ă��܂��B");

for (i=0;i<16;i=i+1) begin//

work=code_array[i];//����Data��

for ( j=0;j<8;j=j+1) begin

a=work ^ (1 <<j);//1bit�@�G���[���悹��

for (k=0;k<8;k=k+1) begin

b=a ^(1<< k);//����1�r�b�g�G���[���悹��

for (n=0;n<8;n=n+1) begin

c=b^(1<<n);//����1�r�b�g�G���[���悹

if (work !=c) begin//����������͏�����

for (m=0; m<16;m=m+1) begin

if (c==code_array[m]) begin//���������ꂪ���邩�ǂ������`�F�b�N

//$display("%b %b",work,c);

flag=1;//���������ꂪ����������@�t���OON

end

end

end

end

end

end

end

if (!flag) $display( "3�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ͂���܂���ł����B�ŏ������́A2���傫���ł��B");

else $display("3�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ�����܂��B�ŏ������́A3�ȉ��ł��B");

end

endmodule

module encoder(input [3:0] in,

output wire [7:0] out);

reg r0,r1,c0,c1;

wire [3:0] y=in[3:0];

assign out[3:0]=in;

assign out[4]=r0;

assign out[5]=r1;

assign out[6]=c0;

assign out[7]=c1;

always @* begin

r0=y[0] ^ y[1];

r1=y[2] ^ y[3];

c0=y[0] ^ y[2];

c1=y[1] ^ y[3];

end

endmodule

���̌��ʂ�����ƁA���̂悤�ɂȂ�܂��B�R�[�h���[�h�O�ƂP�̃n�~���O�����́A3�ɂȂ�܂��B�n�~���O�����Ƃ͂O��1���Ⴄ�Ƃ���̐��ł��B�S�Ă̕�����ł݂��Ƃ��ɁA

�ŏ��ƂȂ�n�~���O�������ŏ������ɂȂ�܂��B�v���O�����ł́A�����f���ɑS���[�h�ɂ��Ď����čŏ����������߂Ă��āA

�^�̍ŏ������́A�R�ł��邱�Ƃ��Ă��܂��B

���̕�����ɉ�����ɂ́A3�r�b�g�̃G���[���K�v�ł��B�����̗��ꂩ�猩��ƁA1�r�b�g�̃G���[�ɂ��ẮA�ǂ���ɋ߂���

�d����ł��e�Ղɔ��f�ł��A2�r�b�g�G���[�ł́A������̉\��������A3�r�b�g�ł́A���̕�����ɉ����Ă��܂��ăG���[�����������Ƃ���A

������Ȃ��A�Ƃ������ƂɂȂ�܂��B�ȏ�́A�ŏ������Ō����ꍇ�ŁA�S�Ă̕����Ԃ̋������R�Ƃ�����ł��Ȃ������Ȃ̂ŁA

���ł́A2�r�b�g�������\�ȏ�ʂ��łĂ��邱�Ƃ����҂ł��邩������Ȃ��Ƃ������Ƃł͂Ȃ����Ǝv���܂��B

�f�W�^���I�Ɍ����̂��A�n�~���O�����ł����A������A�i���O�I�Ɍ����̂����[�N���b�h�����ɂȂ�܂��B����̂悤��AWGN�̌n�ɂ����ẮA��M���[�h�ɂ��āA

�S������Ƃ̃��[�N���b�h���������ߍŏ��ƂȂ镄�����I�яo���A�ł��m���炵�������iMaximum�@likelihood�@Decoding)�ƂȂ邱�Ƃ��m���Ă��܂��B

����̏ꍇ�A�ɒ[�ɕ��������Z���̂ŁA���͂�����ɂ��邩������܂���B

F:\regression_test\ldgm\dwm_test1.v(3)::dwm1_test

Verilog�̃V�~�����[�V�����̏������������܂����B�X�^�[�g��,Go�{�^���������Ă��������B

------------- �V�~�����[�V�������J�n���܂��B--------------------

Code [ 0]=00000000

Code [ 1]=01010001

Code [ 2]=10010010

Code [ 3]=11000011

Code [ 4]=01100100

Code [ 5]=00110101

Code [ 6]=11110110

Code [ 7]=10100111

Code [ 8]=10101000

Code [ 9]=11111001

Code [ 10]=00111010

Code [ 11]=01101011

Code [ 12]=11001100

Code [ 13]=10011101

Code [ 14]=01011110

Code [ 15]=00001111

1�r�b�g�G���[���`�F�b�N���Ă��܂��B

1�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ͂���܂���ł����B�ŏ������́A�P���傫���ł��B

2�r�b�g�G���[���`�F�b�N���Ă��܂��B

2�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ͂���܂���ł����B�ŏ������́A2���傫���ł��B

3�r�b�g�G���[���`�F�b�N���Ă��܂��B

3�r�b�g�G���[�ŁA���̕�����ɂȂ邱�Ƃ�����܂��B�ŏ������́A3�ȉ��ł��B

---------- �V�~�����[�V�������I�����܂��Btime=160----------

�ۑ�̎��g�ݕ��j

�R���e�X�g�̎��g�ݕ��j�́A��̌����Ō��܂�܂����B���肸�ɂ܂��A�Q�킵�Ă݂����Ǝv���܂��B�_���́A

- �X���[�v�b�g�@4Gbps�@�iIterative Decoder�͎g��Ȃ��Ǝ������j

- AWGN�����퓋��->1e8�r�b�g�ł�BER�������i�X�^�[�^�L�b�g�R�j

�ۑ�����������A6�Ђ܂őς���AWGN��IP������������ł��B�@

�n�[�h�Ŕ���������ƂȂ�ƁABox�@Muller�AZiggurat�AWallace�̕��@�̂�����������Ă��Ă������������Z�����邱�ƂɂȂ�̂ŁA

�ʓ|�ł��B����́AYACC�ɁAziggurat�̕��@���\�t�g�Ŏ������邱�Ƃɂ��܂����B�iYACC�̍������Q�Ƃ��������B�j

on the fly �ł́A����܂��A�����I��AWGN���ł���̂ŁA��x���点��A��̓Ԏ��敪�z�܂ŁA�v���O�����Ō����邱�Ƃ��\�ɂȂ�܂��B

BPSK�̐��G���[���[�g��1�r�b�g������H

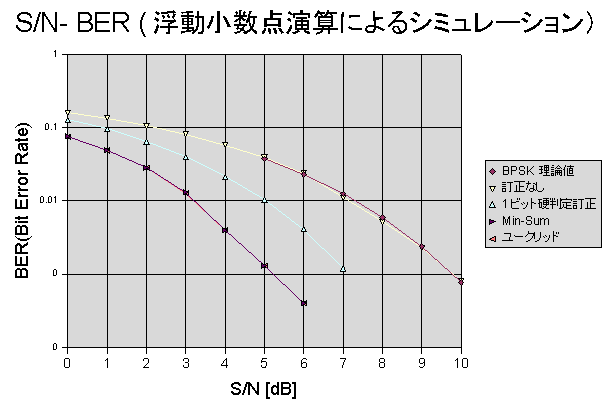

���G���[���[�g�ɑ��āA��̍d���������H�̌��ʂ����Ă݂܂��傤�B

�ۑ�ʂ�A�O��B,3dB,6dB,9dB���܂�AWGN�������A���G���[���[�g�ɑ����r���s���Ă݂܂��B

//Nov.2.2005

//Nov.3.2005

module raw_error_rate;

parameter integer RATE=2;

parameter integer No_Of_Data_Bits=10000;

parameter integer No_Of_Array=No_Of_Data_Bits/4;

parameter integer Total_Bits=No_Of_Data_Bits*RATE;

parameter integer SEED=1;

real expected_sigma;

real noise;

real noise_array[ 0 :Total_Bits-1];

real r_array [0 :Total_Bits-1];

reg [7:0] data_array [0 : No_Of_Array-1];

reg [7:0] decode_array [0 : No_Of_Array-1];

reg [3:0] hard_correction_array [0 : No_Of_Array-1];

initial begin

make_random_data;//10000�̃����_���f�[�^����� ���ʂ�=>data_array�@LSB��4bit

encode_data;//10000�̃p�C�e�B������@���ʂ�=>data_array�@MSB��4bit

add_noise(0.0);//�O��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(3.0);//3��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(5.0);//5��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(6.0);//6��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(7.0);//7��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(8.0);//8.0��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(9.0);//9.0��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

add_noise(10.0);//10.0��B�m�C�Y��������

raw_decode;//�f�R�[�h����

hard_correction;

end

task make_random_data;

integer i;

integer work,counter;

begin

$display("%d�̃����_���f�[�^�����ł��B",No_Of_Data_Bits);

for (i=0;i<No_Of_Array-8; i=i+8) begin//4x8 �r�b�g�����_���f�[�^��

work=$random;

{data_array[i+3][0 +:4],data_array[i+2][ 0 +:4],data_array[i+1][0 +:4],data_array[i+0][0 +:4]}=work[15:0];

{data_array[i+7][0 +:4],data_array[i+6][ 0 +:4],data_array[i+5][0 +:4],data_array[i+4][0 +:4]}=work[31:16];

end

work=$random;

counter=0;

for (i=No_Of_Array-8;i<No_Of_Array; i=i+1) begin//�Ō�́A4�r�b�g�Â�

data_array[i][0 +:4]=work[counter*4 +:4];

counter=counter+1;

end

end

endtask

task encode_data;

integer i;

begin

$display("�p���e�B�����ł��B");

if ( (Total_Bits/RATE)% No_Of_Array)begin//assert(0);

$display(" �v���O�����G���[");

$finish;

end

for (i=0;i<No_Of_Array; i=i+1) begin

data_array[i][4 +:4]=encoder(data_array[i][ 0 +:4]);//�f�[�^��n���ăp���e�B�����

// $display("data=%h parity=%h",data_array[i][0 +:4],data_array[i][4 +:4]);

end

end

endtask

function [3:0] encoder (input [3:0] y);//�p���e�B������

reg r0,r1,c0,c1;

begin

r0=y[0] ^ y[1];

r1=y[2] ^ y[3];

c0=y[0] ^ y[2];

c1=y[1] ^ y[3];

encoder ={c1,c0,r1,r0};

end

endfunction

task make_noise( input real db);//���]��S/N[dB]�����

real sigma2,sigma;

integer seed,i;

real noise;

real noise_sum;

begin

$display("-------------------------------------------------");

$display("�m�C�Y�p���[�@%f[dB] �_���Ő������ł��B",db);

sigma2=$pow(10.0,-db/10.0);//$pow �́AVeritak�@Unique

sigma=$sqrt(sigma2);//$sqrt �́AVeritak�@Unique

seed=0;

noise_sum=0;

for (i=0;i<Total_Bits;i=i+1) begin

noise=$normal_vtak(seed,0.0,sigma);//$normal_vtak�́AVeritak�@Unique�@���ϒl�O�A�Ђ�AWGN��

noise_array[i]=noise;//�m�C�Y�z��Ɏ��[����

noise_sum=noise_sum+noise*noise;

end

$display("�m�C�Y�p���[�@%f[dB]�̐��������܂����B",-10*$log10(noise_sum/Total_Bits));

end

endtask

task add_noise( input real db);//���]��S/N[dB]�����

real sigma2,sigma;

integer counter,i,j;

real noise,RData;

begin

make_noise(db);//���]��S/N�@Noize ��noise_array �Ɏ��[����

$display("�m�C�Y�����Z���ł��B");

counter=0;

for (i=0;i<No_Of_Array; i=i+1) begin

for (j=0;j<8;j=j+1) begin

if (data_array[i][j]==1'b1) RData=$itor(-1);//�f�[�^�P�����|�P.0�ɃG���R�[�h

else RData=$itor(1);//�f�[�^�O�����P.0�ɃG���R�[�h

RData=RData+noise_array[counter];//�v�Z��������AWGN�m�C�Y�����Z����

r_array[counter]=RData;//r_array �Ƀm�C�Y���d��real data ��Save����B

counter=counter+1;

end

end

if ( counter !=Total_Bits) begin//assert(0);

$display(" �v���O�����G���[");

$finish;

end

end

endtask

task raw_decode();

integer i,j;

integer index;

integer error_count;

begin

error_count=0;

index=0;

for (i=0;i<Total_Bits;i=i+8) begin

for (j=0;j<8;j=j+1) begin

if (r_array[i+j]>0) decode_array[index][j]=0;//�p���e�B���܂߃n�[�h�f�R�[�h����

else decode_array[index][j]=1;

if (j<4) begin//�f�[�^���̓r�b�g�G���[���J�E���g����

if (decode_array[index][j] !=data_array[index][j]) error_count=error_count+1;

end

end

index=index+1;

end

$display("�����Ȃ��V�X�e������");

$display("�g�[�^���G���[����%d �G���[���[�g=%e",error_count, $itor(error_count)/No_Of_Data_Bits);

end

endtask

task hard_correction();

reg p0,p1,p2,p3;

reg [3:0] parities;

reg d0,d1,d2,d3;

integer index,error_count,i;

begin

error_count=0;

for (index=0;index<No_Of_Array; index=index+1) begin

{d3,d2,d1,d0}=decode_array[index][3:0];//work

p0=d0 ^ d1 ^ decode_array[index][4];//�p���e�B���v�Z

p1=d2 ^ d3 ^ decode_array[index][5];//�p���e�B���v�Z

p2=d0 ^ d2 ^ decode_array[index][6];//�p���e�B���v�Z

p3=d1 ^ d3 ^ decode_array[index][7];//�p���e�B���v�Z

parities={p3,p2,p1,p0};

hard_correction_array[index][3:0]={d3,d2,d1,d0};

if (parities==4'b0000);//No Error Nothing to Do

else if (parities==4'b0101) hard_correction_array[index][3:0]={d3,d2,d1,~d0};//1bit ����

else if (parities==4'b1001) hard_correction_array[index][3:0]={d3,d2,~d1,d0};//1bit ����

else if (parities==4'b0110) hard_correction_array[index][3:0]={d3,~d2,d1,d0};//1bit ����

else if (parities==4'b1010) hard_correction_array[index][3:0]={~d3,d2,d1,d0};//1bit ����

else ;//parity error or uncorrectable error.

//�G���[�����J�E���g

if (data_array[index][3:0] !=hard_correction_array[index][3:0]) begin//���[�h��r����

for (i=0;i<4;i=i+1) begin//���������G���[�����J�E���g

if (data_array[index][i] !=hard_correction_array[index][i]) error_count=error_count+1;

end

end

end

$display("�n�[�h������H����");

$display("�g�[�^���G���[����%d �G���[���[�g=%e",error_count, $itor(error_count)/No_Of_Data_Bits);

$display("\n");

end

endtask

endmodule

���s���ʂł��B�Ȃ��ABPSK��BER���_�l�́A| S/N | BER |

| �T��B | 3.75e-2 |

| �U��B | 2.29e-2 |

| �V��B | 1.25e-2 |

| �W��B | 5.95e-3 |

| �X��B | 2.39e-3 |

���āA�����̌��ʂ́A�ǂ��ł��傤���H�O���t�ɂ��Ă݂Ȃ��Ɨǂ��킩��܂��ABER�͊m���ɉ������Ă���̂ŁA���ʂ͂����

������ł��傤�B���́A�����Maximum�@Likelihood�@Decoding�����ꍇ�ǂ��Ȃ邩�H�A�ł��B

F:\regression_test\ldgm\raw_error_rate.v(2)::raw_error_rate

Verilog�̃V�~�����[�V�����̏������������܂����B�X�^�[�g��,Go�{�^���������Ă��������B

------------- �V�~�����[�V�������J�n���܂��B--------------------

10000�̃����_���f�[�^�����ł��B

�p���e�B�����ł��B

-------------------------------------------------

�m�C�Y�p���[�@0.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@0.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 1607 �G���[���[�g=1.607000e-001

�n�[�h������H����

�g�[�^���G���[���� 1280 �G���[���[�g=1.280000e-001

-------------------------------------------------

�m�C�Y�p���[�@3.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@3.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 810 �G���[���[�g=8.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 402 �G���[���[�g=4.020000e-002

-------------------------------------------------

�m�C�Y�p���[�@5.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@5.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 393 �G���[���[�g=3.930000e-002

�n�[�h������H����

�g�[�^���G���[���� 104 �G���[���[�g=1.040000e-002

-------------------------------------------------

�m�C�Y�p���[�@6.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@6.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 238 �G���[���[�g=2.380000e-002

�n�[�h������H����

�g�[�^���G���[���� 41 �G���[���[�g=4.100000e-003

-------------------------------------------------

�m�C�Y�p���[�@7.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@7.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 110 �G���[���[�g=1.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 12 �G���[���[�g=1.200000e-003

-------------------------------------------------

�m�C�Y�p���[�@8.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@8.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 52 �G���[���[�g=5.200000e-003

�n�[�h������H����

�g�[�^���G���[���� 2 �G���[���[�g=2.000000e-004

-------------------------------------------------

�m�C�Y�p���[�@9.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@9.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 23 �G���[���[�g=2.300000e-003

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

-------------------------------------------------

�m�C�Y�p���[�@10.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@10.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 8 �G���[���[�g=8.000000e-004

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

---------- �V�~�����[�V�������I�����܂��Btime=0----------

���[�N���b�h�����ɂ�镜���ł��B���hard_correction�^�X�N�ɑΉ����Ă��܂��B

task euclidean_decode();

integer i,j,k,m;

integer index;

integer error_count;

reg [3:0] min_code_word;

reg [7:0] data;

real distance,min_distance;

real bit_distance;

real data_r;

begin

error_count=0;

index=0;

for (i=0;i<Total_Bits;i=i+8) begin

//�����̗�

min_distance=1e5;//Big Value

for (j=0;j<16;j=j+1) begin//�S�R�[�h���[�h�ɂ���

data={encoder(j[3:0]),j[3:0]};//�����̗�

//$display("Code [%d]=%b",j,data);

distance=0.0;

for (k=0;k<8;k=k+1) begin//���[�N���b�h�����ׂ�

data_r=data[k]==1'b1 ? -1.0 : 1.0;//�G���R�[�h

bit_distance=r_array[i+k]- data_r;//�r�b�g���̋���

distance=distance+ bit_distance**2;//�Q�悵�đ���

end

if (distance <min_distance) begin//�������ŏ����H ��r�����Ȃ̂Ń��[�g�͕s�v

min_distance=distance;//������Save

min_code_word=j[3:0];//�R�[�h���[�h���o������

end

end

euclidean_correction_array[index]=min_code_word;

if (min_code_word !==data_array[index][3:0]) begin//�R�[�h���[�h���r����

for (m=0;m<4;m=m+1) begin//���������r�b�g�G���[�����J�E���g

if (data_array[index][m] !=euclidean_correction_array[index][m]) error_count=error_count+1;

end

end

index=index+1;

end

$display("ML�V�X�e������");

$display("�g�[�^���G���[����%d �G���[���[�g=%e",error_count, $itor(error_count)/No_Of_Data_Bits);

end

endtask

���s���ʂł��B�m���ɏ�̍d���������H�����G���[���[�g�����サ�Ă��܂��B���̌��ʂ́A���̕����������̏�E��^���܂��B

�i������ǂ����ʂ͂���܂���B�j�@�R���e�X�g�ł́A�����ɂ��̌��ʂɁA�������ŏ��Q�[�g���ŋ߂Â��邩�A���L�[�|�C���g�ɂȂ�܂��B

F:\regression_test\ldgm\Euclidean_error_rate.v(3)::euclidean_error_rate

Verilog�̃V�~�����[�V�����̏������������܂����B�X�^�[�g��,Go�{�^���������Ă��������B

------------- �V�~�����[�V�������J�n���܂��B--------------------

10000�̃����_���f�[�^�����ł��B

�p���e�B�����ł��B

-------------------------------------------------

�m�C�Y�p���[�@0.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@0.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 1607 �G���[���[�g=1.607000e-001

�n�[�h������H����

�g�[�^���G���[���� 1280 �G���[���[�g=1.280000e-001

ML�V�X�e������

�g�[�^���G���[���� 755 �G���[���[�g=7.550000e-002

-------------------------------------------------

�m�C�Y�p���[�@3.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@3.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 810 �G���[���[�g=8.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 402 �G���[���[�g=4.020000e-002

ML�V�X�e������

�g�[�^���G���[���� 128 �G���[���[�g=1.280000e-002

-------------------------------------------------

�m�C�Y�p���[�@5.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@5.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 393 �G���[���[�g=3.930000e-002

�n�[�h������H����

�g�[�^���G���[���� 104 �G���[���[�g=1.040000e-002

ML�V�X�e������

�g�[�^���G���[���� 13 �G���[���[�g=1.300000e-003

-------------------------------------------------

�m�C�Y�p���[�@6.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@6.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 238 �G���[���[�g=2.380000e-002

�n�[�h������H����

�g�[�^���G���[���� 41 �G���[���[�g=4.100000e-003

ML�V�X�e������

�g�[�^���G���[���� 4 �G���[���[�g=4.000000e-004

-------------------------------------------------

�m�C�Y�p���[�@7.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@7.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 110 �G���[���[�g=1.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 12 �G���[���[�g=1.200000e-003

ML�V�X�e������

�g�[�^���G���[���� 3 �G���[���[�g=3.000000e-004

-------------------------------------------------

�m�C�Y�p���[�@8.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@8.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 52 �G���[���[�g=5.200000e-003

�n�[�h������H����

�g�[�^���G���[���� 2 �G���[���[�g=2.000000e-004

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

-------------------------------------------------

�m�C�Y�p���[�@9.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@9.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 23 �G���[���[�g=2.300000e-003

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

-------------------------------------------------

�m�C�Y�p���[�@10.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@10.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 8 �G���[���[�g=8.000000e-004

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

---------- �V�~�����[�V�������I�����܂��Btime=0----------

���āA���ɉۑ�̕��@�ł����ʂ��r���Ă����܂��傤�B�f���ɁA�Ꭶ�̕��@���R�[�f�B���O���܂��B

task iterative_decoder(input integer iteration,input integer min_sum_flag);//min_sum ��p����ꍇ�́Amin_sum=1�Ƃ���

integer i,j,m;

integer index;

integer iter;

integer error_count;

real y0,y1,y2,y3,r0,r1,c0,c1;

real y0col,y1col,y2col,y3col;

real y0row,y1row,y2row,y3row;

reg d0,d1,d2,d3;

begin

error_count=0;

index=0;

for (i=0;i<Total_Bits;i=i+8) begin

//iterative decoder �̏�����

y0=r_array[i+0];

y1=r_array[i+1];

y2=r_array[i+2];

y3=r_array[i+3];

r0=r_array[i+4];

r1=r_array[i+5];

c0=r_array[i+6];

c1=r_array[i+7];

y0col=0.0;

y1col=0.0;

y2col=0.0;

y3col=0.0;

for (iter=0;iter< iteration;iter=iter+1) begin//interative �f�R�[�f�B���O

//�s�A�O���l�̌v�Z

y0row=func(y1+y1col,r0,min_sum_flag);

y1row=func(y0+y0col,r0,min_sum_flag);

y2row=func(y3+y3col,r1,min_sum_flag);

y3row=func(y2+y2col,r1,min_sum_flag);

//��A�O���l�̌v�Z

y0col=func(y2+y2row,c0,min_sum_flag);

y1col=func(y3+y3row,c1,min_sum_flag);

y2col=func(y0+y0row,c0,min_sum_flag);

y3col=func(y1+y1row,c1,min_sum_flag);

end

//�J��Ԃ����I�������f�R�[�h���`���l���l�{���O�l�{����l

d0=y0+y0row+y0col > 0 ? 0 :1;

d1=y1+y1row+y1col > 0 ? 0: 1;

d2=y2+y2row+y2col > 0 ? 0: 1;

d3=y3+y3row+y3col > 0 ? 0: 1;

iterative_correction_array[index]={d3,d2,d1,d0};

if (iterative_correction_array[index] !==data_array[index][3:0]) begin//�R�[�h���[�h���r����

for (m=0;m<4;m=m+1) begin//���������r�b�g�G���[�����J�E���g

if (data_array[index][m] !=iterative_correction_array[index][m]) error_count=error_count+1;

end

end

index=index+1;

end

if (min_sum_flag) $display("Min-Sum Iterative Decoding Log�V�X�e������ ");

else $display("Log-Sum Iterative Decoding Log�V�X�e������ ");

$display("�g�[�^���G���[����%d �G���[���[�g=%e",error_count, $itor(error_count)/No_Of_Data_Bits);

end

endtask

function real func (input real a, input real b,input integer min_sum_flag);//min_sum ��p����ꍇ�́@min_sum_flag =1�ɐݒ肷��

real den,num;

real sign;

real min;

begin

if (min_sum_flag) begin

sign=a*b > 0 ? 1.0 : -1.0;

min=$fabs(a) > $fabs(b) ? $fabs(b) : $fabs(a);

func=sign* min;

end else begin

num=1.0 +$exp(a+b);

den=$exp(a)+$exp(b);

func=$log(num/den);

end

end

endfunction

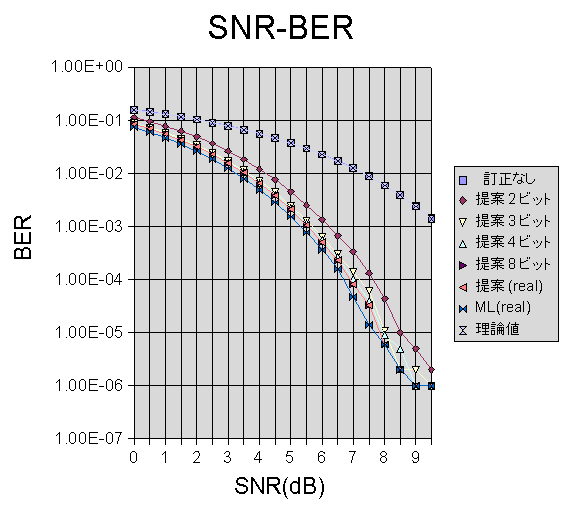

���ʂł��Biteration �́A5��ɂ��܂����B�ӊO�ɂ��A�w��Optimum�Ȍ��ʂɂȂ�܂����B���ۂ̂Ƃ���A2��ł��A�w�LjႢ�́A�Ȃ��悤�Ɏv���܂��B

�ǂ����āA����iterative algorithm���������邩�Ƃ����̂́A���o�I�Ɍ����Ă��s�v�c�ł��ˁB

����ɂ��Ă��A����ȏ�ȒP�����悤�̂Ȃ�LDPC������ɂȂ��Ă���A�ʔ����ۑ�ɂȂ��Ă��܂��B�B

�O���t�����Ă݂܂����BMin-Sum �ƃ��[�N���b�h�́A�s�b�^���d�Ȃ��Ă��܂��Ă��܂��B1e-3�Ō���ƁA

���G���[���[�g�ɑ��āA�T��B�ʂ̃Q�C��������܂��B�������ɂ��ш�m�C�Y�̏㏸�́A2�{�̂R��B�Ȃ̂ŁA��������

����Č�������Q��B�̕����������������邱�ƂɂȂ�܂��B�i�Q��B���M�d�͂𗎂Ƃ��Ă�����BER��������j

F:\regression_test\ldgm\iterative_decoding.v(3)::iterative_decoding

Verilog�̃V�~�����[�V�����̏������������܂����B�X�^�[�g��,Go�{�^���������Ă��������B

------------- �V�~�����[�V�������J�n���܂��B--------------------

10000�̃����_���f�[�^�����ł��B

�p���e�B�����ł��B

-------------------------------------------------

�m�C�Y�p���[�@0.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@0.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 1607 �G���[���[�g=1.607000e-001

�n�[�h������H����

�g�[�^���G���[���� 1280 �G���[���[�g=1.280000e-001

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 765 �G���[���[�g=7.650000e-002

ML�V�X�e������

�g�[�^���G���[���� 755 �G���[���[�g=7.550000e-002

-------------------------------------------------

�m�C�Y�p���[�@1.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@1.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 1345 �G���[���[�g=1.345000e-001

�n�[�h������H����

�g�[�^���G���[���� 969 �G���[���[�g=9.690000e-002

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 494 �G���[���[�g=4.940000e-002

ML�V�X�e������

�g�[�^���G���[���� 489 �G���[���[�g=4.890000e-002

-------------------------------------------------

�m�C�Y�p���[�@2.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@2.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 1061 �G���[���[�g=1.061000e-001

�n�[�h������H����

�g�[�^���G���[���� 645 �G���[���[�g=6.450000e-002

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 283 �G���[���[�g=2.830000e-002

ML�V�X�e������

�g�[�^���G���[���� 282 �G���[���[�g=2.820000e-002

-------------------------------------------------

�m�C�Y�p���[�@3.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@3.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 810 �G���[���[�g=8.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 402 �G���[���[�g=4.020000e-002

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 131 �G���[���[�g=1.310000e-002

ML�V�X�e������

�g�[�^���G���[���� 128 �G���[���[�g=1.280000e-002

-------------------------------------------------

�m�C�Y�p���[�@4.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@4.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 577 �G���[���[�g=5.770000e-002

�n�[�h������H����

�g�[�^���G���[���� 214 �G���[���[�g=2.140000e-002

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 40 �G���[���[�g=4.000000e-003

ML�V�X�e������

�g�[�^���G���[���� 40 �G���[���[�g=4.000000e-003

-------------------------------------------------

�m�C�Y�p���[�@5.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@5.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 393 �G���[���[�g=3.930000e-002

�n�[�h������H����

�g�[�^���G���[���� 104 �G���[���[�g=1.040000e-002

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 13 �G���[���[�g=1.300000e-003

ML�V�X�e������

�g�[�^���G���[���� 13 �G���[���[�g=1.300000e-003

-------------------------------------------------

�m�C�Y�p���[�@6.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@6.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 238 �G���[���[�g=2.380000e-002

�n�[�h������H����

�g�[�^���G���[���� 41 �G���[���[�g=4.100000e-003

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 4 �G���[���[�g=4.000000e-004

ML�V�X�e������

�g�[�^���G���[���� 4 �G���[���[�g=4.000000e-004

-------------------------------------------------

�m�C�Y�p���[�@7.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@7.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 110 �G���[���[�g=1.100000e-002

�n�[�h������H����

�g�[�^���G���[���� 12 �G���[���[�g=1.200000e-003

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 3 �G���[���[�g=3.000000e-004

ML�V�X�e������

�g�[�^���G���[���� 3 �G���[���[�g=3.000000e-004

-------------------------------------------------

�m�C�Y�p���[�@8.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@8.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 52 �G���[���[�g=5.200000e-003

�n�[�h������H����

�g�[�^���G���[���� 2 �G���[���[�g=2.000000e-004

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

-------------------------------------------------

�m�C�Y�p���[�@9.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@9.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 23 �G���[���[�g=2.300000e-003

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

-------------------------------------------------

�m�C�Y�p���[�@10.000000[dB] �_���Ő������ł��B

�m�C�Y�p���[�@10.024707[dB]�̐��������܂����B

�m�C�Y�����Z���ł��B

�����Ȃ��V�X�e������

�g�[�^���G���[���� 8 �G���[���[�g=8.000000e-004

�n�[�h������H����

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

Min-Sum Iterative Decoding Log�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

ML�V�X�e������

�g�[�^���G���[���� 0 �G���[���[�g=0.000000e+000

---------- �V�~�����[�V�������I�����܂��Btime=0----------

���āA�ȏ�ŗ��z�������V�X�e���ł̃��f���̍\�z���ł��܂����B���܂ł́A�_���������ӎ����܂���ł����B���ʂ̖��́A�r�b�g������ɂ��邩�Ƃ������ł��B

����ɂ́A��̃��f����ʎq���r�b�g�����p�����[�^�ɂ��āA�V�~�����[�V�������Ă݂�����ł��ˁB

�ʎq���덷�����荞��ł���̂ŁA��̃V�~�����[�V��������͔������܂���B���z�l��m������ł�

�Q�[�g��/���x�Ƃ̃g���[�h�I�t�ɂȂ�܂��BVersion�@1.83��regresiion_test\ldgm�t�H���_�ɏ�̃R�[�h�͓����Ă��܂��̂ŁA��������A

�X�̃A�C�f�A��W�J���Ă݂�̂��悢��������܂���B

�r�b�g���̌���

�A�[�L�e�N�`�������܂����̂ŁARTL�������āA�r�b�g���̌������s���܂����B

���̒i�K�ł́A���x�ƁA������H�K�́A���\�̃g���[�h�I�t�ɂȂ�̂ŁA�r�b�g�����p�����[�^�ɂ��āA�������s���Ă��܂��B

���̋L�q�́A�n�[�h�E�F�A�g�b�v�̃|�[�g�L�q�ł����A�r�b�g��BW���p�����[�^�ɂ��Ă��܂��BXILINX�ł́A���̃p�����[�^��

�����ƔF�����Ă���āABW�̒l�������邾���ŁA�S�̂̃r�b�g�����ς���Ă���܂��B�r�b�g���̃R�X�g�́A�������Ă݂Ȃ���

�\�z�����Ȃ����Ƃ������A���̎�@�͂����߂ł��B

module hardware # (parameter BW=8)

( input [BW*8-1:0] indata,

output reg [3:0] outdata,

input clock, Reset );

localparam integer FIFO_DEPTH=6;

reg [BW*8-1:0] indataR,indataR_D;

�܂��A����HW�L�q�ł́Averilog-2001��generate ���g���ăp�C�v���C�����W�X�^�������Ă݂܂����BFIFO_DEPTH���p�����[�^�Ƃ��āAHW�ύX�ɑ��ď_��ɂ��Ă��܂��B(Verilog 2001 generate�ɂ��ẮA�����������Q�Ƃ��������B�j

generate

genvar g;

for (g=0;g <FIFO_DEPTH; g=g+1) begin :fifo

reg [3:0] BinDD;

reg [3:0] word0_D;

reg [3:0] word1_D;

reg [3:0] word2_D;

if (g==0) begin :if_label //why xilinx needs label here?

always @(posedge clock) begin

BinDD<=BinD;//2nd

word0_D<=word0[3:0];//2nd

word1_D<=word1[3:0];

word2_D<=word2[3:0];

end

end else begin :else_label//why xilinx needs label here?

always @(posedge clock) begin

BinDD<=fifo[g-1].BinDD;//

word0_D<=fifo[g-1].word0_D;//

word1_D<=fifo[g-1].word1_D;

word2_D<=fifo[g-1].word2_D;

end

end //if

end //for

endgenerate

�Ƃ���ŁA���\�ł����A��Ă��Ă���A�[�L�e�N�`���ł́AML�̗��z�l�ɂ������āA�͔������܂���B�����ł́A0.5��B�ʂɂƂǂ߂����Ǝv���Ă��܂��B���̃V�X�e���V�~�����[�V�����̃O���t����A3�r�b�g�ȏオ�K�v�ł��邱�Ƃ��킩��܂��B�Ȃ��A�����x���`�ŁA�����Ɏg����RTL�ł��V�~�����[�V����

���s���A����̌��ʂł��邱�Ƃ��m�F���܂����B���̃V�~�����[�V�����ł́A�e1e6�r�b�g�����Ă��܂��B�G���[���[�g���Ⴂ�Ƃ���ŁA�o�^���Ă���̂́A���̃G���[�����łȂ��ׂł��B

������̋K�́E���x���A��̑z����ł����̂ŁA����ŁA�R�A���̐v�I���ł��B

�]�k�ł����AXILINX�X�p���^���R��Stratix2�Ƃł́A���W�b�N�̐[�����Ⴂ�܂��B�X�p���^���R�́A�ƂĂ��̂ŁA�[�����W�b�N��

���������ł��܂���B��ꂽ���W�b�N�́A�����x�ቺ�Ƃ����`�Ō���܂��B�ŏ�3�i�ʂŏ����Ă��܂������A70MHz��

�����o�Ȃ��āA�ڂ��^���܂����B���ʁA�ŏI�I��8�i�ɂȂ��Ă��܂��܂����B�����Ă͂��܂��AST2�Ȃ玩�g�̍ō����x��ۂ����܂܁A3-4�i�Ŏ��܂�悤�ȋC�����܂��B

=>�������ɍő��f�o�C�X�iST2�j���g���Ƒ������ʂɂȂ�܂����B

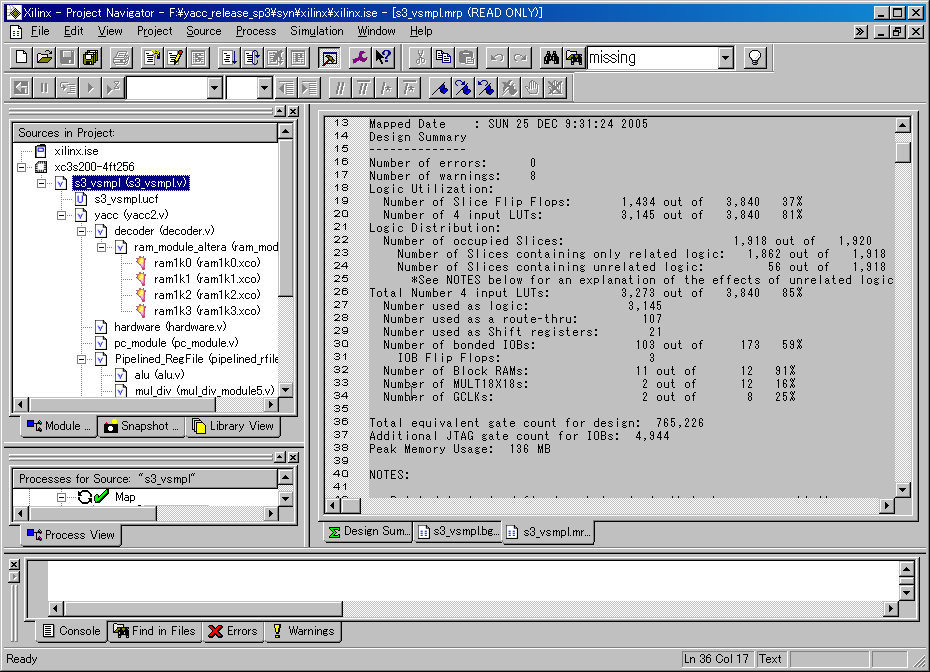

| �����\�t�g/�f�o�C�X | �����Ώ� | LUT�� | �x��(ns) | ���g���iMH���j | LUT���� | ���x�� | �]�����[�g(Gbps) |

| Quartus�T�D�P/ | ���t�@�����X��H | 14 | 10.57 | 94.60 | 1 | 1 | |

| EP2S15F484C3 | hardware.v | 309 | 2.11 | 473.26 | 22.07 | 5.003 | 3.79 |

| ISE7.1/ | ���t�@�����X��H | 17 | 12.73 | 78.57 | 1 | 1 | |

| XC3S200-4 | hardware.v | 291 | 5.37 | 186.22 | 17.12 | 2.370 | 1.49 |

�x���V�~�����[�V����

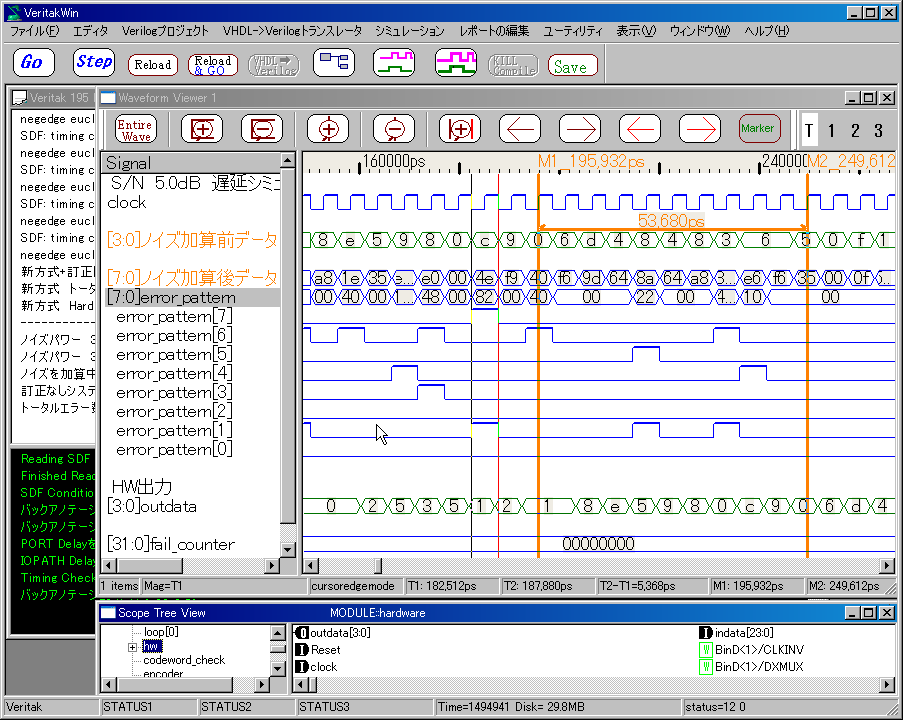

�@�v�����R�A�̒x���V�~�����[�V�������s���Ă݂܂����BRTL��́A9�N���b�N�x���Ȃ̂ł����A�o�͂̒x��(��7ns)�̂��߁A10�N���b�N�x���ɂȂ��Ă��܂��Ă��܂��B

�܂��A���ŁA1�r�b�g�Ȃ����A2�r�b�g�̃G���[�p�^�[�����������Ă��܂����A�������s���ăm�C�Y���Z�O�̃f�[�^���Č����Ă��邱�Ƃ�������܂��B

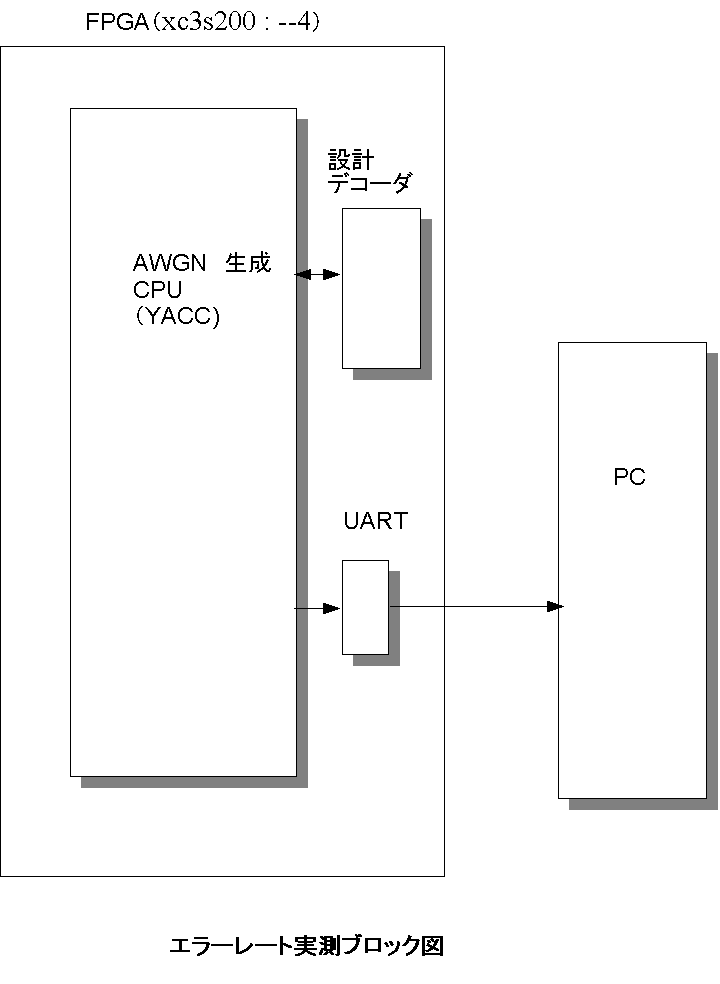

YACC�Ƃ̌���

YACC�̃�������ɃR�A���}�b�v���A������H���쐬���܂��B

3E�́A�҂��Ă����Ȃ��̂ŁA�X�p���^���R�̃X�^�[�^�L�b�g��ō쐬���܂����B���ʁAC�v���O�����̃_�C�G�b�g��]�V�Ȃ�����܂����B

Area�D��ŁA�x����25ns�������Ă��܂��B

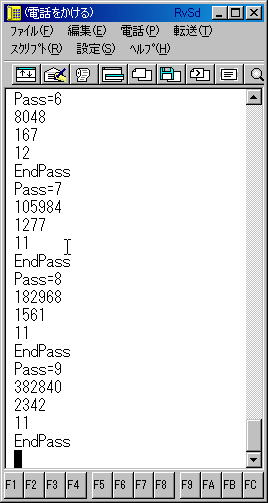

��́A���̂悤�ȁAC�v���O�������Ђ����瑖�点�AUART�ŁA�G���[���[�g�̕��i�Q�āj�҂ĂA�悢�����ł��B

double target_sds[]={ 1.0, //0db PASS0

0.891,//1db 1

0.794,//2db 2

0.708,//3db 3

0.631,//4db 4

0.562,//5dB 5

0.501,//6dB 6

0.447,//7 7

0.422,//7.5 8

0.398,//8.0 9

0.376,//8.5 10

0.355,//9 11

0.335,//9.5 12

0.315// 10.0 13

};

void main()

{

double sum,avg,a,target_sd;

double noise;

int i,j,index,I;

unsigned data_in,data_out;

int n=No;

#ifdef RTL_SIM

print_uart("V1.1\n");

#endif

total_bits=0;

sum=0;

// for (i=0;i< (STATISTICS_LEVELS*2);i++) counter_array[i]=0;

for(j=0;j< 14 ;j++) {

target_sd=target_sds[j];

bit_counter=0;

bit_error_counter=0;

raw_bit_error_counter=0;

do{

data_in=make_input_data(target_sd);

#ifndef DOS

data_write_and_compare(data_in);

#endif

bit_counter +=4;

total_bits +=4;

if (bit_error_counter> ERROR_THRESHOLD){

print_uart("Pass=");

print_num(j);

print_num(bit_counter);

print_num(raw_bit_error_counter);

print_num(bit_error_counter);

print_uart("EndPass\n");

break;

}

}while(1);

}

#ifdef DOS

#ifdef SD_DISPLAY

avg=sum/No;

sum=0;

for (i=0;i<No;i=i+1){

a=array[i]-avg;

sum=sum+a*a;

}

sd=sqrt(sum/No);

printf("Done %d samples. avg=%f target_sd=%f sd=%f",n,avg,target_sd,sd);

#endif

printf("Done %d samples. target_sd=%f\n",n,target_sd);

for (i=0;i< (STATISTICS_LEVELS*2);i++){

printf("%d,%d\n",i-STATISTICS_LEVELS,counter_array[i]);

}

#else

print_uart("Done All\n");

#endif

}

��������

AWGN�̐����Ɏ��Ԃ��������Ă���̂ŁA������݂̃r�b�g���́A������ʂƂȂ�܂������A����ł��AH/W��

�쐬�����Ԃ��l����ƁA�����I�ȑË��_�ł͂Ȃ����Ǝv���܂��B��y��C�v���O����������CPU������ƁA

����H/W�̌����y�ɂȂ邱�Ƃ��A�������܂����B

�@����AC�v���O�����̃f�o�b�O��Veritak��ōs���܂������AAWGN�̐����́A���Ԃ�������̂Ō��\�Ȏ��Ԃ�������܂����B

�\�t�g�E�F�A�V�~�����[�^�ł́A�����ɑ��点�邱�Ƃ��ł��܂����A����H/W�́A�Ǝ��Ȃ̂ŁA��͂�RTL�ł̍��������]�܂����Ǝv���܂����B

�܂��A�V�X�e���̌����ł́ARTL�͂��̂܂܂ŁA����ȊO��VPI���g����C�Ăяo���ō쐬���Ă��悩������������܂���B

�����A���Ԃ�����̂ŁA���̓_�ł̌��������Ă݂����Ǝv���܂��B

�Ȃ��A����́A�����̃G���W�j�A���̗ǎ��Ƃ̋���ł��B

����

��VPI���g��������RTL�V�~�����[�V������

H/W�̋L�q�ȊO�̎��ӂ�C�ŋL�q���āARTL�V�~�����[�V���������������܂����B

���ꂾ�ƁA���r�b�g��1e9�̃e�X�g�ł��A����قǎ��Ԃ́A������܂���B��̃X�p���^���R�ł̃e�X�g�����A

���Ȃ葬���ł��B���@CPU�̕�����Ȃ��Ȃ��Ă��܂��B�i�Ȃɂ��A�\�t�g�t���[�g25MHz�쓮�ł��̂ŁB�j

H/W���́A�����Ɏg�p�����\�[�X�ł����AAWGN�̃v���O�����������Ȃ̂ŁA���@�Ɠ������ʂɂȂ�͂��ł��B

�ȉ��e�X�g�x���`�ł��B

//RTL VPI��p����������

`timescale 1ns/1ps

`define CYCLE 10

module euclidean_error_rate;

parameter integer ERROR_LIMIT=1000;//�G���[���@��������玟��DB�@STEP�ɍs��

parameter integer BW=3;//�r�b�g��

parameter integer FIFO_DEPTH=9;//�n�[�h�E�F�A�̒x���҂�

reg clock=0;

reg [31:0] VPI_Data;//VPI�ŕԂ����l

wire [23:0] indata=VPI_Data[23:0];//�n�[�h�E�F�A����3�r�b�g���W�r�b�g

wire [3:0] correct_data=VPI_Data[27:24];//���Ғl

wire [3:0] outdata;//�n�[�h�E�F�A�o��

reg Reset=1;

reg [63:0] bit_counter=0;

integer bit_error_counter=0;

real DB;

real sigma;

initial begin

#100;

Reset=0;

DB=0.0;

set_sigma;

end

generate

genvar gen;

for (gen=0;gen<FIFO_DEPTH;gen=gen+1) begin :loop

reg [4:0] D;

if (gen==0) begin

always @(posedge clock) begin

D<={Reset,correct_data};

end

end else if(gen==FIFO_DEPTH-1) begin//�n�[�h�E�F�A�̒x���N���b�N���A���Ғl���x��������

always @(posedge clock) begin

D<=loop[gen-1].D;

@(negedge clock);

if (D[4]==0 ) begin//RESET ��LOW�̂Ƃ������J�E���g����

bit_counter=bit_counter+4;

count_bit_error(D[3:0],outdata);//�G���[���̃J�E���g�@D[3:0]�́A���Ғl

end

end

end else begin

always @(posedge clock) begin

D<=loop[gen-1].D;

end

end

end

endgenerate

task count_bit_error( input [3:0] in1,in2) ;

integer i;

real rate;

begin

if ( in1 !==in2) begin

for (i=0;i<4;i=i+1) begin

if (in1[i] !==in2[i]) bit_error_counter=bit_error_counter+1;

end

end

if (bit_error_counter >ERROR_LIMIT) begin//�G���[����LIMIT���������玟��DB�@STEP

rate=bit_error_counter;

rate=rate/bit_counter;

$display("DB=%f bits=%d error=%d error_rate=%e sigma=%f",DB,bit_counter,bit_error_counter,rate,sigma);

DB=DB+0.5;

bit_counter=0;

bit_error_counter=0;

set_sigma;

end

end

endtask

task set_sigma;

real sigma2;

begin

sigma2=$pow(10.0,-DB/10.0);//

sigma=$sqrt(sigma2);//$sqrt

end

endtask

always @(negedge clock) begin

#1;

if (Reset) ;

else begin

VPI_Data=$my_random_for_dwm(sigma);//DWM �p�@VPI

end

end

always #(`CYCLE) clock=~clock;

hardware # ( .BW(BW)) hw ( .indata(indata), .outdata(outdata), .clock(clock), .Reset(Reset) );

endmodule

VPI�\�[�X�ł��B

static int sys_my_random_for_dwm_size_tf()//Aug.42003

{

return 32;

}

/* position of right-most step */

#define PARAM_R 2.96454468156

/* level values */

static const double ytab[32] = {

1,

0.907475617638,

0.8387295158,

0.780775785072,

0.729446868113,

0.682776316768,

0.639647716015,

0.599353201849,

0.561409662765,

0.525469625896,

0.491273228111,

0.458620229136,

0.427352696597,

0.397343775955,

0.368490127285,

0.340706676394,

0.313922886649,

0.288080067698,

0.263129417761,

0.23903060658,

0.215750777731,

0.193263899438,

0.171550433862,

0.150597335281,

0.130398439093,

0.110955385052,

0.0922793705114,

0.0743943543072,

0.0573431209268,

0.0411998625242,

0.0261009770388,

0.0123479825627,

};

/* quick acceptance check */

static const unsigned long ktab[32] = {

0,

12465559,

14143380,

14859376,

15254596,

15503949,

15674743,

15798352,

15891342,

15963265,

16020003,

16065358,

16101882,

16131333,

16154939,

16173564,

16187797,

16198017,

16204425,

16207053,

16205755,

16200181,

16189707,

16173323,

16149413,

16115345,

16066638,

15995077,

15883832,

15691829,

15281721,

15063248

};

/* quick value conversion */

static const double wtab[32] = {

2.6265107239e-08,

3.5349827263e-08,

4.19328107856e-08,

4.73449074891e-08,

5.20705831605e-08,

5.63468970139e-08,

6.03100167664e-08,

6.40468149156e-08,

6.76171489147e-08,

7.10648776583e-08,

7.44238783956e-08,

7.77216053723e-08,

8.09813473119e-08,

8.42237615336e-08,

8.74679979284e-08,

9.0732597892e-08,

9.4036290297e-08,

9.73987784303e-08,

1.00841606117e-07,

1.04389204949e-07,

1.08070261837e-07,

1.11919620405e-07,

1.15981071511e-07,

1.20311664676e-07,

1.24988739931e-07,

1.30122131768e-07,

1.35877026736e-07,

1.42521234138e-07,

1.50537318078e-07,

1.60949814958e-07,

1.76700632665e-07,

1.96806467179e-07

};

unsigned long s1=0xffffffff,s2=0xffffffff,s3=0xffffffff;

unsigned long taus88_int ()

{/*Generates numbers between 0 and 1.*/

unsigned b;

b =(((s1 <<13)^s1)>>19);

s1 =(((s1 &4294967294)<<12)^b);

b =(((s2 <<2)^s2)>>25);

s2 =(((s2 &4294967288)<<4)^b);

b =(((s3 <<3)^s3)>>11);

s3 =(((s3 &4294967280)<<17)^b);

return ((s1 ^s2 ^s3));

}

double taus88 ()

{

return (taus88_int()*2.3283064365e-10);

}

double

gsl_ran_gaussian_ziggurat ()

{

unsigned long U, sign, i, j;

double x, y;

while (1) {

U = taus88_int();

i = U & 0x0000001F; /* 7 bit to choose the step */

sign = U & 0x00000020; /* 1 bit for the sign */

j = U>>6; /* 24 bit for the x-value */

x = j*wtab[i];

if (j < ktab[i]) break;

if (i<32) {

double y0, y1;

y0 = ytab[i];

y1 = ytab[i+1];

y = y1+(y0-y1)*taus88();

} else {

x = PARAM_R - log(1.0-taus88())/PARAM_R;

y = exp(-PARAM_R*(x-0.5*PARAM_R))*taus88();

}

if (y < exp(-0.5*x*x)) break;

}

return sign ? x : -x;

}

unsigned quantize(double rvalue)

{

double R;

int qdata;

R=rvalue*1;

if (R>=1.5) qdata=3;

else if (R>=1.0) qdata=2;

else if (R>=0.5) qdata=1;

else if (R>=0) qdata=0;

else if (R>=-0.5) qdata=-1;

else if (R>=-1.0) qdata=-2;

else if (R>=-1.5) qdata=-3;

else qdata=-4;

qdata &=0x7;//3bit ��o��

return qdata;

}

unsigned get_random_data()

{

unsigned y;

unsigned r0,r1,c0,c1;

unsigned y0,y1,y2,y3;

unsigned outdata;

y=taus88_int();//�����_���f�[�^��B����4�r�b�g�����g���Ă��Ȃ�

//�r�b�g��o��

y0=y & 0x01;

y1=(y >> 1) & 0x01;

y2=(y >> 2) & 0x01;

y3=(y >> 3) & 0x01;

//�p���e�B�v�Z

r0=y0 ^ y1;

r1=y2 ^ y3;

c0=y0 ^ y2;

c1=y1 ^ y3;

outdata=y0;

outdata |=y1 <<1;

outdata |=y2 <<2;

outdata |=y3 <<3;

outdata |=r0 <<4;

outdata |=r1 <<5;

outdata |=c0 <<6;

outdata |=c1 <<7;

outdata <<=24;// ���8�r�b�g�������O�m�C�Y���Z�O�G���R�[�h�f�[�^

return outdata;

}

unsigned make_input_data(double target_sd)

{

double rvalue;

unsigned temp;

unsigned i,j;

double noise;

unsigned outdata;

unsigned word;

outdata=get_random_data();//�G���R�[�_���8�r�b�g�ɃG���R�[�h�f�[�^

//3�r�b�g�A�i���O��M�l�̍쐬

for (i=0;i<8 ;i++) {

noise=gsl_ran_gaussian_ziggurat();//1.0 �K�E�X�m�C�Y����

#ifdef STATISTICS

statistics(noise);//�K�E�X�m�C�Y�̓x�����z����

#endif

noise *=target_sd;//�m�C�Y�V�O�}��Z

if ( (outdata >> (24+i)) & 0x01) {

rvalue=-1.0;//1-> -1��

}else rvalue=+1.0;//0-> +1�ɃG���R�[�h

rvalue +=noise;

temp=quantize(rvalue);//3�r�b�g�ɗʎq��

temp <<=3*i;

outdata |=temp;

}

return outdata;

}

static int sys_my_random_for_dwm(char* name)

{

vpiHandle systfref,argsiter,argh;

t_vpi_value value;

double r;

systfref = vpi_handle(vpiSysTfCall, NULL); /* get system function that invoked C routine */

argsiter = vpi_iterate(vpiArgument, systfref);/* get iterator (list) of passed arguments */

argh = vpi_scan(argsiter);/* get the one argument - add loop for more args */

if(!argh){

vpi_printf("$VPI missing parameter.\n");

return 0;

}

value.format = vpiRealVal;

�@�@vpi_get_value(argh, &value);

�@�@r = value.value.real;

value.value.integer =make_input_data(r) ;

value.format = vpiIntVal;/* return the result */

vpi_put_value(systfref, &value, NULL, vpiNoDelay);

vpi_free_object(argsiter);

return(0);

}

extern "C" void sys_math_vpi_register()//VPI�@DLL���[�h��CALL����A��Function���o�^�����B

{

s_vpi_systf_data tf_data;

//Dec.30.2005 FOR DWM

tf_data.type = vpiSysFunc;//Define as function

tf_data.subtype =vpiIntFunc;//return by integer

tf_data.tfname = "$my_random_for_dwm";

tf_data.user_data = "$my_random_for_dwm";

tf_data.calltf = sys_my_random_for_dwm;

tf_data.compiletf = 0;

tf_data.sizetf = sys_my_random_for_dwm_size_tf;//func �Ȃ̂ŕԂ�

vpi_register_systf(&tf_data);

}

RTL�V�~�����[�^�ŁAC�̃f�o�b�O������Ȃ�āA�M�҂��炢�ł��傤���B�ŏI�I�Ȍ��ʂł��B9/9.5dB�̎����ŁARTL�V�~�����[�V�����l�ƈ�v���Ă��Ȃ��̂́A����2�_�����A�G���[�����P�O�Ŏ~�߂Ă��邽�߂Ǝv���܂��B

���̃f�[�^�́A���ׂ�1000�ȏ�̃G���[���ł����ARTL�V�~�����[�V�����l�Ƃ悭��v���Ă��܂��B�ǂ����ĂP�O�Ŏ~�߂Ă��邩�Ƃ����ƁA���Ԃ��Ȃ���������ł��B

1.3e8�r�b�g���e�X�g����̂ɁA1�T�Ԉȏ�܂����B���̃f�[�^9.0db�ł́A�����炭3�T�Ԃ͂������Ă��܂��ł��傤�B

��������AWGN���{���ɃK�E�X���z���Ă���̂������ׂ܂����B�J�C���挟��ō��i�ł��B

��o�������|�[�g�ł��B

�V�X�e���̌�������o�b�N�A�m�e�[�V������̒x���V�~�����[�V�����܂ŁA�P��̌���Verilog�@HDL��Ō������s���܂����B

����Ȃ�������A���x�I�Ƀl�b�N�̕����́AC/C++�ŋL�q���āAVerilog�@HDL�ŌĂяo���Ă��܂��悢�̂ł��B

�A

�e�X�g�x���`���V�X�e���̌�������x���V�~�����[�V�����܂ŁA�ς��Ȃ��������Ƃɂ��C�Â��ł��傤���H���̎���HDL���g��

�����Ƃ��傫�ȓ_���ƕM�҂͎v���܂��B�m����H/W�́A���ۂ����̂ցA���Ȃ킿�A���f��->RTL->�Q�[�g�[���x�����Q�[�g�ɕω����܂������A�e�X�g�x���`�́A�V�X�e����

�g�������̂����̂܂g�p���Ă��܂��B�������A���̋L�q�́ASystemVerilog�ɂȂ��Ă��ύX�̕K�v�͂���܂���B

20�N���O�ɐv���ꂽ���ꂪ�A���̊�{�@�\�͂��̂܂܂ɁA�����Ȃ��Ƃ��A����10�N�ԁA����������̂́A���������Ƃ��Ǝv���܂��B

�@

LDPC��Verilog�@HDL�L�q

�R���e�X�g�ۑ�́ALDGM�̓����ł��B���������Ɉ��܂����ALDPC��Verilog�R�[�f�B���O��́AOpencores���܂߂Ă܂Ƃ܂������̂́A

���J����Ă��Ȃ��悤�Ȃ̂ŁA�����ŋL�q���Ă݂悤���Ǝv���܂��B

�K���AMATLAB��C�ł̗�́A���\����܂��̂ŁA������|�[�g���Ă��������Ǝv���܂��B

T.B.C.

Verilog �ʼn摜�����H�iVersion�@1.74A/3.24A)

Note:�ȉ��́AVeritak�g���I�v�V������Enable�ɂ���8�r�b�g�P�ʂŏ����Ă��܂��B�����Enable���Ȃ��ƁAVerilog-2001�̋K�i�ł́A%u�́A32�r�b�g�P�ʂōs���Ƃ����K�肪����AC����̃C���[�W�����̂܂܈ڐA�����ȉ��̃\�[�X�͐��������삵�܂���B

3.24A����A�����$fwrite��%c���g���܂����A�o�C�i��0�������Ă���(20)�ɂ��Ă��܂��V�~�����[�^������V�~�����[�^�Ԃ������̍���������悤�ł��B�܂��AVeritak�ł́A1�o�C�g���C�g�p��fputc���g�p�ł��܂����A����́AStandard�iLRM)�ł͂���܂���B

Verilog�@2001�ŃT�|�[�g���ꂽ�A�������z��ƃo�C�i���t�@�C���������V�X�e���^�X�N�̗�ł��B

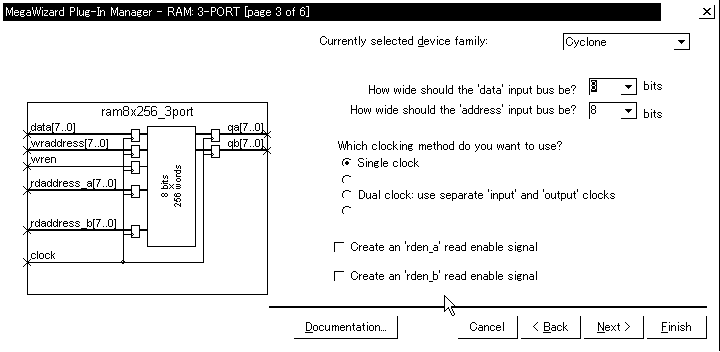

���̗�ł́A24�r�b�g��BMP�t�@�C��(3port.bmp)���o�C�i���œǂݍ���ŁA

�Z�W�����摜(after_abc2.bmp)�ƁA2�l���摜(after_abc3.bmp)�ɂ��Ă��܂��B

���x�����߂�ꍇ�́AC��VPI�������������悢�̂́A�����܂ł�����܂���B

�o�C�i���̃��C�g���s���ɂ́A$fwrite(�h%u�h�A�����j�A������%u�́A�����o�C�i��2�i�̃t�H�[�}�b�g�w���ɂȂ�܂��B�ʏ�A

Verilog�@HDL�ł́A4�l�Ȃ̂Ń�������ł͕���2�r�b�g�ɃA�T�C������Ă��܂����A�����ł́A�����I��1�r�b�g�ɑΉ����܂��B

�܂��A���ӓ_�Ƃ��āA�o�C�i����R/W����ꍇ�́A

$fopen�́A�e�L�X�g���[�h�ł͂Ȃ��A�o�C�i�����[�h�ŊJ���Ȃ��Ă͂����܂���B�i�M�҂��ŏ��e�L�X�g���[�h�ŊJ����

���܂��āA�ςȌ��ʂɔY��ł��܂��܂����B�j�@�@�܂��A�o�C�i�����[�h���s���ɂ́A$fread���g���܂��B

���ϊ�(after_abc1.bmp)

�Z�W�����摜(after_abc2.bmp)

2�l���摜(after_abc3.bmp)

//�Q�l�ɂ���C�\�[�X�́A

//http://www.fit.ac.jp/elec/7_online/lu/sample/bmp_image_proc.cpp

//�ł��B

`define Y_SIZE 2048 // �����ł���ő�摜

`define X_SIZE 2048

`define HIGH 255 //�@�摜�̍ő勭�x�l

`define LOW 0 //�@�摜�̍ŏ����x�l

`define LEVEL 256 //�@�摜�̋��x���x���l

module bmp_test;

parameter read_filename="3port.bmp";

parameter write_filename1="after_abc1.bmp";

parameter write_filename2="after_abc2.bmp";

parameter write_filename3="after_abc3.bmp";

parameter [7:0] INTENSITY=100;//0-255

integer biCompression,

biSizeImage,

biXPelsPerMeter,

biYPelsPerMeter,

biClrUsed,

biClrImportant;

reg [15:0] bfType;

integer bfSize;

reg [15:0] bfReserved1, bfReserved2;

integer bfOffBits;

integer biSize, biWidth, biHeight;

reg [15:0] biPlanes, biBitCount;

reg [7:0] image_in [0:`Y_SIZE][0:`X_SIZE][0:2]; // ���̓J���[�摜�z��

reg [7:0] image_out [0:`Y_SIZE][0:`X_SIZE][0:2]; //�o�̓J���[�摜�z��

reg [7:0] image_bw [0:`Y_SIZE][0:`X_SIZE]; //�Z�W�摜�z��

//********************************************

// 24Bit�r�b�g�}�b�v�t�@�C���ǂݍ��� *

//********************************************

task readBMP(input [128*8:1] read_filename);

integer fp;

integer i, j, k;

reg [7:0] byte;

begin

// �t�@�C���I�[�v��

fp = $fopen(read_filename, "rb") ;//must be binary read mode

if (!fp) begin

$display("readBmp: Open error!\n");

$finish;

end

$display("input file : %s\n", read_filename);

// �w�b�_�[���ǂݍ���

$fread(bfType, fp);

$fread(bfSize, fp);

$fread(bfReserved1, fp);

$fread(bfReserved2, fp);

$fread(bfOffBits, fp);

$fread(biSize, fp);

$fread(biWidth, fp);

if (biWidth%4) begin

$display("Sorry, biWidth%4 must be zero in this program. Found =%d",biWidth);

$finish;

end

$fread(biHeight, fp);

$fread(biPlanes, fp);

$fread(biBitCount, fp);

if (biBitCount !=24) begin

$display("Sorry, biBitCount must be 24 in this program. Found=%d",biBitCount);

$finish;

end

$fread(biCompression, fp);

$fread(biSizeImage, fp);

$fread(biXPelsPerMeter, fp);

$fread(biYPelsPerMeter, fp);

$fread(biClrUsed, fp);

$fread(biClrImportant, fp);

// RGB�摜�f�[�^�ǂݍ���

for (i=0; i< biHeight; i=i+1) begin

for (j=0; j< biWidth; j=j+1) begin

for (k=0; k<3; k=k+1) begin

$fread(byte,fp);

image_in[biHeight-i][j][2-k]=byte;

end

end

end

$display("Current POS=%d",$ftell(fp));

$fclose(fp);

end

endtask

//******************************************************

// 24�r�b�g-�r�b�g�}�b�v�f�[�^��BMP�t�@�C���ɏo�� *

//******************************************************

task writeBMP(input [128*8:1] write_filename,input O);

integer fp;

integer i, j, k;

begin

// �t�@�C���I�[�v��

fp = $fopen(write_filename, "wb");//must be binary read mode

if (!fp) begin

$display("writeBmp: Open error!\n");

$finish;

end

$display("output file : %s\n", write_filename);

// �w�b�_�[���

$fwrite(fp,"%u",bfType);

$fwrite(fp,"%u",bfSize);

$fwrite(fp,"%u",bfReserved1);

$fwrite(fp,"%u",bfReserved2);

$fwrite(fp,"%u",bfOffBits);

$fwrite(fp,"%u",biSize);

$fwrite(fp,"%u",biWidth);

$fwrite(fp,"%u",biHeight);

$fwrite(fp,"%u",biPlanes);

$fwrite(fp,"%u",biBitCount);

$fwrite(fp,"%u",biCompression);

$fwrite(fp,"%u",biSizeImage);

$fwrite(fp,"%u",biXPelsPerMeter);

$fwrite(fp,"%u",biYPelsPerMeter);

$fwrite(fp,"%u",biClrUsed);

$fwrite(fp,"%u",biClrImportant);

// �r�b�g�}�b�v�f�[�^

for (i=0; i< biHeight; i=i+1) begin

for (j=0; j< biWidth; j=j+1) begin

for (k=0; k<3; k=k+1) begin

if (O) $fwrite(fp,"%u",image_out[biHeight-i][j][2-k]);

else $fwrite(fp,"%u",image_in[biHeight-i][j][2-k]);

end

end

end

$display("Current WPOS=%d",$ftell(fp));

$fclose(fp);

end

endtask

//**********************************************

// �q�f�a�J���[�摜��256�~�������Z�W�摜�֕ϊ� *

//**********************************************

task BMPto256BW;

integer y, x, a;

begin

for (y=0; y<biHeight; y=y+1) begin

for (x=0; x<biWidth; x=x+1) begin

a =$rtoi(0.3*image_in[y][x][0] + 0.59*image_in[y][x][1] + 0.11*image_in[y][x][2]);

if (a<`LOW) a = `LOW;

if (a>`HIGH) a = `HIGH;

image_bw[y][x] = a;

end

end

end

endtask

//****************************************

// �����摜��24bit�r�b�g�}�b�v�`���ɕϊ� *

//****************************************

task BWto24BMP;

integer y, x, a;

begin

for (y=0; y<biHeight; y=y+1) begin

for (x=0; x<biWidth; x=x+1) begin

a = image_bw[y][x];

image_out[y][x][0] = a;

image_out[y][x][1] = a;

image_out[y][x][2] = a;

end

end

end

endtask

//****************************************

// �����摜�̂Q�l�� *

//****************************************

task toBinary( input [7:0] intensity);

integer y, x;

begin

for (y=0; y<biHeight; y=y+1)begin

for (x=0; x<biWidth; x=x+1) begin

if(image_bw[y][x] >= intensity) image_bw[y][x]=`HIGH;

else image_bw[y][x] = `LOW;

end

end

end

endtask

initial begin

//�摜����1�F

readBMP(read_filename); // �摜�̓���,RGB24�r�b�g�J���[BMP�摜��z��Ɋi�[

writeBMP(write_filename1,0);//���ϊ��ŏ�������

//�摜�����Q�F�����ϊ�

BMPto256BW; // �q�f�a�J���[�摜�𔒍��摜�ɕϊ�

BWto24BMP; //�@�P�`�����l�������摜���R�`�����l���a�l�o�W���t�H�[�}�b�g�֕ϊ�

writeBMP(write_filename2,1); // �����摜�o��

//�摜�����R�F 2�l��

toBinary(INTENSITY);

BWto24BMP;

writeBMP(write_filename3,1); // �����摜�o��

end

endmodule

|

Verilog �Ńe�L�X�g�t�@�C�������H�iVersion�@1.74A)

��̗�́A�o�C�i���t�@�C����������ł������A�e�L�X�g�t�@�C���������s�����Ƃ��ł��܂��B

�e�X�g�x���`�Ō��ʂ̑Ó������`�F�b�N����p�r�Ƃ��ċ@��͑����̂ł͂Ȃ��ł��傤���H�@

�e�L�X�g�t�@�C�������ɂ́A$fseek,$fscanf,$fdisplay,$fell�����g���܂��B�w��C���̂܂܂ł��ˁB

���́A256MB�̃e�L�X�g�t�@�C�����쐬���āA$fseek��$random�ɔ�сA��������ł���Data�̑Ó������`�F�b�N���Ă��܂��B

�Ȃ��A$random�́A�����t�ŕԂ��̂ŁA$unsigned�������́A�o�p�ŁA�����Ȃ��ɂ��܂��B

//Sep.21.2005

//$fseek/$fscanf/$fdisplay Test

module large_file;

parameter integer WORDS=1024*1024*8;//1024*1024*34 BYTES;

parameter integer STR_LEN=32+2;//CR+LF

integer i;

integer fp;

integer offset;

reg [255:0] R2;

initial begin

//Open

fp=$fopen("large_file.txt","w+");//Open By Write & Read Mode

if (!fp) begin

$display("File Can not be opend.!");

$finish;

end

//Write

$display("Writing Large File..");

for (i=0; i<WORDS;i=i+1) begin

R2={i+7,i+6,i+5,i+4,i+3,i+2,i+1,i};

if (i%10000==1) $display("%d",i);

$fdisplay(fp,"%32x",R2[127:0]);

end

$display("Large Text File genrated Words=%d Total %fMBytes",WORDS,(WORDS*STR_LEN)/1e6);

//Trival Check

trival_check(fp);

//Random Check

random_check(fp);

end

task disp_current_position(input integer fp);

integer position;

begin

position=$ftell(fp);

$display("Current Posion=%d",position);

end

endtask

task trival_check(input integer fp);

parameter OFFSET=10;

begin

$display("Trival Check Starts...");

offset=$ftell(fp);

disp_current_position(fp);

offset=offset-OFFSET*STR_LEN;

$fseek(fp, offset,0);

disp_current_position(fp);

for (i=0;i<OFFSET;i=i+1) begin

$fscanf(fp,"%h\n",R2);

$display("%h",R2);

end

$display("Trival Check Done.\n");

end

endtask

task random_check(input integer fp);

integer EOF;

parameter integer No_of_Checks=1000_000;

integer i,position,aligned_pos,word_pos;

reg [127:0] word;

begin

$display("Random Check.Starts.. It takes several minutes.");

$fseek(fp,0,2);//Go to EOF

EOF=$ftell(fp);//EOF position

disp_current_position(fp);

for (i=0;i< No_of_Checks;i=i+1) begin

position={$random} % EOF;//or $unsigned($random) %EOF

word_pos=(position/STR_LEN);

aligned_pos=word_pos*STR_LEN;

$fseek(fp,aligned_pos,0);//Goto aligned_pos

$fscanf(fp,"%h\n",R2);

word={word_pos+3,word_pos+2,word_pos+1,word_pos};

if (word !==R2[127:0] ) begin//Check result

$display("Fails. Error detected");

$stop;//assert(0);

end

end

$display("Random Test passed. Random %d seeks performed . Error Detected 0",No_of_Checks);

end

endtask

endmodule

Opencores Veritak �v���W�F�N�g�t�@�C���iVersion�P�D�S�PA�j

�@

�@Opencores�ɂ́A�v���t�F�b�V���i�����������l�X��IP�R�A������܂��B������ȒP�ɁA�]��/�������Ă݂������������̂ł͂Ȃ��ł��傤���H

�Ƃ��낪�AOpencores���V��INCLUDE�@�t�@�C����ADefine�̐ݒ蓙���K�v�ȏꍇ������A�@����҂̃V�~�����[�^�����Ȃ��ƊȒP�ɂ����Ȃ��Ƃ��낪����܂��B�V�~�����[�^������o���܂łɍ��܂��Ă��܂����l�����邩������܂���B

�����ŁAVeritak�v���W�F�N�g�t�@�C�����쐬���X��}��܂����B

�𓀂��āA�uVerilog�v���W�F�N�g����Load�@Verilog�v�Ńv���W�F�N�g�t�@�C�������[�h�A�uGo�v�����Ńe�X�g�x���`�����肾���܂��B

�l��RTL�\�[�X�́A���������������̂ł����A�g���[�X�t�@�C���i�^�O�t�@�C���j���Y�t���Ă��܂��̂ŁA��͂̈ꏕ�ɂȂ�ł��傤�B

�K�v�ɉ����ăg���[�X���[�h�ŃR���p�C�����邱�ƂŁA�K�wView�AVeriPad�A�g���[�X�t�@�C���i�^�O�t�@�C���j�AWaveformView��ł̃h���C�o����@�\���A�������z�I�ȉ�͊��ɂȂ锤�ł��B

�v���W�F�N�g�́A�ȉ��̌��؉\�ȃe�X�g�x���`�t�̃R�A�ɂ��č쐬���܂����B

�v���W�F�N�g�͕����쐬���Ă���ꍇ������܂����A���̈Ӗ��́A���̒ʂ�ł��B

| �v���W�F�N�g�̖��O | ���e | ���l |

| *_no_save.prj | �g�`Save�Ȃ��̃v���W�F�N�g�B | �������m�F�ς݁B���̃v���W�F�N�g�ł͔g�`�iWaveformView�j�������ɂȂ�܂���̂ł����ӂ��������B |

| *_trace_mode.prj | �g���[�X���[�h�ł̃v���W�F�N�g | |

| *_trace_mode2.prj | �g���[�X���[�h2�ł̃v���W�F�N�g | �g���[�X�t�@�C���̐����p |

| IP�@CORES | Veritak�@�v���W�F�N�g�t�@�C���ʒu | �\�[�X���s�� | �V�~�����[�V�������ԁiAthlon64 3000+�@�PGB�@Memory�@on�@W2K) |

�_�E�����[�h�iZIP) | ���l |

| AC97 | \ac97_ctrl\bench\verilog | 11K | 49min54sec | AC97�i0.3MB) | ac97_no_save.prj |

| CAN | \can | 12K | 0min | CAN�i0.2MB) | can.prj |

| ATA | \ata | 4K | 13min38sec | ATA�i1MB) | Nov.22.2004 no_save_ata.prj |

| PCI | \pci\bench\verilog | 89K | 2�� | PCI�i14MB) | pci_no_save.prj |

| USB1.1 | \usb11 | 11K | 2min37sec | USB1.1�i0.3MB) | `include����ӏ��lj� usb11_no_save.prj |

| I2C | \i2c | 2K | 2sec | I2C(0.7MB) | i2c.prj |

| ETHERNET | \ethernet\ethernet | 45K | 4h | ETHERNET�i2.6MB) | tb_ethernet_no_save.prj |

| AES | \aes_core | 2K | 13sec | AES�i0.2MB) | aes.prj |

| DES | \des | 2K | 1sec | DES�i0.5MB) | des_trace_mode.prj |

| GENERIC FIFO | \generic_fifos\generic_fifos\bench\verilog | 2K | �Q�� | GENERIC�@�@ FIFO�i0.1MB) |

fifo_no_save.prj |

| GPIO | \gpio\gpio | 4K | 41sec | GPIO�i0.6MB) | gpio.prj |

| WB_DMA | \wb_dma | 15K | 46h | WB_DMA�i1.5MB) | |

| WB_CONBUS | \wb_conbus | 4K | 6sec | WB_CONBUS�i0.4MB) | conbus.prj |

| WB_CONMAX | \wb_conmax | 11K |

10min6sec | WB_CONMAX�i0.2MB) | |

| Divider |

dividers\bench\verilog | divierders | divider.vtakprj (Version 2.11�ȏ�@RunLength10�O0us) |

�i���Ƃ��APentium500MHz���ƁA6�{����x�ɂ͂Ȃ��Ă���悤�ł��B

��Opencores�ɂ��ā�

�@��삪�����ł��B�Ȃ��ɂ́A�V�~�����[�V�������Ԃ��ُ�ɂ������Ă�����̂�����܂����A�i���CPU�x���`�}�[�N�e�X�g��ł́A�����Ă������ł��j�@

����́ARegression�@Test�ŁA�ԗ��I�ȃe�X�g�����Ă��邽�߂ł��B���g�́Atask���ŕ����L�q����A�����FOR�@LOOP�ʼnĂ���̂ŁA�v�G�b�Z���X�̃V�~�����[�V�����ł́A����قǑ���������K�v�͂Ȃ��ł��傤�B

�n�[�h�E�F�A�̋L�q�ɁA�@���Ƃ��AA<=#1A���g���Ă���i�V�~�����[�V�����T�C�N�����]�v�ɂ�����ȊO�ɉ��̉v���Ȃ��L�q�j�A�e�X�g�x���`�ł�Race�L�q�������A���A

�K�������悢�L�q�ƌ����Ȃ����̂��܂܂�Ă��܂����A�S�̂̃��x���Ƃ��Ă͍����A��ώQ�l�ɂȂ�Ǝv���܂��B

�@�Ƃ���ŁA����Opencores�@�͂ǂ����Ă���́H�v�����v���Z�b�T�́A���̈Ӗ�����́H�Ƃ������₪�ǂ����炩���ł������ł��B�M�҂̏ꍇ�́AFAQS��Veritak�̖ڎw���Ă�����̂Ƃ��ď����Ă���܂��̂���������Q�Ƃ��B

Opencores�̐l�B�̓��������p���܂��B

Mainly for fun.

Other reasons include:

- to learn,

- to teach,

- to improve your resume,

- to make the world a better place to live in.

CRC��RTL���������v���O�����̉���iMay.5.2005�@�I���j

<�T��>

���L�����N�ŁAWEB��ŁA�C�Ӑ����������A�C�Ӄr�b�g����RTL�\�[�X�������܂��B

http://www.easics.be/webtools/crctool

���ۂɂ���Ă݂�Ɗm���ɐ������܂��B�Ƃ���ŁA����́A�ǂ�����Đ������Ă���̂ł��傤���H�����v���O�����������āA�����R�[�h���o�͂��邱�Ƃ��m�F���܂����B

�܂��A�g�����̗�Ƃ��āAVerilog-2001�Ńe�X�g�x���`�������܂����B�i�{���́A�p���ł��B�j

�Ȃ��ACRC�ɂ��Ă͈ȉ����ڂ����ł��B

�C���^�[�t�F�[�X2004�@12����CRC��H�̍����ƃA�����W�@�X�����v��

���_����w�т������́A

�������_�@�d�q���ʐM�w��@����G��

�������߂��܂��B

=>CRC32�i�q�e�b�Q�O�W�R) ��C �v���O�����ƌ��ʂ�����Ȃ��A�Ƃ�������������������܂����B

��͂��Ă݂��Ƃ���A�r�b�g��MSB��LSB���t���ɂȂ��Ă���܂����B���H/W������́AMSB������͂���d�l�ɂȂ��Ă��܂��B

������ALSB������͂���d�l��C�v���O�����Ɣ�r����ꍇ�́A�r�b�g�����o�[�X����K�v������܂��ˁB

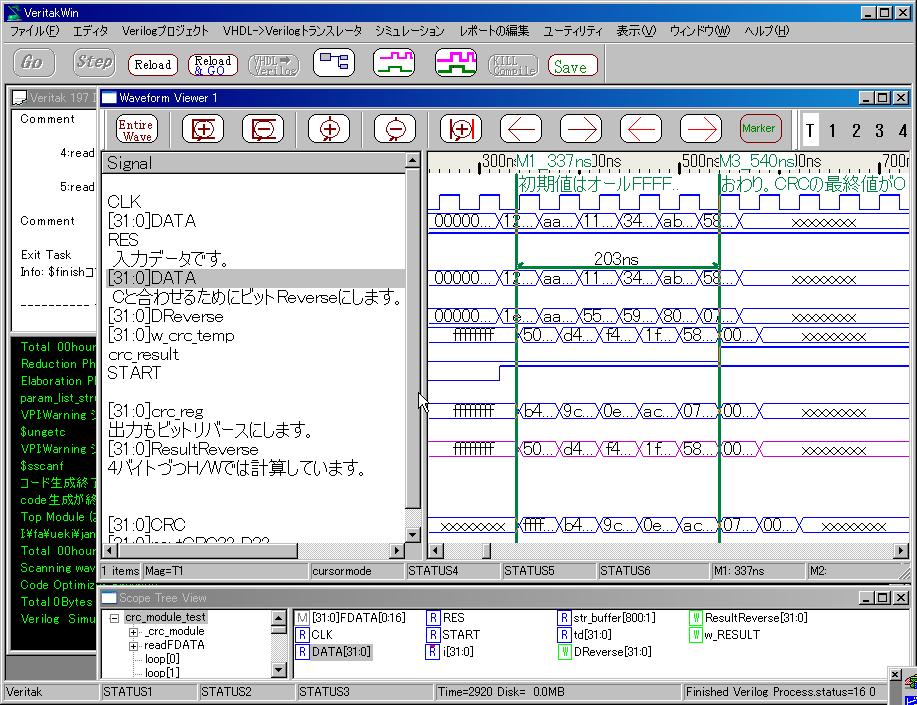

�����ŁA�r�b�g�����o�[�X����L�q��lj�����Ǝ��̂悤�ɂȂ�܂��B����ɂ��H/W���\�[�X�lj��͂���܂���B�i�z�������ł��j

`define CYCLE (10)

`timescale 1ns/1ns

module crc_module_test;

reg RES; // Reset

reg CLK; // clock

reg[31:0] DATA; // data

wire w_RESULT;//TAK

always #20 CLK =~CLK;

parameter RATE = 50;

wire [31:0] DReverse;//TAK

wire [31:0] ResultReverse;//TAK

generate //TAK

genvar g;