ベンチマークテスト

ベンチマークプログラム

SH2

例によってOpencoresから頂いてきます。筆者が追加修正したものをここに置いておきます。オリジナルでは、ベンチマークプログラムが収まりきれなかったので、ROM/RAM容量のUpを行いました。なお、ベンチマークソース、修正済みROM Generator(モトローラ形式→rom.v)は、tool¥sh2_tak以下に入っています。

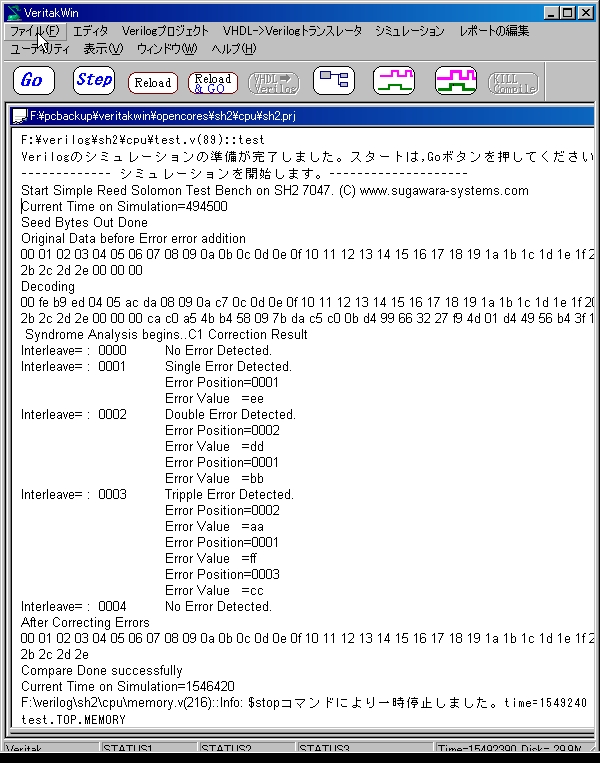

・Cコンパイラ ベストテクノロジー社のGCC Developer Liteを使用しました。GCC オプションSH7047内蔵FLash、最適化Option-02で、ベンチマークプログラムをコンパイルします。 Cコンパイラは、モトローラ形式.motのファイルを出力します。 ・ROM generator オリジナルは、ROM8KB専用になっていますが、32KB専用にしました。VC7でコンパイルしたバイナリも入れておきます。これで、.motファイルから、rom.vファイルを作成します。 ・Verilog修正 rom.vをオリジナルと置き換えます。これにともないメモリIF周りを修正しました。またデバッガも入れ込みます。 ・シミュレーション Verilog プロジェクトファイルsh2.prjをロードします。シミュレーションは、筆者のマシン(Athron1.2GHz)で数分でした。  ここで、テストスタート時の時刻は、494500ns、終了時の時刻が、1546420nsですから、 テスト実行時間は、約1msとなりまます。(実際は、printの時間も含んでいますが)、 さすがに高速なCPUですね。 |