|

・Cコンパイル

SDCCを使いました。以下は筆者環境でのバッチファイルです。

..\bin\sdcc --debug -mmcs51 --model-large 8051test2.c

hex2rom 8051test2.ihx rom52 15l8v > rom52.dat

copy rom52.dat F:\vhdl\t51\*.* |

hex2romは、作者のものを改変し、Verilogの$readmembで読み込めるオプションv/Vを追加しました。

・VHDソース修正

RAMサイズの修正を行いました。

・トランスレート(VHDL->Verilogに変換します。)

translated.vが生成されます。

・Verilogソース追加修正

- デバッガを埋め込みます。

- module rom52を改変し、rom52.datを読み込む仕様としました。というのは、ソースデバッグのため、何回もROMの内容を変更して必要がありその度にVHDLからVerilogに変換するのが面倒だったからです。

- Stack Pointerを設定した直後のサブルーチンコールで、Stack Pointerの設定がおかしくなるソース上のバグがあったので修正(ワークアラウンド)しました。(module t51)(作者に報告済み)なお、このようなCPUソースのデバッグには、CPUシミュレータが有効です。今回はJSIM51を使いました。

- CLOCK周期を50MHzとします。

以上変更したものをdemo.vとします。

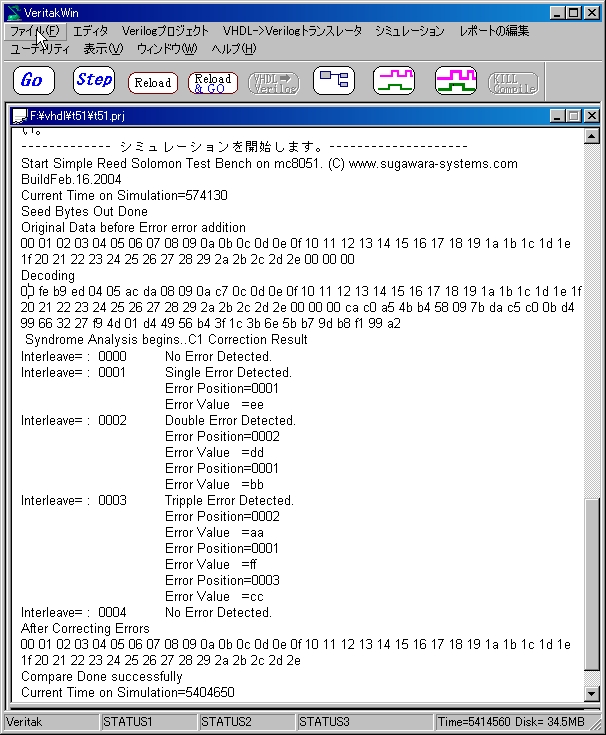

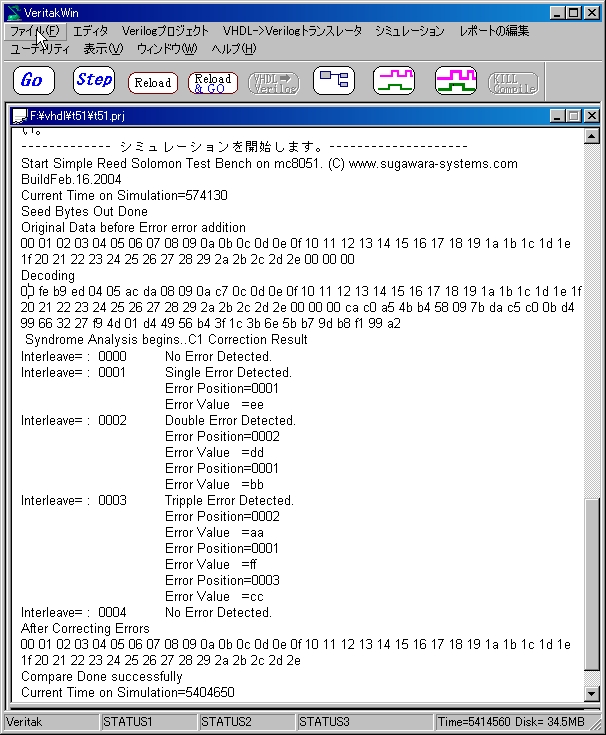

・シミュレーション

t51.prj をLoadVerilogします。

Test時間は、5404650-574130=約4.8msとなりました。AVRより遅いのは、当然としてZ80よりかなり速いという結果になりました。SDCCのコードジェネレータは、8051Nativeで、Z80は後からポートされました。CPU自体の能力差がそんなにあるとは思えないので、多分コンパイラに起因するところが大きいのでしょう。

|