例によってOpencoresから頂いてきます。筆者が追加修正したものをここに置いておきます。

| ・Cコンパイル SDCCを使いました。コンパイルは、

インテル形式から、VHDファイルにしていくれるツールをコアの作者が提供してくれているのでそれを利用します。

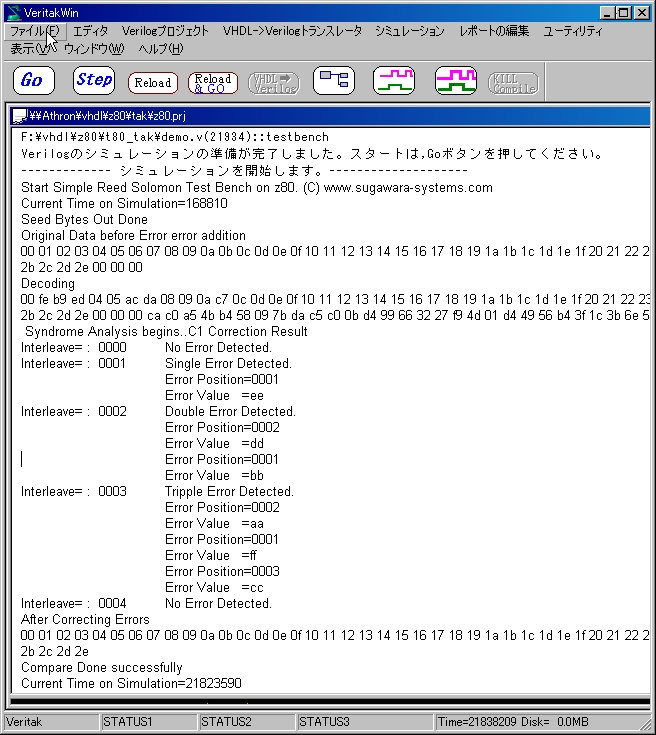

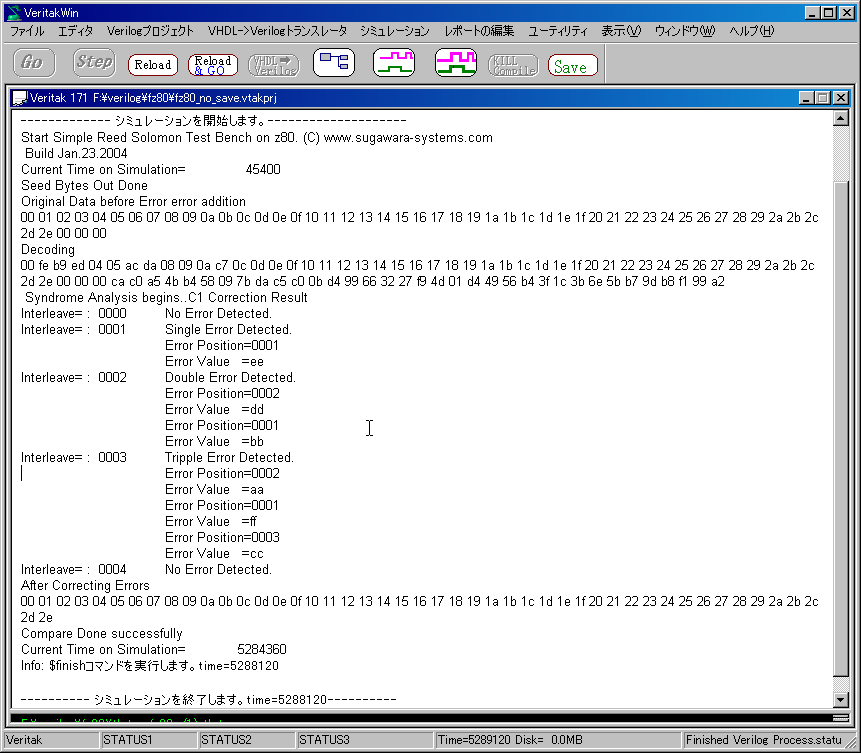

割り込みラインのDisable,及び不要なログファイルの生成を止めました。 rom80.vhdをオリジナルと置き換えます。 ・トランスレート(VHDL->Verilogに変換します。) translated.vが生成されます。(2万行を超えるので少々時間がかかります。) ・Verilogソース追加修正 デバッガを入れ込みます。 ->demo.v ・シミュレーション z80.prj をLoadVerilogします。  Test時間は、21823590-168810=21.7msとなりました。 予想以上に遅くなりました。8ビットバスだからいたしかたない点もありますが、コンパイラの性能も関係しているのだと思います。なおプロジェクトの設定は、DataSaveを外しています。波形をご覧になりたい場合は、[プロジェクト設定」SaveAllSimDataをオン、Reloadしてください。また、MaxDiskCapacityは、600MB以上としてください。 TV80コア 上のコアは、Daniel Wallner氏のT80コアVHDL記述を、トランスレータを使ってほぼ自動翻訳したものです。このコアは、Guy Hutchison 氏によるもので、同じくT80コアをベースにしてVerilogで書かれています。 (ソースを見る限り、トランスレータを使った形跡はなく、おそらく一からマニュアルでVerilogで書かれたものです。)読みやすいソースに仕上がっています。 ここでは、ベンチマークテストが目的ですので、いつものように

筆者が追加修正したVeritakプロジェクトファイルを含む一式をここにおいておきます。 tv80\tv80\env¥no_save.prjをLoad Verilogすると走りだします。 20.7203−0.1589=20.6ms です。T80コアより、僅かに速くなっています。若干の改善していることが分かります。 これは、以下のソースで、Fast Z80がON(1)になっていることによります。これをOFF(0)にすると、ベンチマークは、 T80と完全に一致します。

WB_Z80コア このコアは、数あるZ80コアの中でも 旧WB_Z80一式のダウンロード(2.7MB) Veritak1.5xから走りません。(文法を厳しくチェックした為です。) 新WB_Z80のソースコード改(117KB) Veritak最新版で走ります。ソースコードオリジナル改版ベースです。 ベンチマークを走らせるための修正

プログラムの読み込み方法 作者は、アセンブラのテストソースと、アセンブラを提供しています。Z80を研究している方には、願ってもない環境が構築できます。 上で行ったT80のROMの置き換えを行わずに、HEXファイルを直接読み込む方式としました。 これによる修正点は、以下のソースです。 generic_spram.vのなかで、次のソースを追加します。

(この方法は、アルテラのメガファンクションソースaltera_mf.vのなかでも、ROM/RAMの初期値読み込みとして使われています。) なお、"z80_test2.ihx"は、SDCCコンパイラが吐いたHEXファイルで、T80のプロジェクトで作ったものです。作成方法は、T80をご参照ください。 ベンチマーク wb_z80\wb_z80\rtl¥no_save.prjをLoad Verilogすると走り出します。  テスト時間は、5.82189-0.04550=約5.8msとなり、オリジナルに比べて4倍近い高速化がなされていることが分かります。 アセンブラのテスト 添付している、アセンブラでアセンブルしてみましょう。 次のソースは、アセンブルのためのバッチファイル(asm_tak.bat)です。

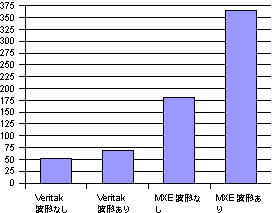

これでアセンブルするとHEXファイルが生成されるので、それをRTLフォルダにCOPYしておきます。 後は、BJS80TST.HEXをベンチマークと同様に読み込めばよいです。 Veritak Viewerを見易すくするための修正 作者は、parameterを多用しています。これをGroup毎にリスト形式に分けることで、「ステート名に名前をつける」 Veritak機能が使えます。 また、$Dumpfileは、Veritak上意味がないので、外します。(全波形を見る場合は、Veritakが圧倒的に有利です。$DumpFileでは、数百MBでも、Veritak上では、数MBということはあります。) wb_z80\wb_z80\rtl¥wb_z80_trace_asm_test.prjをLoad Verilogすると次の画面が現れます。  これのプロジェクトは、トレースモードで構成しているので、任意過去の任意信号のドライバソースに簡単に飛んでゆくことができます。解析には最適です。 なお、アセンブルテストの最後は、CPU HALTして終わりです。  FZ80コア http://www.geocities.jp/kwhr0/hard/fz80.html から1.04をいただいてきます。 (使用は、非商用に限ります。) 手順は、上と同様で、クロック周期を例によって50MHz、上で作ったROMを外付けすればOKです。  実行時間は、約5.2ms、Z80コアの中では最速です。 <少しVeritakのコマーシャルです。> 非常にコンパクトに書かれてあるので、テスト結果を全波形SaveしてもVeritakでは、37MBしか消費しませんでした。(さすがにVCDで全波形Saveすると、300MBを超え、自身で生成したVCDが読めないくらいになってしまいますが。) 圧縮した波形は、ほぼ瞬時に任意の信号を波形に展開できるので、この程度の規模のデバッグには、Veritakは、最適です。Full MXE6.0で、全波形Saveで比較すると約3倍弱Veritakが高速でした。 NETで非常にコンパクトに書かれているので、通常効くはずのNet Optimizeが殆ど効きません。(Net記述での冗長が殆どなく書かれていることを意味します。逆にWB_Z80は、Net Optimizeがよく効きます。) FZ80コア以外のダウンロード(FZ80本体は、上記より入手してください。Veritak Versionは、 1.71です。) =>Veritak最新版で再度計測してみました。Version328C(Fast Mode)、MXE6.1e(starterではありません)です。 波形なしで3倍、波形ありで5倍になっていました  |