例によってOpencoresから頂いてきます。筆者が追加修正したものをここに置いておきます。なお以下は、Veritak REV1.0.1で行っています。

| ・Cコンパイル 作者が添付しているGCCを使いました。以下は筆者環境でのバッチファイルです。 convert.exe はCygwin環境下でコンパイルしました。これが、最終的なcode.txt(メモリイメージ) を出力してくれます。

・VHDLソース修正 今回は、トランスレートされたVerilog上で修正を行いますのでVHDLソース修正はありません。 ・トランスレート(VHDL->Verilogに変換します。) translated.vが生成されます。 ・Verilogソース追加修正

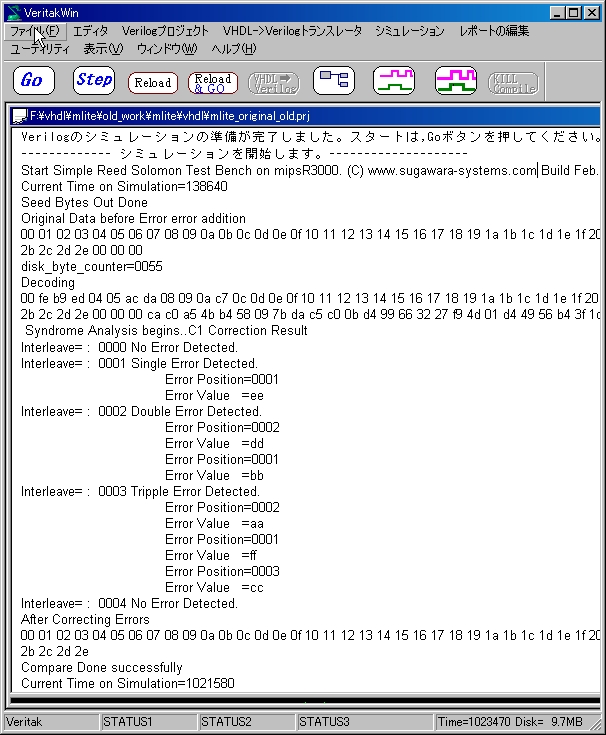

・シミュレーション mlite_original_old.prj をLoadVerilogします。  Test時間は、1021580-138640=約880μsとなり最速です。 さすがですね。 |

論理合成(May.12.2004 New)

その後、更新されているようなので、再度ダウンロード・トランスレートを行い、前回のバグがフィックスされていることを確認しました。Veritak RTLシミュレーションでは、通っても論理合成するとなるとまた、手修正が必要になります。今回作者の提供するツールの修正も含めてAltera CYCLONE用に記述を手修正しました。正味1日の作業でした。一旦RTLシミュレーションがVeritak上で通ってしまえば、後は、そのシミュレーションをリファレンスにしてQuartasが色々言ってくる文句に対処していけばいいのです。筆者は、RTLソースの中身を殆ど理解していませんが、変更の度に、RTLシミュレーションをかけて一致することを確認していけばいいので機械的な作業でOKでした。1万行近いソースを手作業で、変換していたら、Editだけで、2週間、デバッグ2週間というところでしょう。その意味で、トランスレータ+Veritakは、意外によいツールかもしれません。(??)

Qaurtasの合成ツールについて

Verilog2001の構文は、文句を言わないのですが、合成自体は、殆ど1995しか対応できていないようです。以下は、メモです。

- generate ifは、構文エラーにならないが、FalseでもすべてTrueで評価されてしまう模様.従い、Falseのgenerateは、コメントアウトの処理が必要。

- 変数パートセレクト =>対応していない。

- LPM...の記述 => コンパイルエラーが止められなかったので、Wizardで作り直しした。

- Function中のdisalbe文 =>無視されず、たまたま無視されても問題ない所だったので記述はそのまま

- モジュールパラメータ渡しのところの順序があっていない。=>修正

- Initialによる初期化=>弊害のあるところのみ削除修正。無視されるところはそのまま

- Regの2重宣言 =>修正

RAM_SIZE(合計32KBへ)、AREA_OPTIMIZE、TESTBENCH IF等修正

ツールの修正

AltraのRAMに初期値(C プログラムオブジェクトコード)を設定するツールが作者よりbintohex.cとして提供されていますが、うまく動かなかったので、convert.c上に4つの8ビットRAMの初期値をインテルHEXファイル(code0.hex,code1.hex、code2.hex、code3.hex)で出力するツールを作成しました。これでCYCLONEのRAMを初期化します。

なお、合成結果は以下の通りです。記述を最適化したら、50MHzは超えると思います。まだ、改善の余地があります。

ポストレイアウト遅延ゲートシミュレーションログ

筆者の低Spec.マシンでは、(Athron1.2GHz、1GBメモリDIMM)シミュレーションに仮想メモリを使いながら、8時間30分もかかってしまいました。夜仕事を終える前に仕掛けておくとちょうどいい感じです。Alteraのメモリを多く積んだゲートシミュレーションではとにかくメモリを食います。(今回は、32KBです。) が、これでRTLと合成結果の一致を検証することができました。

CLOCK CYCLEは、Max周波数の24.336nsに設定しましたので、前回と時間値が違いますが、 1242961-168600で

当然のことながら、Clock数としては同じになります。

パッケージ

筆者が作成した、ソースとツールをここにおいておきます。ダウンロードされる場合、原作者のLEGAL NOTICEは必ずお読みになり同意した上でお願いします。

ファイルの説明

| translated.v | トランスレータが生成したファイルで、加工していないファイル |

| demo.v | 論理合成とRTL_SIMに使用したファイル |

| convert_tak1.c | code0.hex code1.hex,code2.hex,code3.hexを吐くように筆者が改造したもの |

・Cコンパイル

作者が添付しているGCCを使いました。以下は筆者環境でのバッチファイルです。

convert.exe はconvert_tak1.cをCygwin環境下でコンパイルしました。

| as -o boot.o F:\vhdl\mlite\old_work\mlite\tools\boot.asm gcc -02 -O -DMLITE -Dmain=main2 -Wall -c -s F:\vhdl\mlite\old_work\mlite\tools\mips_test.c ld.exe -Ttext 0 -eentry -Map test.map -s -N -o test.exe boot.o mips_test.o objdump.exe --disassemble test.exe > test.lst convert.exe copy code.txt F:\vhdl\mlite\old_work\mlite\vhdl\*.* |

パッケージのダウンロード