Verilog偱CPU愝寁擖栧

僩儔媄偺晅榐婎斅(2006擭4寧崋乯偱丄CPU傪嶌偭偰傒傑偟傚偆丅偲偙傠偱丄偙偺僨僶僀僗ALTERA丂MAX嘦丄俤俹俵240俿100俠俆偼丄240僙儖偟偐側偄偺偱丄惓峌朄偱偼丄偳偆偑傫偽偭偰傕嵹傝傑偣傫丅僼儔僢僔儏傕嵹偭偰偄傞偺偱偡偑丄偙傟傪ROM偵偟偰偟傑偆偲丄偐側傝抶偔側傞偟丄巊偄曽偑擄偟偄偱偡丅偙偺僙儖悢偼丄忢幆揑偵偼丄悢屄偺僇僂儞僞偱杽傑偭偰偟傑偄傑偡丅偦偙偱丄師偺傛偆側曽恓偱愝寁偟傑偟偨丅

- 1擔偱愝寁偱偒傞娙扨側傾乕僉僥僋僠儍(僴乕僪僜乕僗偼300峴埲壓乯

- RISC傾乕僉僥僋僠儍傪恀帡偡傞

- 幚梡惈傕峫椂偟丄16價僢僩墘嶼丄32價僢僩僀儞僗僩儔僋僔儑儞/儚乕僪

- 僷僞乕儞僕僃僱儗乕僞偲偟偰幚梡偵懴偊傞

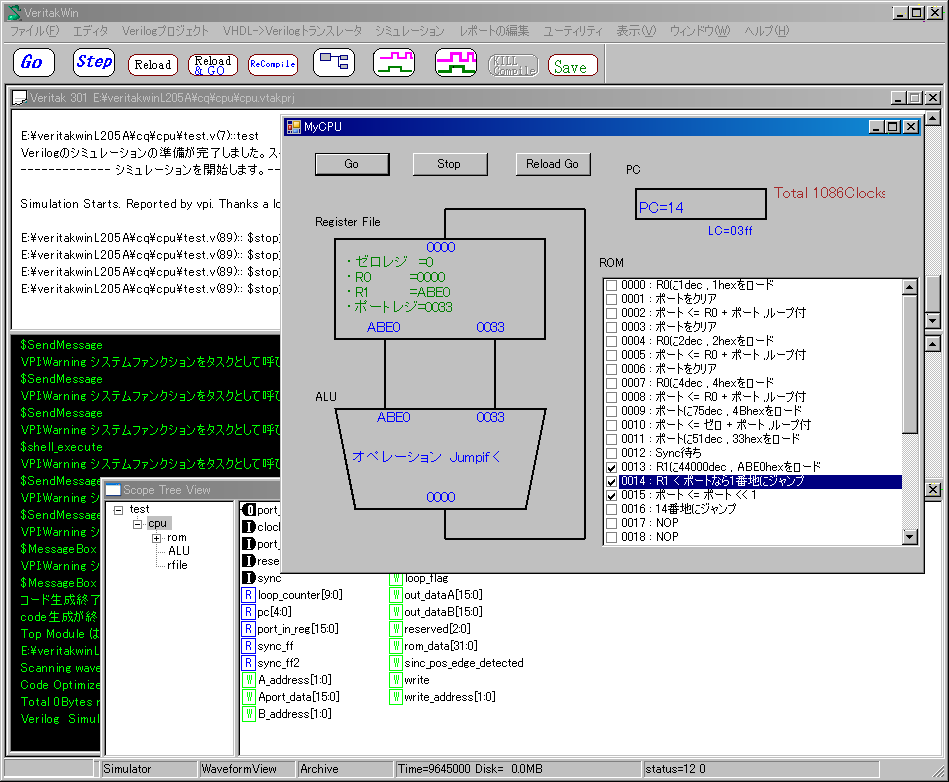

- 擖栧梡偲偟偰丄CPU傾乕僉僥僋僠儍傪梕堈偵棟夝偱偒傞傛偆丄VPI偱價僕儏傾儖側摦嶌娐嫬傪採嫙

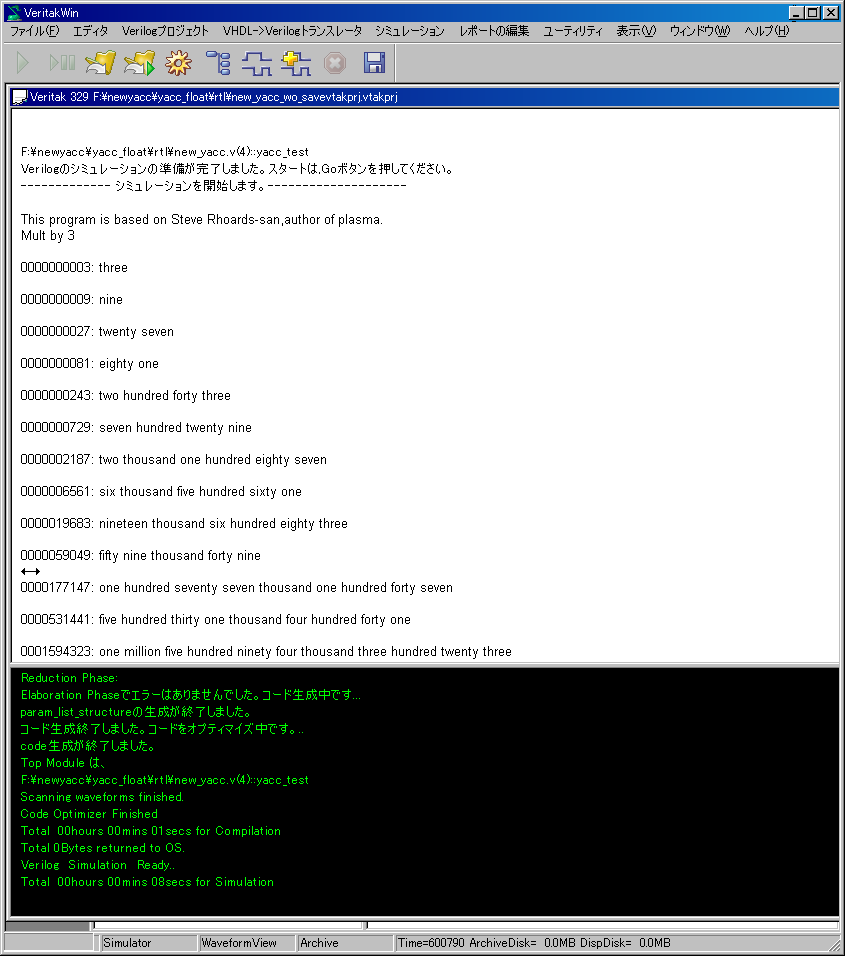

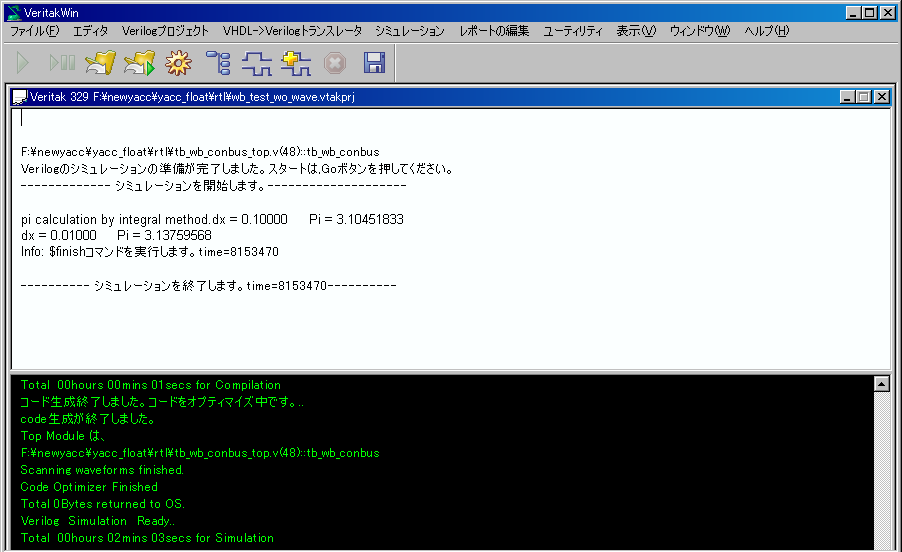

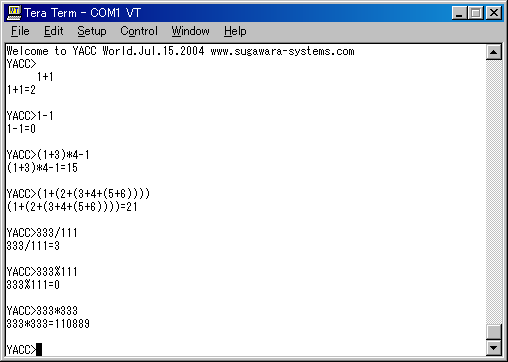

偲偄偆曽恓偱愝寁偟傑偟偨丅僼儔僢僔儏傪巊梡偟偰偄傑偣傫偺偱丄僩儔媄僨僶僀僗偱偼丄16儚乕僪埵偟偐嵹傝傑偣傫丅偦傟偱傕丄椺偊偽丄師偺傛偆側僷僞乕儞傪敪惗偝偣傞偙偲偑偱偒傑偡丅乮傑偨丄ROM梕検偑嫋偣偽丄俇係KWORD傑偱奼挘壜擻側傾乕僉僥僋僠儍偵側偭偰偄傑偡丅乯

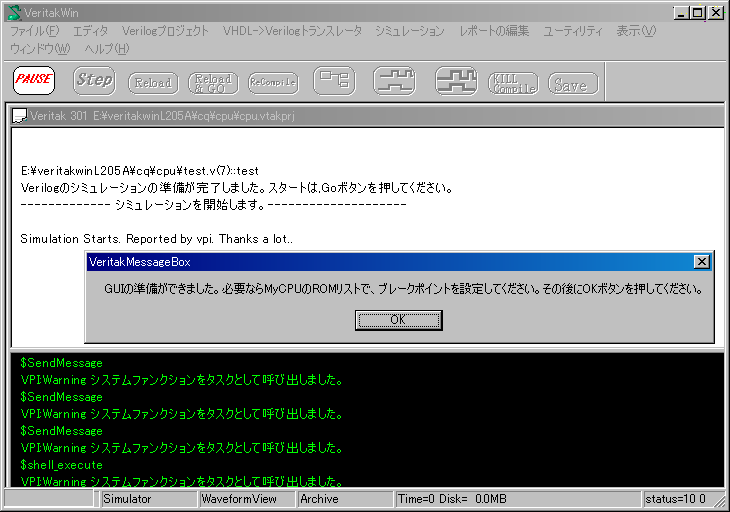

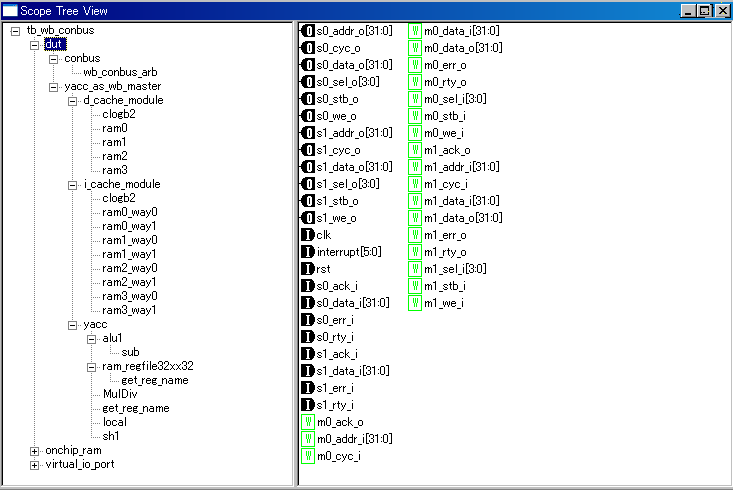

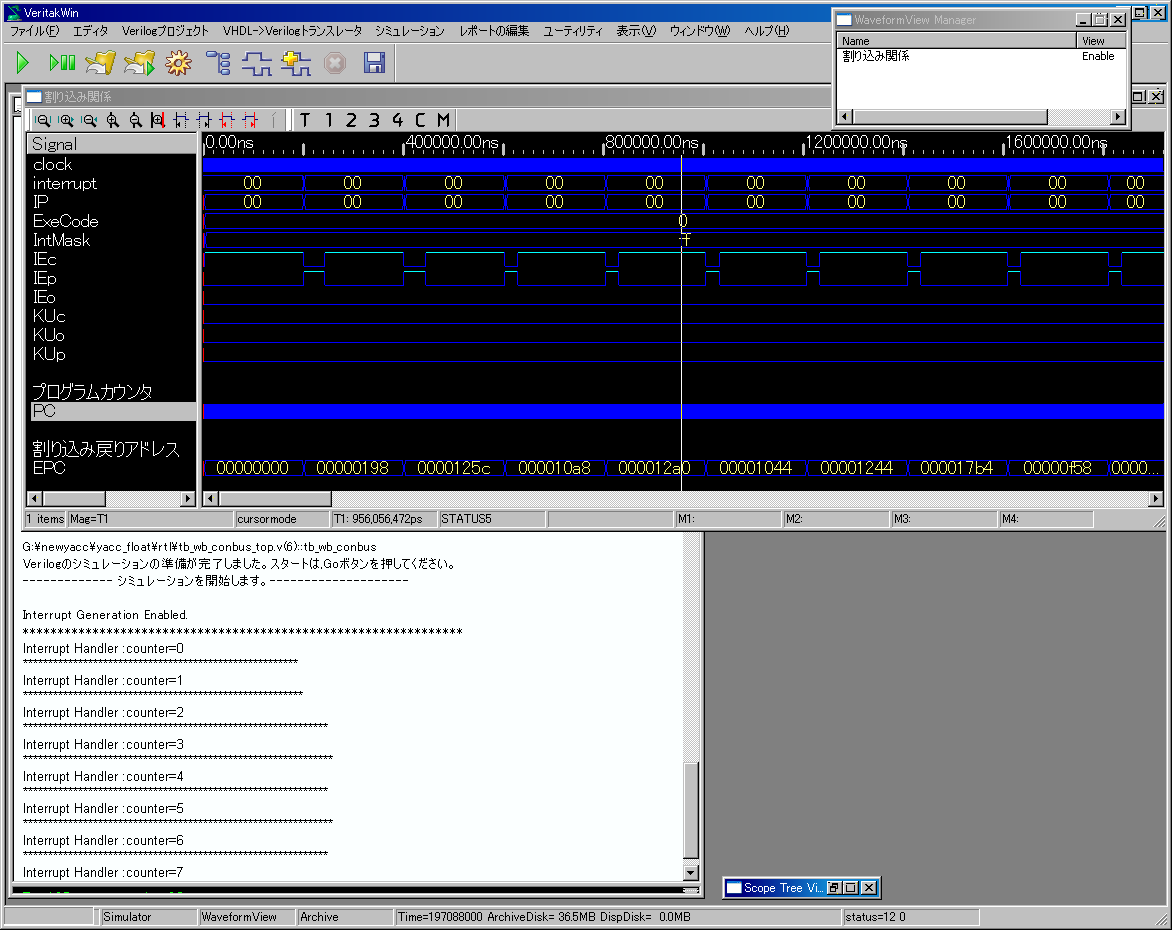

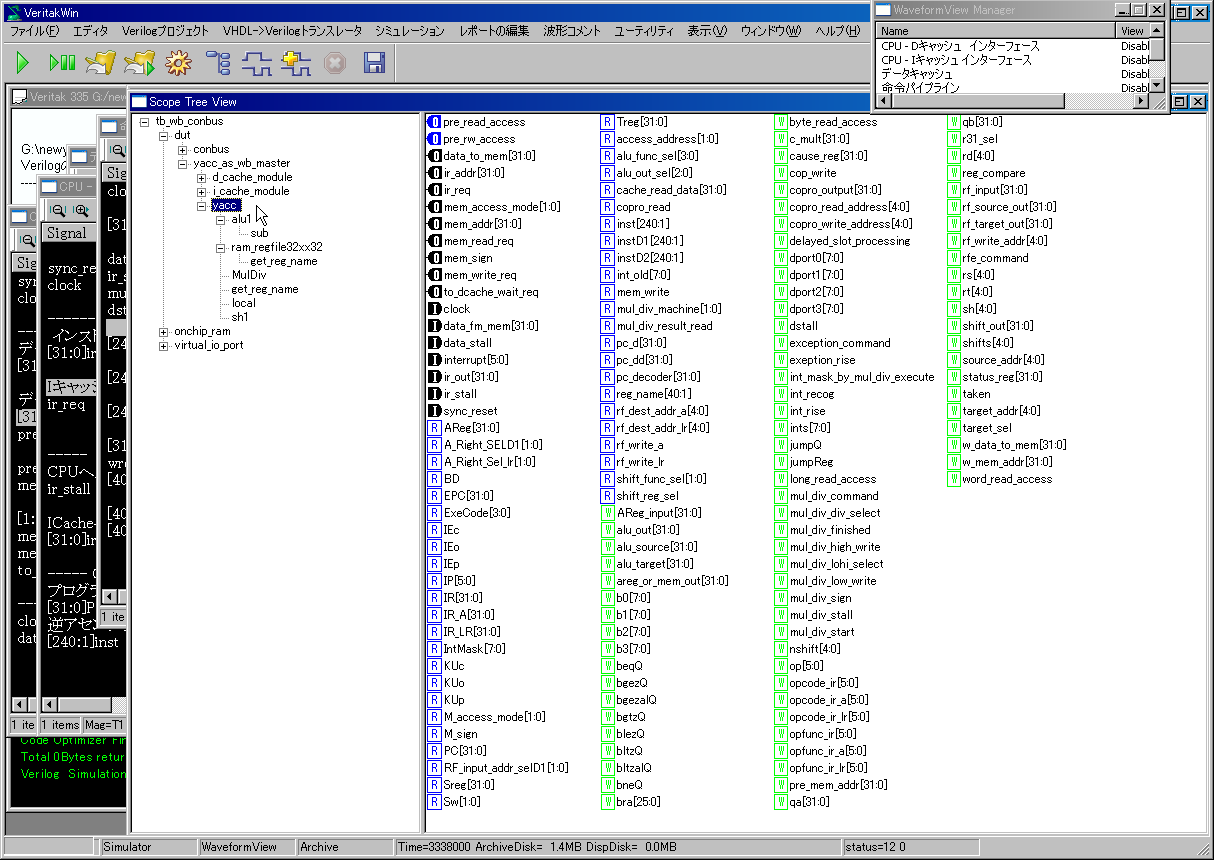

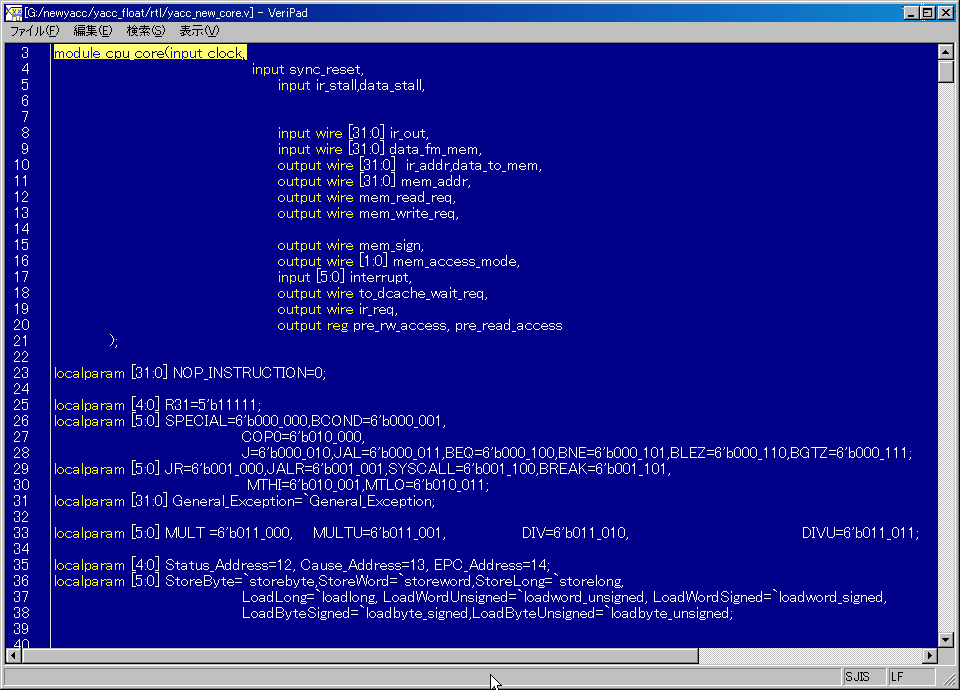

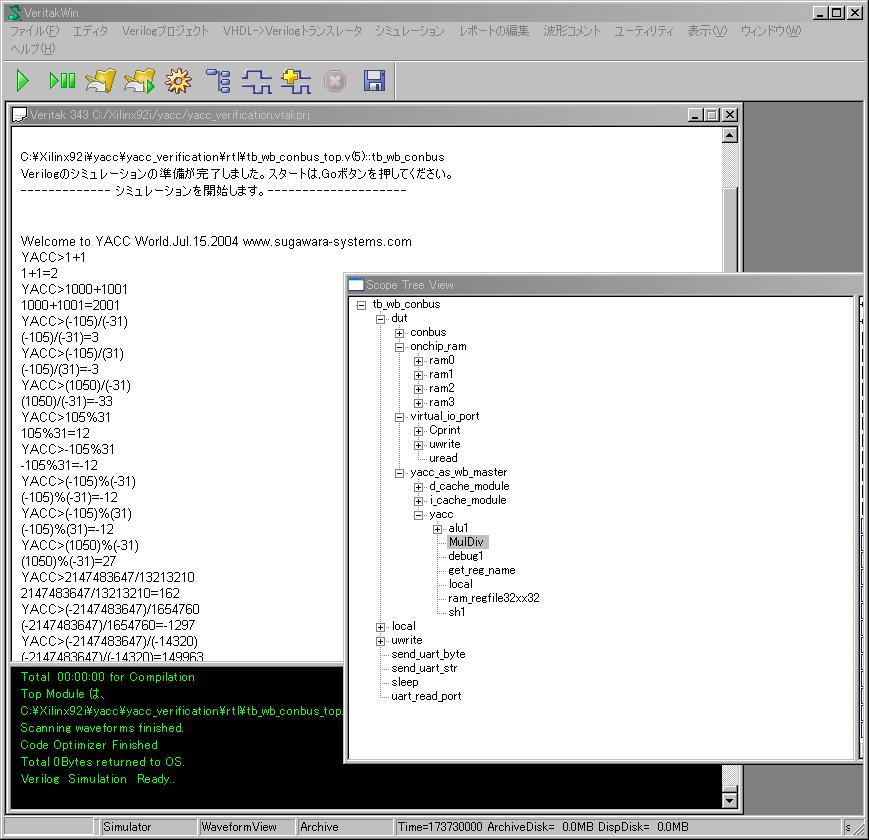

傑偨丄價僕儏傾儖偵撪晹偺忬懺傪僽儗乕僋億僀儞僩晅偱妋擣偡傞偙偲偑弌棃傑偡丅乮椺偵傛偭偰GUI偼丄C#偱嶌惉偟偰偄傑偡丅乯

偙傟偵傛傝丄梕堈偵CPU偺拞恎偺摦偒傪抦傞偙偲偑偱偒傑偡丅

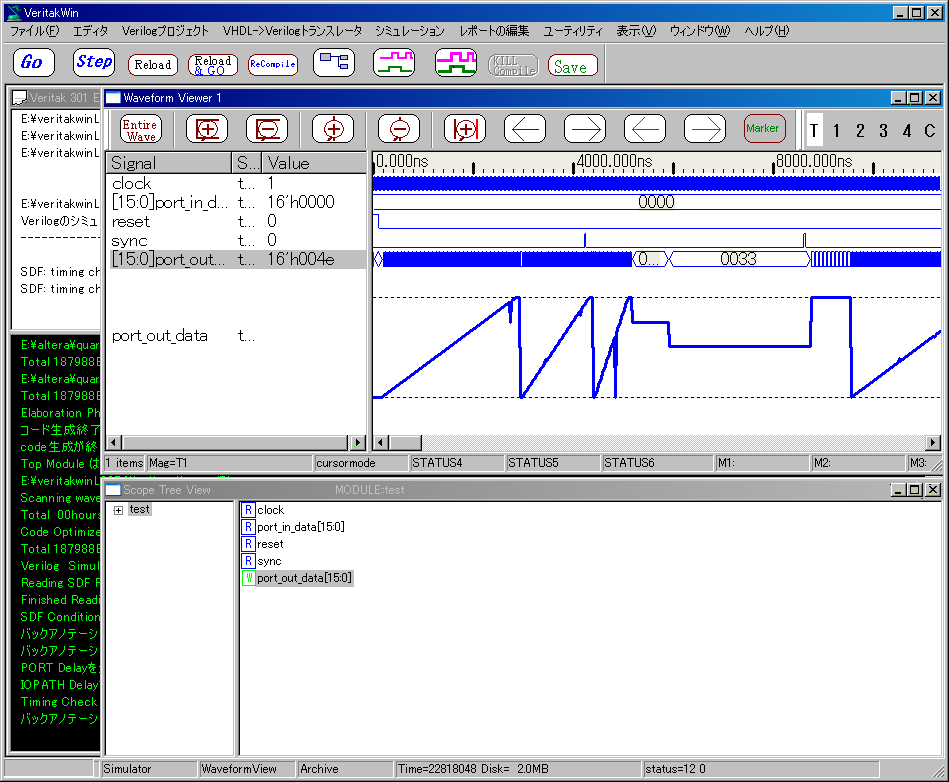

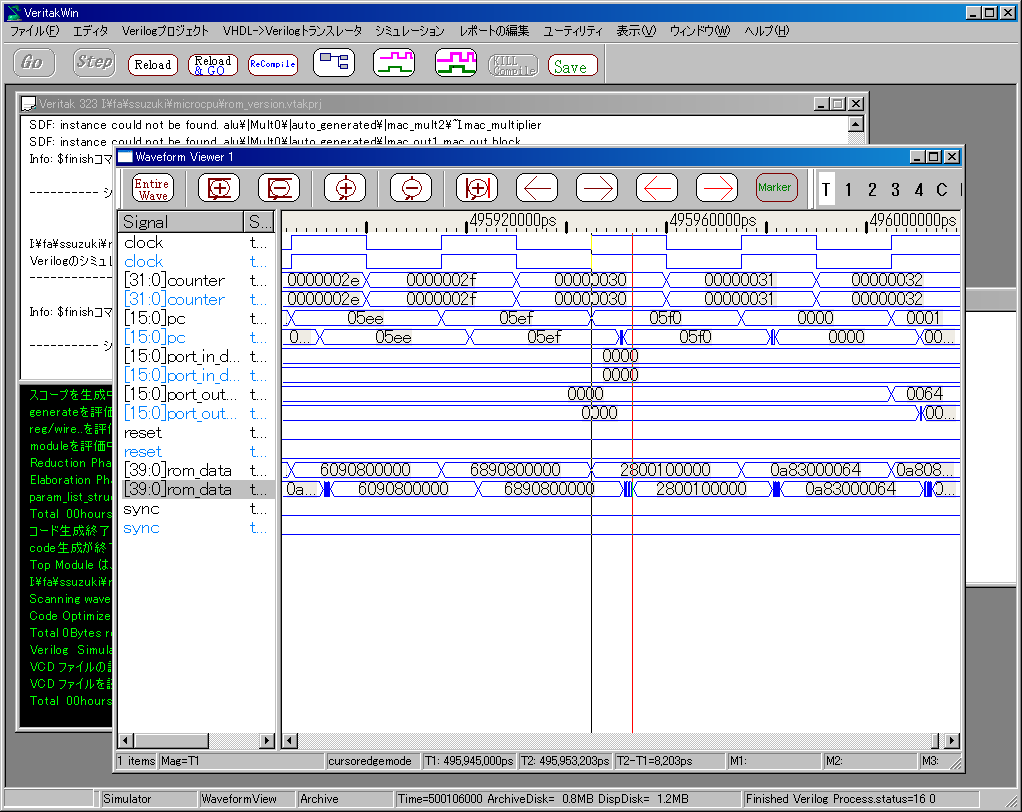

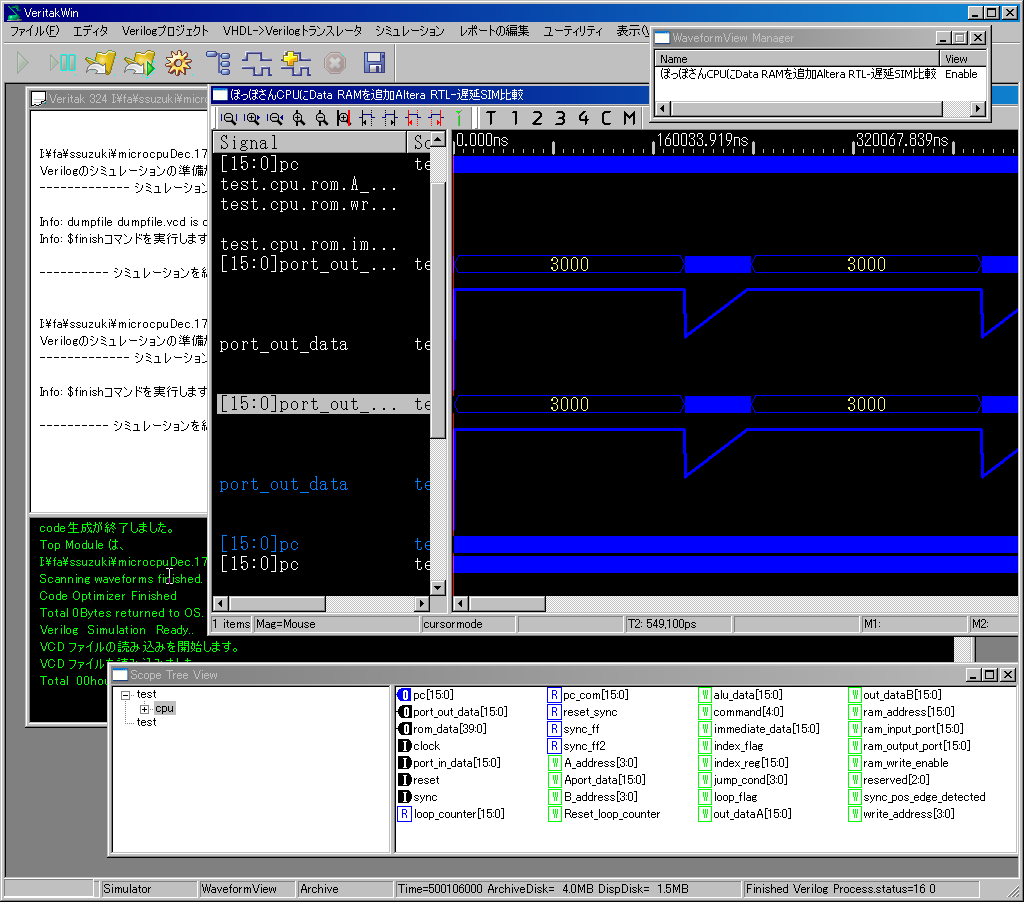

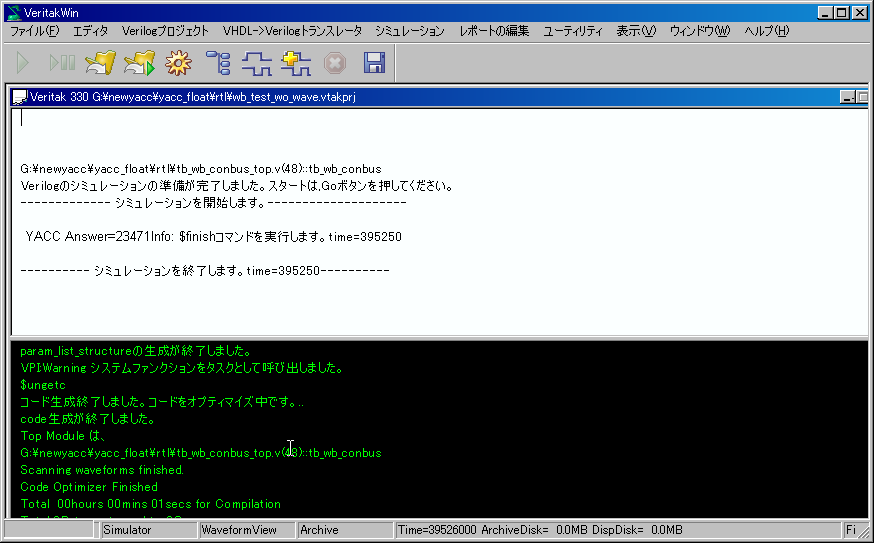

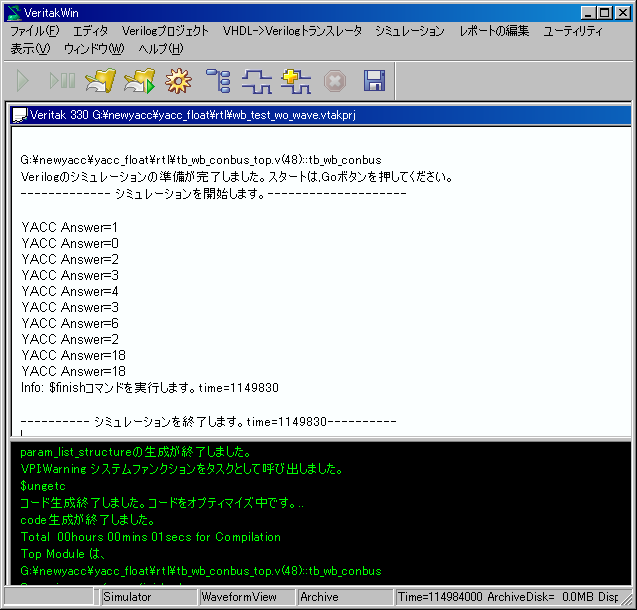

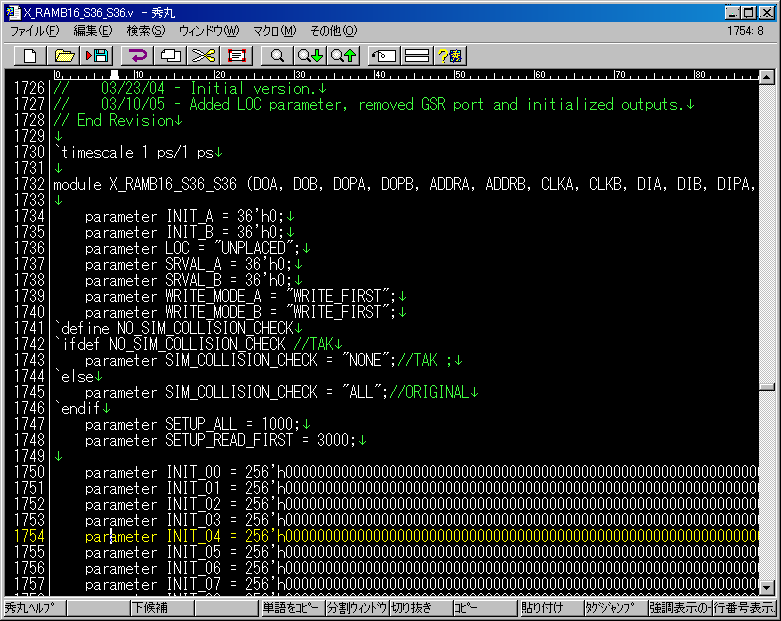

MAX2偵儗僀傾僂僩屻偺抶墑僔儈儏儗乕僔儑儞偱傕摦嶌妋擣偟偰偄傑偡丅乮僸僎偼丄抶墑偑堦掕偟偰偄側偄偨傔偱偡丅乯

亙CPU偲偼丄弴彉婡夿亜

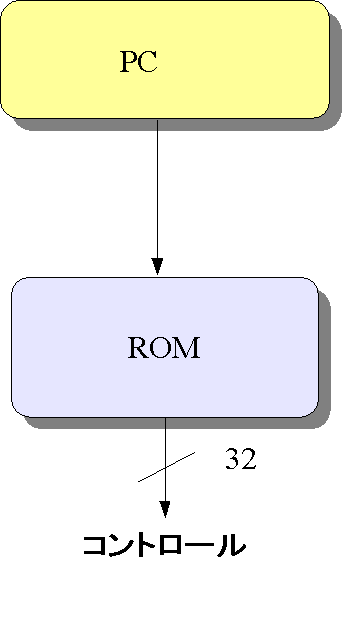

堦斣扨弮側弴彉婡夿偲偄偊偽丄僇僂儞僞偱偡丅僇僂儞僞偼丄弴斣傪惗惉偟傑偡偺偱丄偦傟偵ROM傪偮偗傟偽丄僐儞僩儘乕儖晅偒偺弴彉婡夿偵側傝傑偡丅

壓恾偱丄僇僂儞僞傪PC亖僾儘僌儔儉僇僂儞僞偲尵偆偲奿岲傛偔側傝傑偡丅偝偰愝寁偟偨CPU偼丄32價僢僩暆偑偁傞偺偱丄ROM偺暆偼32價僢僩偵側傝傑偡丅

偦偺傑傑偱偼丄側偵偐傪敾抐偟偰張棟傪曄偊傞偲偄偆偙偲偑偱偒側偄偺偱丄PC傪側傫傜偐偺宍偱惂屼偡傞昁梫偑偁傝傑偡丅傑偨丄偦偺堊偵偼丄堦帪揑側婰壇慺巕偑昁梫偱

偡丅婰壇慺巕傪儗僕僗僞偺廤傑傝偲偟偰傑偲傔偨傕偺傪儗僕僗僞僼傽僀儖偲尵偄傑偡丅忋偺儗僕僗僞僼傽僀儖偼丄摨帪偵撉傒彂偒偱偒傞億乕僩偑俁偮偁傝傑偡丅儔僀僩億乕僩偑堦偮丄儕乕僪億乕僩偑擇偮偱偡丅傑偨丄儗僕僗僞悢偼丄16價僢僩偑4屄偱偡丅

堦斣栚偺僛儘儗僕僗僞偼丄RISC偱偼丄掕斣偱偡丅嵟屻偺億乕僩儗僕僗僞偼丄偙偺CPU偩偗偺摿庩巇條偱偡丅乮儕僜乕僗嶍尭偺偨傔乯

| 柤徧 | 婡擻 |

| 僛儘 | Write偟偰傕Read偟偰傕侽丄側偺偱幚懱偼丄偨偩偺GND |

| R0 | 斈梡儗僕僗僞 |

| R1 | 斈梡儗僕僗僞 |

| 億乕僩 | 摿庩儗僕僗僞丄偦偺傑傑丄奜晹億乕僩弌椡偵側傞 |

HDL僜乕僗偱尒偰傕傜偭偨傎偆偑暘偐傝傗偡偄偐傕偟傟傑偣傫丅

module register_file(input clock,write,reset,

input [1:0] A_address,

input [1:0] B_address,

input [1:0] write_address,

input [15:0] alu_data,port_in_data,

output [15:0] out_dataA, out_dataB,port_out_data);

reg [15:0] port_reg,r0,r1;

always @(posedge clock,posedge reset) begin

if (reset) begin

port_reg<=0;

r0<=0;

r1<=0;

end else if (write) begin

case (write_address)

`PORT: port_reg<=alu_data;

`R0: r0<=alu_data;

`R1: r1<=alu_data;

//default r0<=alu_data;

endcase

end

end

assign out_dataA=A_address==`PORT ? port_in_data :

A_address==`R0 ? r0 :

A_address==`R1 ? r1 : 0;

assign out_dataB=B_address==`PORT ? port_reg :

B_address==`R0 ? r0 :

B_address==`R1 ? r1 : 0;

assign port_out_data=port_reg;

endmodule

偝偰丄儗僕僗僞僼傽僀儖偺屻抜偼丄ALU偱偡丅杮奿揑側ALU傪幚憰偟偰偄傑偡丅

module alu (input [3:0] command,

input [2:0] jump_cond,

input [15:0] portA,portB,

output reg [15:0] alu_out);

always @* begin

case (command)

`ADD_com : alu_out=portA+portB;

`SUB_com : alu_out=portA-portB;

`SHIFT_L_com: alu_out=portB >>1;

`SHIFT_R_com: alu_out=portB <<1;

`JMP_com :

case (jump_cond)

`Eq : alu_out=portA==portB;

`Not_Eq:alu_out=portA !=portB;

`Always : alu_out=1;

`Always_Not :alu_out=0;

`LT : if (portA < portB) alu_out=1;

else alu_out=0;

`GT : if (portA > portB) alu_out=1;

else alu_out=0;

default: alu_out=0;

endcase

default: alu_out=portA+portB;

endcase

end

endmodule

屻偼丄PC偺僐儞僩儘乕儖偱偡丅偙傟偼丄屻弎偡傞僷僞乕儞僕僃僱儗乕僞偲偟偰偺婡擻偑擖偭偰偄傞偨傔偵丄偪傚偭偲偩偗暋嶨偱偡偑丄偨偄偟偨偙偲偼偁傝傑偣傫丅

幬傔帤傪柍帇偟偰撉傓偲丄JUMP僐儅儞僪偺偲偒丄ALU弌椡偺價僢僩侽偑1偩偭偨傜丄immediate

data 偺斣抧傪儘乕僪丄偦傟埲奜偼丄pc<=pc+1 ;偮傑傝丄偨偩偺僇僂儞僞偲偄偆偙偲偱偡丅

偙偺immediate_data 偼丄32價僢僩暆偺ROM偺壓埵16價僢僩偵妱傝摉偰偰偄傑偡丅偱偡偐傜丄ROM偺梕検偝偊嫋偣偽丄俇係KWORD傑偱丄偳偙偵偱傕旘偽偡偙偲偑偱偒傑偡丅

//control of PC

always @(posedge clock, posedge reset) begin

if (reset) pc<=0;

else if (command==`JMP_com && alu_data[0]==1'b1) pc<=immediate_data;//Jump if jump condition is met.

else if (command==`SYNC_com) begin//Sync Start Condition

if (sinc_pos_edge_detected) pc<=pc+1;//Exectute Next Address!

else pc<=pc;//Hold until sync pulse is detected.

end else if (loop_flag ) begin//Loop Condition

if (loop_counter==0) pc<=pc+1;//Execute Next Address!

else pc<=pc;//Hold until loop counter becomes zero.

end else pc<=pc+1;//else increment PC

end

婎杮揑偵偼丄埲忋偺梫慺傪偮側偘傟偽丄CPU偵側傝傑偡丅偡偛偔娙扨偱偡偹丅栜榑侾CLK偱丄侾INSTRUCTION張棟偱MUX俀僨僶僀僗偱傕俁侽MH倸埲忋偱摦嶌壜擻偱偡丅

偝偰丄ROM弌椡偼丄32價僢僩偺撪16價僢僩傪旘傃愭偵巊偄傑偟偨丅

巆傝偺僼傿乕儖僪傪娷傓妱晅偼師偺傛偆偵側偭偰偄傑偡丅

| 價僢僩埵抲 | 價僢僩暆 | 柤徧 | 撪梕 |

| 31:28 | 4 | command | 僐儅儞僪 |

| 27:26 | 2 | A_address | 儗僕僗僞僼傽僀儖A億乕僩偺傾僪儗僗 |

| 25:24 | 2 | B_address | 儗僕僗僞僼傽僀儖B億乕僩偺傾僪儗僗 |

| 23:22 | 2 | write_address | 儗僕僗僞僼傽僀儖儔僀僩億乕僩偺傾僪儗僗 |

| 21:19 | 3 | jump_cond | 僕儍儞僾忦審 |

| 18:16 | 3 | reserved | |

| 16:16 | 1 | loop_flag | 儖乕僾張棟偡傞偐偳偆偐偺僼儔僌丄侾偱儖乕僾張棟 |

| 15:0 | 16 | immediate | 懄抣傑偨偼丄旘傃愭 |

柦椷偺撪梕傪夝搥偡傞僨僐乕僪偲偄偆張棟偼偁傝傑偣傫丅偱偡偺偱丄32價僢僩偲偄偆峀偄價僢僩暆偑梫傞偺偱偡偑丄偦偺暘娙扨偵愝寁偱偒傑偡丅

偙偺傛偆偵ROM偺弌椡傪惂屼慄偵巊偆傗傝曽傪儅僀僋儘僐乕僪曽幃偲屇傃傑偡丅偙偺CPU偼丄儅僀僋儘僐乕僪帺懱偑丄婡夿岅柦椷偵側偭偰偄傑偡丅

偙偺CPU偑Native偱丄傕偭偰偄傞柦椷偼丄師偱偡丅

`define ADD_com 4'b0000 `define LOAD_IM_com 4'b0001 `define SUB_com 4'b0010 `define SHIFT_L_com 4'b0011 `define SHIFT_R_com 4'b0100 `define JMP_com 4'b0101 `define SYNC_com 4'b0110

傛偔傾僙儞僽儔偱尒偐偗傞MOV柦椷偑偁傝傑偣傫丅偙傟偼丄RISC偺掕斣偱偁傞丄僛儘儗僕僗僞偲偺壛嶼偱幚尰偟偰偄傑偡丅

僜乕僗偱偼丄儅僋儘掕媊偱丄價僢僩僼傿乕儖僪傪32價僢僩偺ROM僐乕僪偵曄姺偟偰偄傑偡丅

`define MOV( r0, r1) {Add,r0,ZR, r1,Eq,Reserved,Zero_Im}

忋偺僐乕僪偺堄枴偼丄

丂丂丂r1 <=r0 +0

偵側傝傑偡丅

摨條偵丄儅僋儘偱柦椷傪掕媊偡傞偙偲偑偱偒傑偡丅傾僙儞僽儔偱傛偔尒偐偗傞NOP偼丄偳偆幚憰偟偨傜傛偄偱偟傚偆偐丠幚偼丄ALL丂侽偼丄NOP偵偟偰偄傑偡丅

偦偺堄枴偼丄

丂丂僛儘儗僕僗僞亙亖僛儘儗僕僗僞亄僛儘儗僕僗僞

偱偡丅

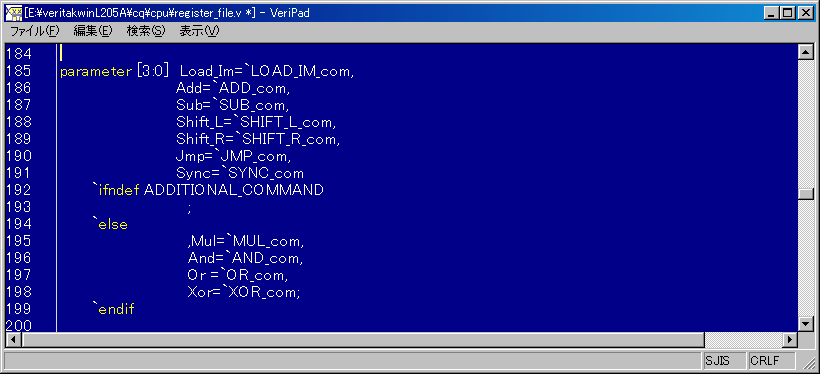

parameter [1:0] Port=`PORT,//IO PORT

R0= `R0,

R1= `R1,

ZR= `ZR;//ZERO REGISTER

parameter [15:0] Zero_Im=16'h0000;

parameter [3:0] Load_Im=`LOAD_IM_com,

Add=`ADD_com,

Sub=`SUB_com,

Shift_L=`SHIFT_L_com,

Shift_R=`SHIFT_R_com,

Jmp=`JMP_com,

Sync=`SYNC_com;

parameter [2:0] Eq=`Eq,

Not_Eq=`Not_Eq,

Always=`Always,

Always_Not=`Always_Not,

LT=`LT,

GT=`GT,

LTE=`LTE,

GTE=`GTE;

parameter [2:0] Reserved=3'b000,

Loop_Enabled=3'b001;

`define MOV( r0, r1) {Add,r0,ZR, r1,Eq,Reserved,Zero_Im}

`define CLR( r0) { Add,ZR,ZR,r0,Eq,Reserved,Zero_Im}

`define JUMP(num) {Jmp,ZR,ZR,ZR,Always,Reserved,16'd num}

`define LOAD_IM(r0,num) {Load_Im,Port,ZR,r0,Eq,Reserved,16'd num}

`define ADD(r0,r1,r2) { Add,r0,r1,r2,Eq,Reserved,Zero_Im}

`define SUB(r0,r1,r2) { Sub,r0,r1,r2,Eq,Reserved,Zero_Im}

`define JUMP_IF_LESS_THAN(r0,r1,num) {Jmp,r0,r1,ZR,LT,Reserved,16'd num}

`define JUMP_IF_GREATER_THAN(r0,r1,num) {Jmp,r0,r1,ZR,GT,Reserved,16'd num}

`define JUMP_IF_EQ(r0,r1,num) {Jmp,r0,r1,ZR,Eq,Reserved,16'd num}

`define SHIFT_L(r0,r1) {Shift_L,ZR,r0,r1,Eq,Reserved,Zero_Im}

`define SHIFT_R(r0,r1) {Shift_R,ZR,r0,r1,Eq,Reserved,Zero_Im}

`define SYNC {Sync,ZR,ZR,ZR,Eq,Reserved,Zero_Im}

偙偙傑偱丄撉傫偱偔傟偰偁傝偑偲偆偛偞偄傑偡丅偦偆偱偡丅傾僙儞僽儔偼側偄偺偱偡丅

ROM僐乕僪偼丄椺偊偽丄忋偱掕媊偟偨儅僋儘傪巊偭偰師偺傛偆偵彂偒傑偡丅

偙傟偧丄媶嬌偺乽僐儞僺儏乕僞偺尨棟傪妛傇乿丂偐傕偟傟傑偣傫丅丂偙偆偄偆柦椷偑梸偟偄偲偄偆偺偑偁偭偨傜丄忋偱儅僋儘掕媊偟偰偟傑偊偽丄傛偄栿偱偡丅

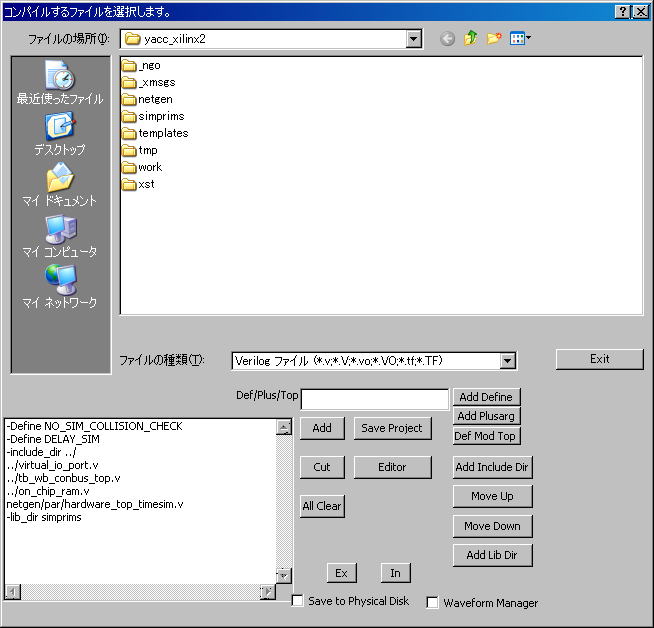

儅僋儘揥奐偼丄Veritak僆僾僔儑儞偱丄preout.v丂偲偟偰尒傟傑偡偺偱丄巚偄捠傝偵揥奐偝傟偰偄傞偐僠僃僢僋偟偰傒偰傕傛偄偱偟傚偆丅

function [31:0]romdata;

input [4:0] address;

case (address) //Commad A_addr, B_addr, Write_addr, Jmp_cond,Reserved, IM

0: romdata =`LOAD_IM(R0,1);

1: romdata =`CLR(Port);

2: romdata =`Add_with_loop(Port,R0,100);

3: romdata =`CLR(Port);

4: romdata =`LOAD_IM(R0,2);

5 : romdata =`Add_with_loop(Port,R0,50);

6: romdata =`CLR(Port);

7: romdata =`LOAD_IM(R0,4);

8 : romdata =`Add_with_loop(Port,R0,25);

9 : romdata =`LOAD_IM(Port,75);

10: romdata =`Add_with_loop(Port,ZR,25);

11: romdata =`LOAD_IM(Port,51);

12: romdata =`SYNC;

13: romdata =`LOAD_IM(R1,44000);

14: romdata =`JUMP_IF_LESS_THAN(R1,Port,1);

15 : romdata =`SHIFT_R(Port,Port);

16: romdata =`JUMP(14);

// 3 : romdata =`LOAD_IM(R0,100);

// 4 : romdata =`LOAD_IM(R1, 62444);

// 5 : romdata =`ADD(R0,R1,Port);

// 6 : romdata =`LOAD_IM(Port,10000);

// 7 : romdata =`ADD(R0,R1,R0);

// 8 : romdata =`SUB(R0,R1,R0);

// 9 : romdata =`ADD(Port,R0,R0);

// 10 : romdata =`JUMP_IF_LESS_THAN(R0,R1,0);

// 11 : romdata =`JUMP_IF_EQ(R0,R1,3);

17 : romdata =0;

18 : romdata =0;

19 : romdata =0;

20 : romdata =0;

default : romdata=0;

endcase

endfunction

亙Confiugurable CPU亜

偙偺CPU偱丄愝寁偟偰偄偰柺敀偄偙偲偵婥偯偒傑偟偨丅偦傟偼丄偙偺CPU偼丄ROM儚乕僪偄偔偮傑偱MAX2偵嵹傞偲偼丄尵偊側偄偙偲偱偡丅幚嵺偵ROM偱巊偆柦椷偵傛傝傑偡丅ROM傪儊儌儕偲偟偰偱偼側偔丄LUT偱峔惉偟偰偄傞偺偱丄幚憰偡傞柦椷偱塭嬁傪庴偗傑偡丅偮傑傝丄ALU偱偼丄偄傠偄傠掕媊偟偰偁傞偺偱偡偑丄榑棟崌惉偱丄巊傢側偄儘僕僢僋偼丄梕幫側偔Rudction偝傟傑偡丅儅僕僢僋偺庬柧偐偟偱偟偨丅

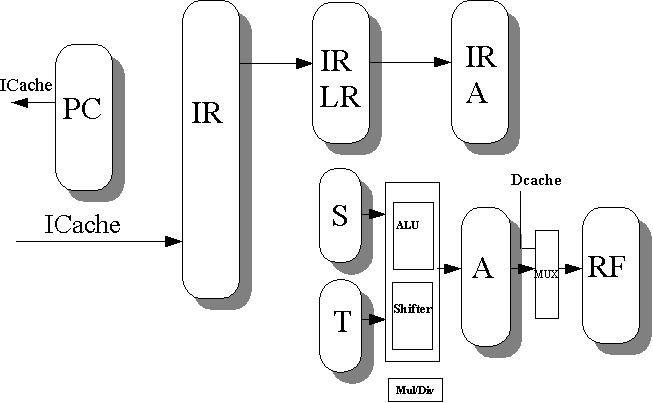

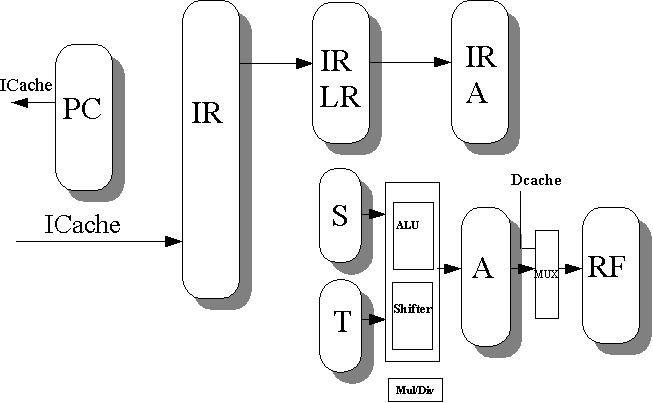

亙僷僀僾儔僀儞壔偲偄偆偙偲亜

偙偺CPU偼丄挿偄僷僗傪帩偭偰偄傑偡丅懡暘丄PC偵巒傑傝ROM丂->Register丂FILE丂亅亜ALU亅亜丂PC丂僐儞僩儘乕儖儘僕僢僋乕亜PC偵棃傞僷僗偑嵟挿偩傠偆偲巚偄傑偡丅

嵟挿偺僷僗傪僋儕僥傿僇儖僷僗偲尵偄傑偡丅僷僀僾儔僀儞壔偟偨晛捠偺CPU偱偼丄偙偺僷僗偼壗抜偐偺FF娫偺慻傒崌傢偣夞楬偵暘妱偝傟傞偙偲偵側傝傑偡丅丂

CPU偺墳梡

亙僷僞乕儞Generator亜

儖乕僾僼儔僌傪ON偵偡傞偲丄儖乕僾僇僂儞僞偑0偵側傞傑偱丄偦偺応強偵棷傑傝丄柦椷傪孞傝曉偟傑偡丅偙傟偼丄Shift墘嶼偵傕妶梡偡傞偙偲偑偱偒傑偡丅

//loop command

`define Shift_Right_with_Loop(r0,num) {Shift_R,ZR,r0,r0,Eq,Loop_Enabled,16'd num }

`define Add_with_loop(r0,r1,num) { Add,r1,r0,r0,Eq,Loop_Enabled,16'd num} //Use Bport for port_reg

儖乕僾僇僂儞僞偼丄懄抣偲寭梡偱偡偺偱丄慡柦椷偱揔梡偱偒傞栿偱偼丄偁傝傑偣傫丅偟偐偟丄擟堄帪娫暆偺僷僞乕儞傪嶌傞応崌偵偼丄偙偺惈幙偼丄廳曮偟傑偡丅 傑偨丄SYNC柦椷偱丄POS丂EDGE偱柦椷僗僞乕僩偲偄偆偙偲傕偱偒傑偡丅BINARY偺僔儕傾儖僷僞乕儞傪嶌傞応崌偼丄16價僢僩偛偲偵丄CPU傊CLCOCK傪梌偊傟偽丄僔儕傾儖僷僞乕儞惗惉婍偵傕側傝傑偡丅 亙VPI亜 崱夞傕丂vpi_dll5.dll 偵捛壛偟傑偟偨丅$SendMessage偲丄$MessageBox 傪捛壛偟傑偟偨丅偦偺柤偺捠傝偱偡偑丄徻嵶偼僜乕僗傪嶲徠偔偩偝偄丅 崱夞捛壛偟偨僜乕僗偼師偱偡丅

搊榐晹

//Jul.11.2006

tf_data.type =vpiSysFunc;//

tf_data.sysfunctype =vpiIntFunc;//

tf_data.tfname = "$SendMessage";

tf_data.user_data = "$SendMessage";

tf_data.calltf = sys_SendMessage;

tf_data.compiletf = 0;

tf_data.sizetf = sys_systems_size_tf;//func

vpi_register_systf(&tf_data);

tf_data.type =vpiSysFunc;//

tf_data.sysfunctype =vpiIntFunc;//

tf_data.tfname = "$MessageBox";

tf_data.user_data = "$MessageBox";

tf_data.calltf = sys_MessageBox;

tf_data.compiletf = 0;

tf_data.sizetf = sys_systems_size_tf;//func

vpi_register_systf(&tf_data);

幚憰晹

static int sys_SendMessage(char* name)

{

vpiHandle systfref, argsiter, argh;

s_vpi_value value;

systfref = vpi_handle(vpiSysTfCall, NULL); /* get system function that invoked C routine */

argsiter = vpi_iterate(vpiArgument, systfref);/* get iterator (list) of passed arguments */

unsigned message_parameter[4];

for (unsigned i=0;i<4;i++){

argh = vpi_scan(argsiter);/* get the one argument - add loop for more args */

if(!argh){

vpi_printf("$VPI sys_SendMessage: missing parameter. \n");

// vpi_sim_control(vpiFinish, 1);

return 0;

}

value.format = vpiIntVal;

vpi_get_value(argh, &value);

message_parameter[i]=value.value.integer;

}

unsigned result= ::SendMessage(reinterpret_cast<HWND>(message_parameter[0]),//handle

message_parameter[1],//WM_COMMAND

message_parameter[2],//WPARAM

message_parameter[3]);//LPARAM

if(argh) vpi_free_object(argsiter);

value.value.integer =result;//;

value.format = vpiIntVal;/* return the result */

vpi_put_value(systfref, &value, NULL, vpiNoDelay);

return(0);

}

static int sys_MessageBox(char* name)

{

vpiHandle systfref, argsiter, argh;

s_vpi_value value;

systfref = vpi_handle(vpiSysTfCall, NULL); /* get system function that invoked C routine */

argsiter = vpi_iterate(vpiArgument, systfref);/* get iterator (list) of passed arguments */

unsigned message_id=0;

string str_message;

string str_caption;

for (unsigned i=0;i<2;i++){

argh = vpi_scan(argsiter);/* get the one argument - add loop for more args */

if(!argh){

vpi_printf("$VPI sys_MessageBox: missing parameter. \n");

// vpi_sim_control(vpiFinish, 1);

return 0;

}

value.format = vpiStringVal;

vpi_get_value(argh, &value);

if (i==0) str_message=value.value.str;

else if (i==1) str_caption=value.value.str;

}

argh = vpi_scan(argsiter);

if (argh) {

value.format = vpiIntVal;

vpi_get_value(argh, &value);

message_id=value.value.integer;

}

unsigned result=MessageBox(0,str_message.c_str(),

str_caption.c_str(),message_id);

if(argh) vpi_free_object(argsiter);

value.value.integer =result;//;

value.format = vpiIntVal;/* return the result */

vpi_put_value(systfref, &value, NULL, vpiNoDelay);

return(0);

}

僥僗僩儀儞僠偺僜乕僗偱偡丅

Verilog丂HDL僜乕僗偐傜丄MessageBox傪奐偔偙偲偑偱偒傑偡丅

`timescale 1ns/1ps

`ifdef GATE_SIM

`define CYCLE 26.92

`else

`define CYCLE 30

`endif

module test;

reg clock=0;

reg reset=0;

reg [15:0] port_in_data=0;

reg sync=0;

wire [15:0] port_out_data;

always #(`CYCLE/2) clock=~clock;

initial begin

reset=1;

#105;

reset=0;

#1000000;

$finish;

end

cpu cpu(.clock,.reset,.sync,.port_in_data,.port_out_data);

always @(negedge clock) begin

if (port_out_data==51) begin

repeat( 100) begin

@(negedge clock);

end

sync=1;

@(negedge clock);

sync=0;

end

end

localparam integer MB_YESNO=4;

localparam integer MB_YES=6;

localparam integer MB_NO=7;

localparam integer TOP_MOST=32'h4_0000;

`ifndef GATE_SIM

integer handle,i;

reg [8*20:1] str;

reg [31:0] data;

integer result;

parameter integer WM_COMMAND=32'h111;

initial begin

handle=$FindWindow("MyCPU");

if (handle) begin

end else begin :loop0

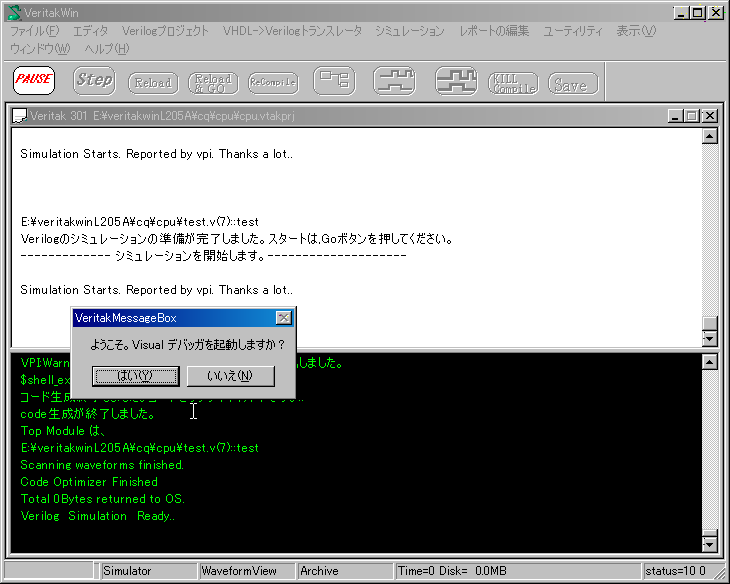

result=$MessageBox("傛偆偙偦丅Visual 僨僶僢僈傪婲摦偟傑偡偐丠","VeritakMessageBox",MB_YESNO | TOP_MOST );

if (result==MB_YES) begin

$shell_execute("cpu");

repeat(100) begin//Retry丂LOOP丟丂Repeat until MyCPU is detected.

$Sleep(100);//100ms wait

handle=$FindWindow("MyCPU");

if (handle) disable loop0;

end

end

end

if (handle) begin

$SendMessage(handle,WM_COMMAND,256,0);//ROM 僐乕僪傪憲弌

for (i=0;i<32;i=i+1) begin

data=cpu.rom.romdata(i);

$SendMessage(handle,WM_COMMAND,i+256,data);

end

$MessageBox("GUI偺弨旛偑偱偒傑偟偨丅昁梫側傜MyCPU偺ROM儕僗僩偱丄僽儗乕僋億僀儞僩傪愝掕偟偰偔偩偝偄丅偦偺屻偵OK儃僞儞傪墴偟偰偔偩偝偄丅","VeritakMessageBox");

end else begin

//$MessageBox("MyCPU偑婲摦偱偒傑偣傫偱偟偨丅","VeritakMessageBox");

end

end

always @(negedge clock) begin

handle=$FindWindow("MyCPU");

if (handle) begin//尰嵼偺忬懺傪憲弌

//regfile

$SendMessage(handle,WM_COMMAND,1,cpu.rfile.out_dataA);

$SendMessage(handle,WM_COMMAND,2,cpu.rfile.out_dataB);

$SendMessage(handle,WM_COMMAND,3,cpu.rfile.alu_data);

$SendMessage(handle,WM_COMMAND,4,cpu.rfile.r0);

$SendMessage(handle,WM_COMMAND,5,cpu.rfile.r1);

$SendMessage(handle,WM_COMMAND,6,cpu.rfile.port_reg);

$SendMessage(handle,WM_COMMAND,7,cpu.ALU.portA);

$SendMessage(handle,WM_COMMAND,8,cpu.ALU.portB);

$SendMessage(handle,WM_COMMAND,9,cpu.ALU.alu_out);

$SendMessage(handle,WM_COMMAND,10,cpu.ALU.command);

$SendMessage(handle,WM_COMMAND,11,cpu.ALU.jump_cond);

$SendMessage(handle,WM_COMMAND,12,cpu.loop_counter);

//PC 僐儅儞僪偼儔僗僩偵憲傞

result=$SendMessage(handle,WM_COMMAND,0,cpu.pc);

if (result==-1) begin//僽儗乕僋梫媮偑GUI偐傜棃偨傜

$stop;

end

end

end

`endif

integer handle_7led;

initial begin

handle_7led=$FindWindow("7LED");//傪扵偡

if (!handle_7led)begin :loop1

result=$MessageBox("億乕僩弌椡傪7僙僌儊儞僩LED僷僱儖偵弌椡偟傑偡偐丠","VeritakMessageBox",MB_YESNO | TOP_MOST );

if (result==MB_YES) begin

$shell_execute("LED7SEG");//7僙僌儊儞僩LED傪棫偪忋偘傞

repeat(100) begin//嵟挿100ms倶侾侽侽=10sec懸偪

$Sleep(100);

handle_7led=$FindWindow("7LED");//傪扵偡

if (handle_7led) disable loop1;//尒偮偐偭偨傜扙弌

end

end

end

end

always @(negedge clock) begin

handle_7led=$FindWindow("7LED");

if (handle_7led) begin :LED//尰嵼偺忬懺傪憲弌

reg [31:0] led_value={1'b0,decoder(port_out_data[15:12]),

1'b0,decoder(port_out_data[11:8]),

1'b0,decoder(port_out_data[7:4]),

1'b0,decoder(port_out_data[3:0])};

$SendMessage(handle_7led,WM_COMMAND,led_value,0);

end

end

function [6:0] decoder(input [3:0] din);//7segment LED

case (din)

4'b0000 : decoder = 7'b1111110;

4'b0001 : decoder = 7'b0110000;

4'b0010 : decoder = 7'b1101101;

4'b0011 : decoder = 7'b1111001;

4'b0100 : decoder = 7'b0110011;

4'b0101 : decoder = 7'b1011011;

4'b0110 : decoder = 7'b1011111;

4'b0111 : decoder = 7'b1110000;

4'b1000 : decoder = 7'b1111111;

4'b1001 : decoder = 7'b1111011;

4'b1010 : decoder = 7'b1110111;

4'b1011 : decoder = 7'b0011111;

4'b1100 : decoder = 7'b1001110;

4'b1101 : decoder = 7'b0111101;

4'b1110 : decoder = 7'b1001111;

4'b1111 : decoder = 7'b1000111;

endcase

endfunction

endmodule

C#僜乕僗偱偡丅

using System;

using System.Collections.Generic;

using System.ComponentModel;

using System.Data;

using System.Drawing;

using System.Text;

using System.Windows.Forms;

using System.Collections;

using System.Runtime.InteropServices;

namespace cpu

{

public partial class Form1 : Form

{

public Form1()

{

InitializeComponent();

command_array = new int[10000];

}

[DllImport("USER32.DLL")]

public static extern int FindWindow(

int hWnd, String lpText );

[DllImport("USER32.DLL")]

public static extern void PostMessage(

int hWnd, int com,int wp,int lp);

int wp = 0;

int lp = 0;

int[] command_array;

int a_port_address=0;

int b_port_address=0;

int write_port_address=0;

int current_pc=0;

uint clock = 0;

uint regfile_R0 = 0;

uint regfile_PORT = 0;

uint regfile_R1 = 0;

uint regfile_a_port=0;

uint regfile_b_port=0;

uint regfile_write_port=0;

uint alu_port_a=0;

uint alu_port_b=0;

uint alu_out_port=0;

uint loop_counter=0xffffffff;

uint alu_operation = 0;

uint alu_jump_cond = 0;

string get_register_name(int num)

{

switch (num)

{

case (0): return "僛儘";

case (1): return "R0";

case (2): return "R1";

case (3): return "億乕僩";

}

return "";

}

private void make_code()

{

int command = (lp >> 28 ) & 0xf;

int address = wp - 256;

if (address == 0)

{

checkedListBox1.Items.Clear();

clock = 0;

command_array.Initialize();

}

if(address>=0) command_array[address] = lp;

int a_port_address=(lp >>26) & 3 ;

int b_port_address = (lp >> 24) & 3;

int write_port_address=(lp>>22) & 3;

int jump_cond = (lp >> 19) & 7;

int loop_flag = (lp >> 16) & 1;

uint immediate =(uint)( lp & 0xffff);

string str;

str =address.ToString("d4");

str +=" : ";

if (lp == 0)

{

str +="NOP";

checkedListBox1.Items.Add(str);

}

else if (command == 0)//Add

{

if (a_port_address == 0 && b_port_address == 0)//CLR

{

string str_word = str+get_register_name(write_port_address);

str_word += "傪僋儕傾";

checkedListBox1.Items.Add(str_word);

}else if (b_port_address == 0)//MOV

{

string str_word = str+get_register_name(a_port_address);

str_word += "偐傜";

str_word += get_register_name(write_port_address);

str_word += "傊偺僐僺乕";

checkedListBox1.Items.Add(str_word);

}

else

{//Add

string str_word =str+ get_register_name(write_port_address);

str_word += " <= ";

str_word += get_register_name(a_port_address);

str_word += " + ";

str_word += get_register_name(b_port_address);

if (loop_flag == 1) str_word += " ,儖乕僾晅";

checkedListBox1.Items.Add(str_word);

}

}

else if (command == 1)//load IM

{

string str_word = str + get_register_name(write_port_address);

str_word += "偵";

str_word += immediate.ToString("d");

str_word += "dec , ";

str_word += immediate.ToString("X");

str_word += "hex傪儘乕僪";

checkedListBox1.Items.Add(str_word);

}

else if (command == 2)//SUB

{

string str_word = str + get_register_name(write_port_address);

str_word += " <= ";

str_word += get_register_name(a_port_address);

str_word += " - ";

str_word += get_register_name(b_port_address);

checkedListBox1.Items.Add(str_word);

}

else if (command == 3)//

{

string str_word = str + get_register_name(write_port_address);

str_word += " <= ";

str_word += get_register_name(b_port_address);

str_word += " >> 1 ";

if (loop_flag == 1) str_word += " ,儖乕僾晅";

checkedListBox1.Items.Add(str_word);

}

else if (command == 4)//

{

string str_word = str + get_register_name(write_port_address);

str_word += " <= ";

str_word += get_register_name(b_port_address);

str_word += " << 1 ";

if (loop_flag == 1) str_word += " ,儖乕僾晅";

checkedListBox1.Items.Add(str_word);

}

else if (command == 5)//JUMP

{

string str_word = str ;

if (jump_cond==2) {//always

str_word += immediate.ToString("d");

str_word += "斣抧偵僕儍儞僾";

checkedListBox1.Items.Add(str_word);

}else if (jump_cond==3) {//not always

str +="NOP";

checkedListBox1.Items.Add(str);

}else {

str_word += get_register_name(a_port_address);

if (jump_cond == 0) str_word += " = ";

else if (jump_cond == 1) str_word += " != ";

else if (jump_cond == 4) str_word += " < ";

else if (jump_cond == 5) str_word += " > ";

else if (jump_cond == 6) str_word += " <= ";

else if (jump_cond == 7) str_word += " >= ";

str_word += get_register_name(b_port_address);

str_word += "側傜";

str_word += immediate.ToString("d");

str_word += "斣抧偵僕儍儞僾";

checkedListBox1.Items.Add(str_word);

}

}

else if (command == 6)//Sync

{

string str_word = str ;

str_word += "Sync懸偪";

checkedListBox1.Items.Add(str_word);

}

}

private void draw_values()

{

int address = wp - 256;

if (address >= 0) make_code();

else

{

switch (wp) {

case (0) :current_pc=lp;break;

case (1): regfile_a_port =(uint) lp; break;

case (2): regfile_b_port =(uint) lp; break;

case (3): regfile_write_port =(uint) lp; break;

case (7): alu_port_a = (uint)lp; break;

case (8): alu_port_b = (uint)lp; break;

case (9): alu_out_port = (uint)lp; break;

case (4): regfile_R0 = (uint)lp; break;

case (5): regfile_R1 = (uint)lp; break;

case (6): regfile_PORT = (uint)lp; break;

case (10): alu_operation = (uint)lp; break;

case (11): alu_jump_cond = (uint)lp; break;

case (12): loop_counter = (uint)lp; break;

}

}

}

private void draw_alu(Graphics g,int x, int y)

{

Pen p = new Pen(Color.Black, 2);

Point[] ps = {new Point(10+x, 30+y), new Point(220+x, 30+y),

new Point(200+x, 130+y), new Point(30+x, 130+y)};

//愜傟慄傪堷偔

g.DrawPolygon(p, ps);

string a_port_str = alu_port_a.ToString("X4");

string b_port_str = alu_port_b.ToString("X4");

string write_port_str = alu_out_port.ToString("X4");

string alu_op_str = "僆儁儗乕僔儑儞";

switch (alu_operation)

{

case (0): alu_op_str += "Add"; break;

case (2): alu_op_str += "Sub"; break;

case (3): alu_op_str += " >> "; break;

case (4): alu_op_str += " << "; break;

case (5): alu_op_str += " Jump";

switch (alu_jump_cond)

{

case (0): alu_op_str += "if Eq"; break;

case (1): alu_op_str += "if Not Eq"; break;

case (2): alu_op_str += "Always"; break;

case (3): alu_op_str += "Always Not"; break;

case (4): alu_op_str += "if < "; break;

case (5): alu_op_str += "if > "; break;

case (6): alu_op_str += "if <= "; break;

case (7): alu_op_str += "if >= "; break;

}

break;

}

Font objFont1 = new Font("俵俽 俹僑僔僢僋", 11);

g.DrawString(a_port_str, objFont1, Brushes.Blue, 50+x, 30+y);

g.DrawString(b_port_str, objFont1, Brushes.Blue, 150+x, 30+y);

g.DrawString(write_port_str, objFont1, Brushes.Blue, 100+x, 110+y);

g.DrawString(alu_op_str, objFont1, Brushes.Blue, 25 + x, 70 + y);

}

private void draw_regfile(Graphics g, int x, int y)

{

Pen p = new Pen(Color.Black, 2);

Point[] ps = {new Point(10+x, 30+y), new Point(220+x, 30+y),

new Point(220+x, 130+y), new Point(10+x, 130+y)};

//愜傟慄傪堷偔

g.DrawPolygon(p, ps);

string a_port_str = regfile_a_port.ToString("X4");

string b_port_str = regfile_b_port.ToString("X4");

string write_port_str = regfile_write_port.ToString("X4");

string regfile_zero_str = "丒僛儘儗僕丂=0";

string regfile_R0_str = "丒R0 丂="+regfile_R0.ToString("X4");

string regfile_R1_str = "丒R1 丂="+regfile_R1.ToString("X4");

string regfile_Port_str = "丒億乕僩儗僕="+regfile_PORT.ToString("X4");

Font objFont1 = new Font("俵俽 俹僑僔僢僋", 11);

g.DrawString(a_port_str, objFont1, Brushes.Blue, 70, 140);

g.DrawString(b_port_str, objFont1, Brushes.Blue, 180, 140);

g.DrawString(write_port_str, objFont1, Brushes.Blue, 130, 60);

g.DrawString(regfile_zero_str, objFont1, Brushes.Green, 50, 75);

g.DrawString(regfile_R0_str, objFont1, Brushes.Green, 50, 90);

g.DrawString(regfile_R1_str, objFont1, Brushes.Green, 50, 105);

g.DrawString(regfile_Port_str, objFont1, Brushes.Green, 50, 120);

}

private void draw_pc(Graphics g, int x, int y)

{

Pen p = new Pen(Color.Black, 2);

Point[] ps = {new Point(10+x, 10+y), new Point(140+x, 10+y),

new Point(140+x, 40+y), new Point(10+x, 40+y)};

//愜傟慄傪堷偔

g.DrawPolygon(p, ps);

Font objFont1 = new Font("俵俽 俹僑僔僢僋", 12);

string str;

str = "PC=";

str += current_pc.ToString("d2");

g.DrawString(str, objFont1, Brushes.Blue, 10, 20);

string lc_str="LC=";

lc_str += loop_counter.ToString("x4");

Font objFont2 = new Font("俵俽 俹僑僔僢僋", 10);

g.DrawString(lc_str, objFont2, Brushes.Blue, 80, 45);

if (checkedListBox1.Items.Count > current_pc)

{

checkedListBox1.SetSelected(current_pc , true);

}

string clock_str = "Total "+clock.ToString("x4") +"Clocks";

g.DrawString(clock_str, objFont1, Brushes.Brown, 145, 5);

}

private void paint(object sender, PaintEventArgs e)

{

Graphics g = e.Graphics;

Pen p = new Pen(Color.Black, 2);

draw_regfile(g, 30, 30);

g.DrawLine(p, 90, 160, 90, 230);

g.DrawLine(p, 200, 160, 200, 230);

draw_alu(g,30,200);

g.DrawLine(p, 150, 330, 150, 360);

g.DrawLine(p, 150, 360, 290, 360);

g.DrawLine(p, 290, 360, 290, 30);

g.DrawLine(p, 290, 30, 150, 30);

g.DrawLine(p, 150, 30, 150, 60);

}

protected override void WndProc(ref Message m)

{

const int WM_CLOSE = 0x0010;

const int WM_ENDSESSION = 0x16;

const int WM_SYSCOMMAND = 0x112;

const int SC_CLOSE = 0xF060;

const int WM_COMMAND = 0x111;

const int WM_SIZE = 0x0005;

switch (m.Msg)

{

case WM_ENDSESSION:

//OS偺僔儍僢僩僟僂儞偱暵偠傜傟傛偆偲偟偰偄傞

//Console.WriteLine("WM_ENDSESSION");

break;

case WM_SYSCOMMAND:

//if (m.WParam.ToInt32() == SC_CLOSE)

//X儃僞儞丄僐儞僩儘乕儖儊僯儏乕偺乽暵偠傞乿丄

//僐儞僩儘乕儖儃僢僋僗偺僟僽儖僋儕僢僋丄

//Atl+F4側偳偵傛傝暵偠傜傟傛偆偲偟偰偄傞

// Console.WriteLine("SC_CLOSE");

break;

case WM_CLOSE:

//Application.Exit埲奜偱暵偠傜傟傛偆偲偟偰偄傞

//Console.WriteLine("WM_CLOSE");

break;

case WM_SIZE:

pictureBox1.Refresh();

pictureBox2.Refresh();

break;

case WM_COMMAND:

wp = (int)m.WParam;

lp = (int)m.LParam;

clock++;

draw_values();

pictureBox1.Refresh();//嵞僪儘乕

pictureBox2.Refresh();

break;

}

base.WndProc(ref m);//base偺屻偵彂偒姺偊側偄偲偩傔

if (m.Msg==WM_COMMAND && wp == 0)//偙偺屻$stop偡傞偺偱丄偙偺僐儅儞僪偼嵟屻偵憲傞偙偲

{

if (checkedListBox1.Items.Count > current_pc)

{

if (checkedListBox1.GetItemChecked(current_pc))//Breakpoint僠僃僢僋偑On側傜

{

m.Result = (IntPtr)(-1);//Mark As breakpoint

}

}

}

}

private void paint_picture_box2(object sender, PaintEventArgs e)

{

Graphics g = e.Graphics;

Pen p = new Pen(Color.Black, 2);

draw_pc(g, 0, 0);

}

private void StepButton(object sender, EventArgs e)

{

const int WM_COMMAND = 0x111;

int veritakwin_handle=FindWindow(0,"VeritakWin");

if (veritakwin_handle !=0) {//VeritakWin偑懚嵼偡傞側傜

PostMessage(veritakwin_handle,WM_COMMAND,133,0);//GO丂Command 傪VeritakWin偵憲傞

}

}

private void checkedListBox1_double_click(object sender, MouseEventArgs e)

{

}

private void Stop_Button_clicked(object sender, EventArgs e)

{

const int WM_COMMAND = 0x111;

int veritakwin_handle = FindWindow(0, "VeritakWin");

if (veritakwin_handle != 0)

{//VeritakWin偑懚嵼偡傞側傜

PostMessage(veritakwin_handle, WM_COMMAND, 134, 0);//GO丂Command 傪VeritakWin偵憲傞

}

}

private void Reload_and_go_Button_clicked(object sender, EventArgs e)

{

const int WM_COMMAND = 0x111;

int veritakwin_handle = FindWindow(0, "VeritakWin");

if (veritakwin_handle != 0)

{//VeritakWin偑懚嵼偡傞側傜

PostMessage(veritakwin_handle, WM_COMMAND, 153, 0);//GO丂Command 傪VeritakWin偵憲傞

}

}

}

}

CPU 偺奼挘

偝偰丄堦墳忋偺婰弎偱摦偒傑偡偑丄傗偼傝帺暘偱偄偠偭偰傒側偄偲椙偔暘偐傜側偄偐傕偟傟傑偣傫丅惀旕丄忋傪悧宍偲偟偰丄

- 帺暘偺柦椷傪偮偔傞

- 儅僋儘僐乕僪傪掕媊偟偰傒傞

- 僾儘僌儔儉偟偰傒傞丂乮ROM僐乕僪傪彂偄偰傒傞乯

偲偄偆曄峏傪峴偭偰傒偰偔偩偝偄丅埲壓偼丄偄偔偮偐偺奼挘埬偱偡丅

- 榑棟墘嶼傪擖傟傞丂AND/OR/XOR

- 忔嶼婍傪擖傟傞

- 僶儗儖僔僼僞傪擖傟傞

傕偪傠傫丄MAX2偱摦偐偡偲側傞偲柍棟偐傕偟傟傑偣傫偑丄僔儈儏儗乕僔儑儞傪峴偆暘偵偼丄帺桼偱偡丅

偦傟偱偼丄幚嵺偵丄曄峏傪壛偊傞椺傪傗偭偰傒傑偟傚偆丅

巇條偼丄師偺僐儅儞僪傪捛壛偡傞傕偺偲偟傑偡丅ifdef 偱捛壛偟偰偄傑偡丅

ADDITIONAL_COMMAND偑define偝傟偰偄傞偲偒偵丄Enable偝傟傑偡丅偙偺傛偆偵偟偰偍偔偲丄尦偵栠偟偨偄偲偒偵曋棙偱偡丅

側傫偲丄忔嶼婍傑偱丄掕媊偟偰偟傑偄傑偟偨丅戝忎晇偱偟傚偆偐丠

師偼丄ALU偵墘嶼婰弎傪捛壛偟傑偡丅忔嶼偼丄8x8=16價僢僩晞崋側偟偵側傝傑偡丅

偦傟偐傜丄parameter 掕媊傕捛壛偟偰偍偒傑偡丅

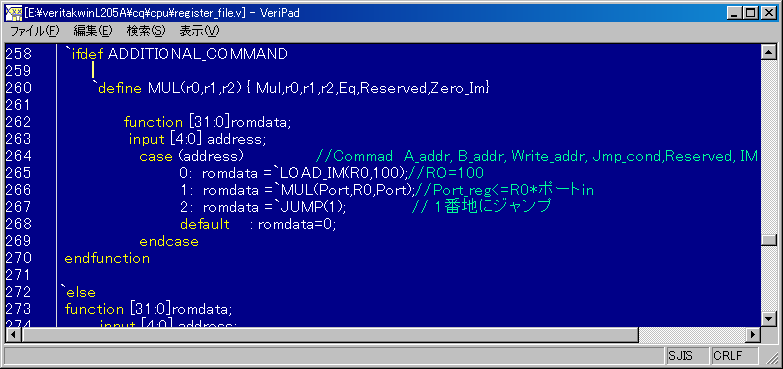

嵟屻偵ROM丂僐乕僪偱偡丅

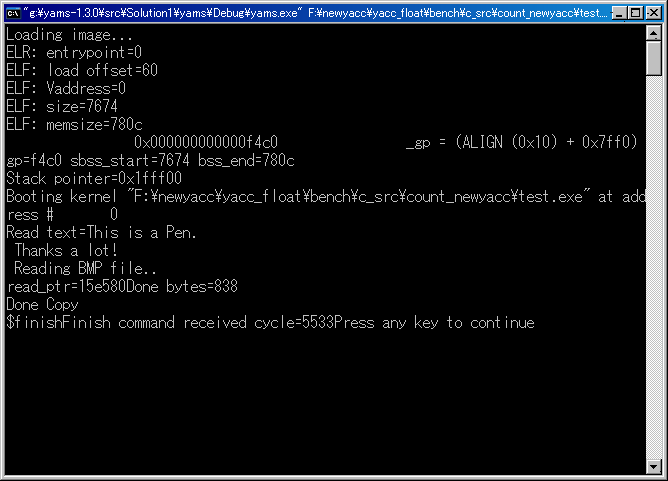

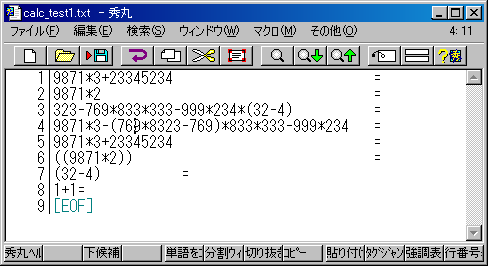

擖椡偺抣傪100攞偟偰丄弌椡億乕僩偵彂偒弌偟偰偄傑偡丅

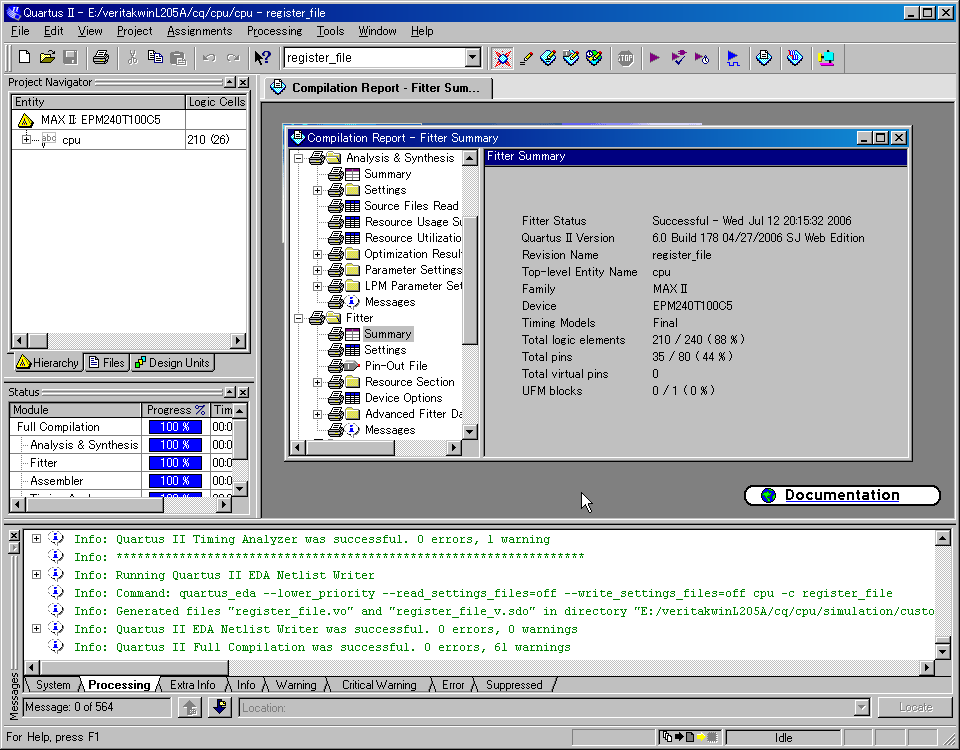

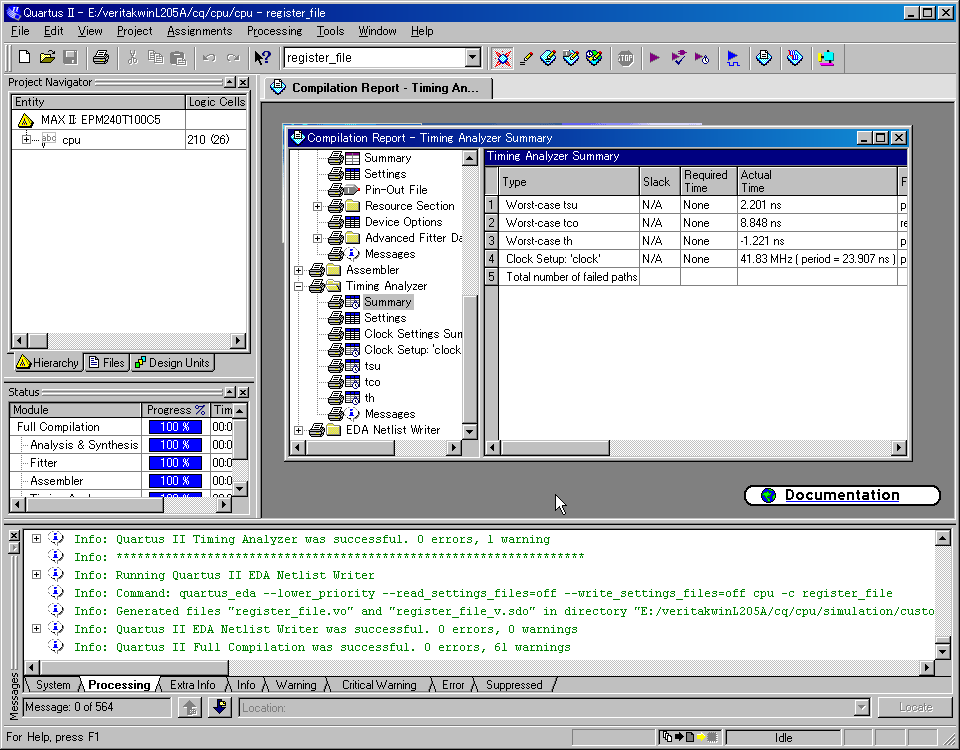

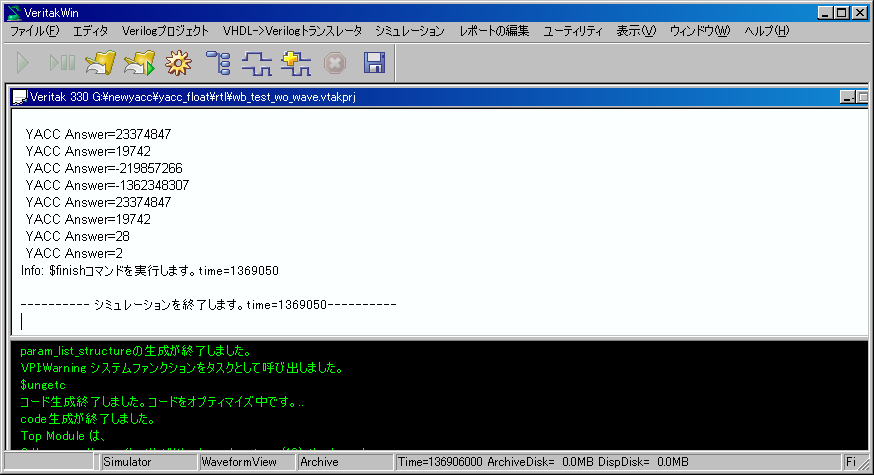

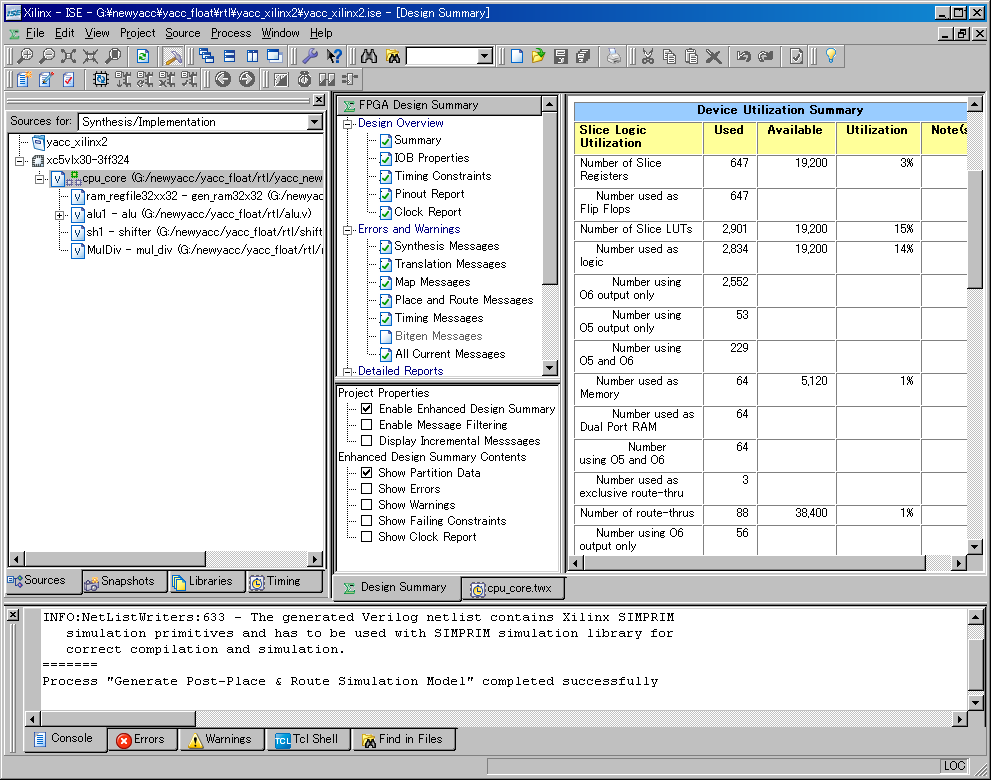

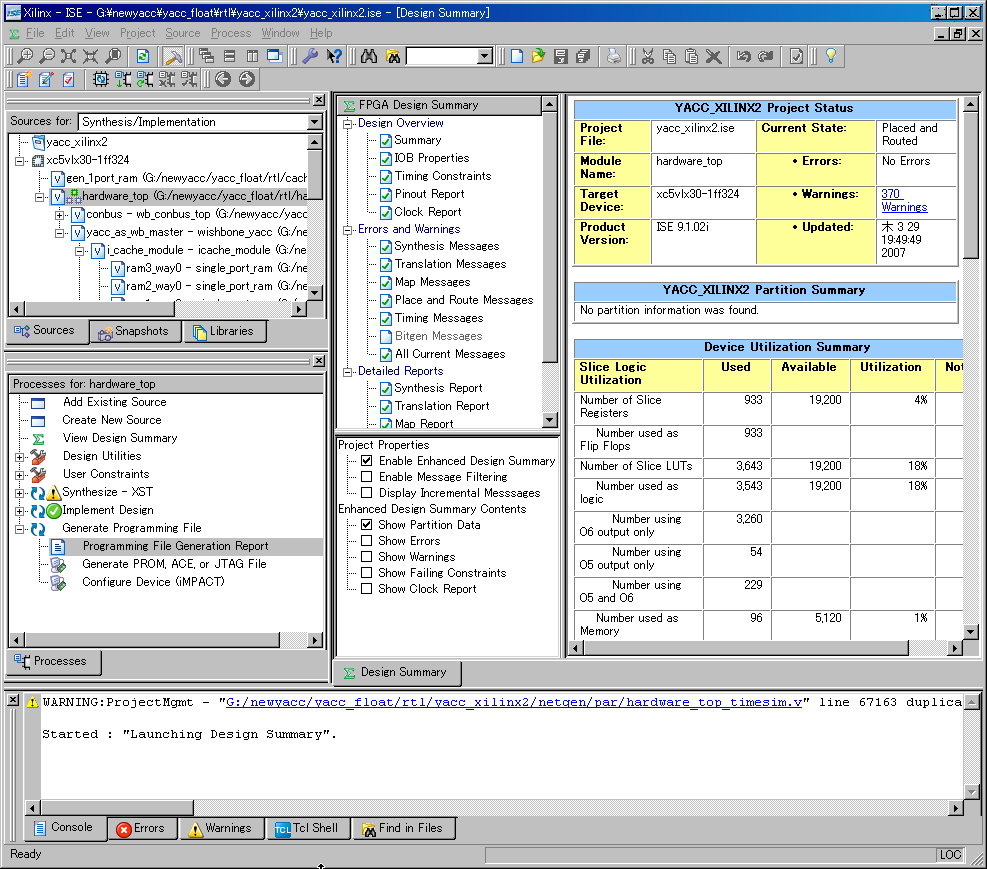

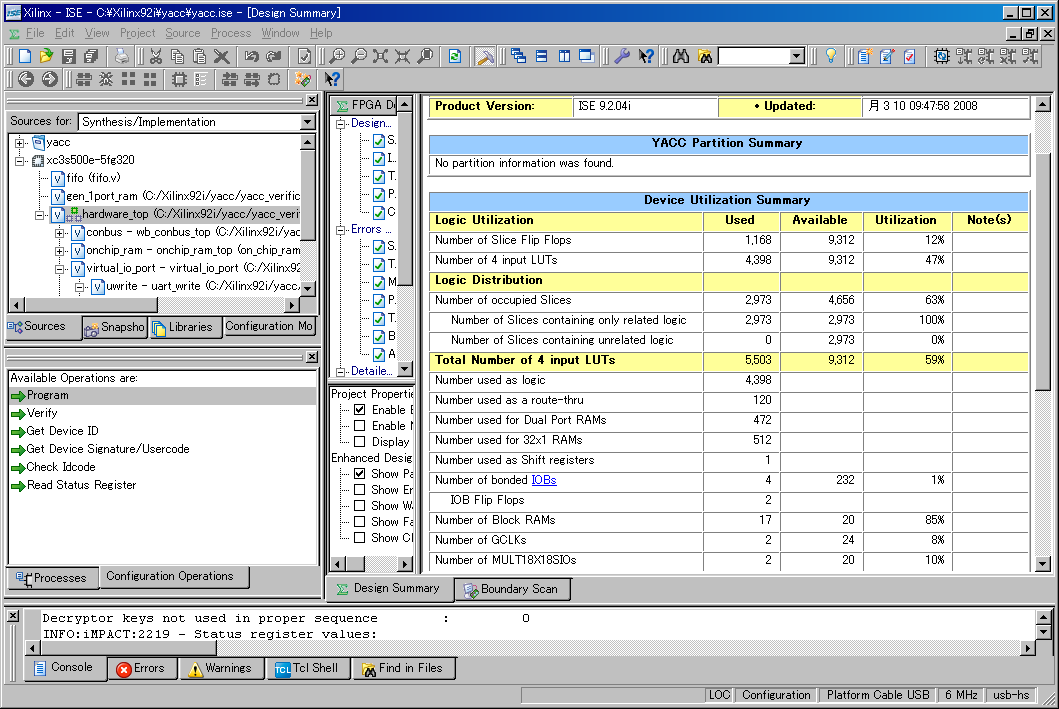

MAX2偱偺崌惉寢壥偱偡丅傆偅丄廂傑傝傑偟偨丅

41MHz偱憱傞偦偆偱偡丅

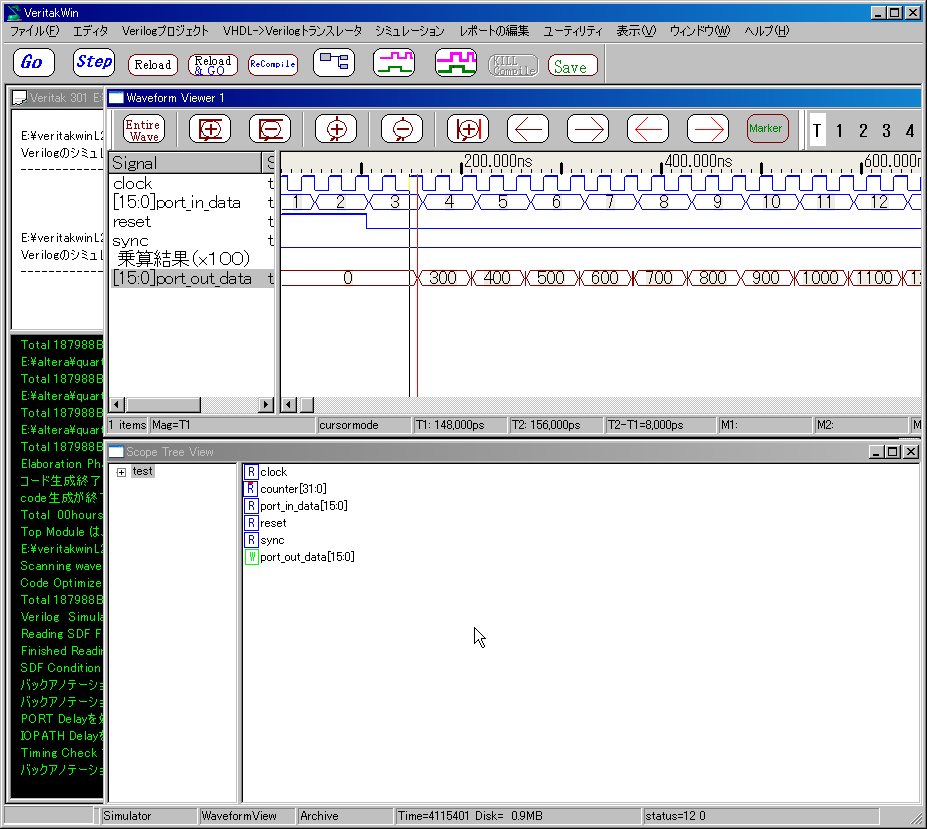

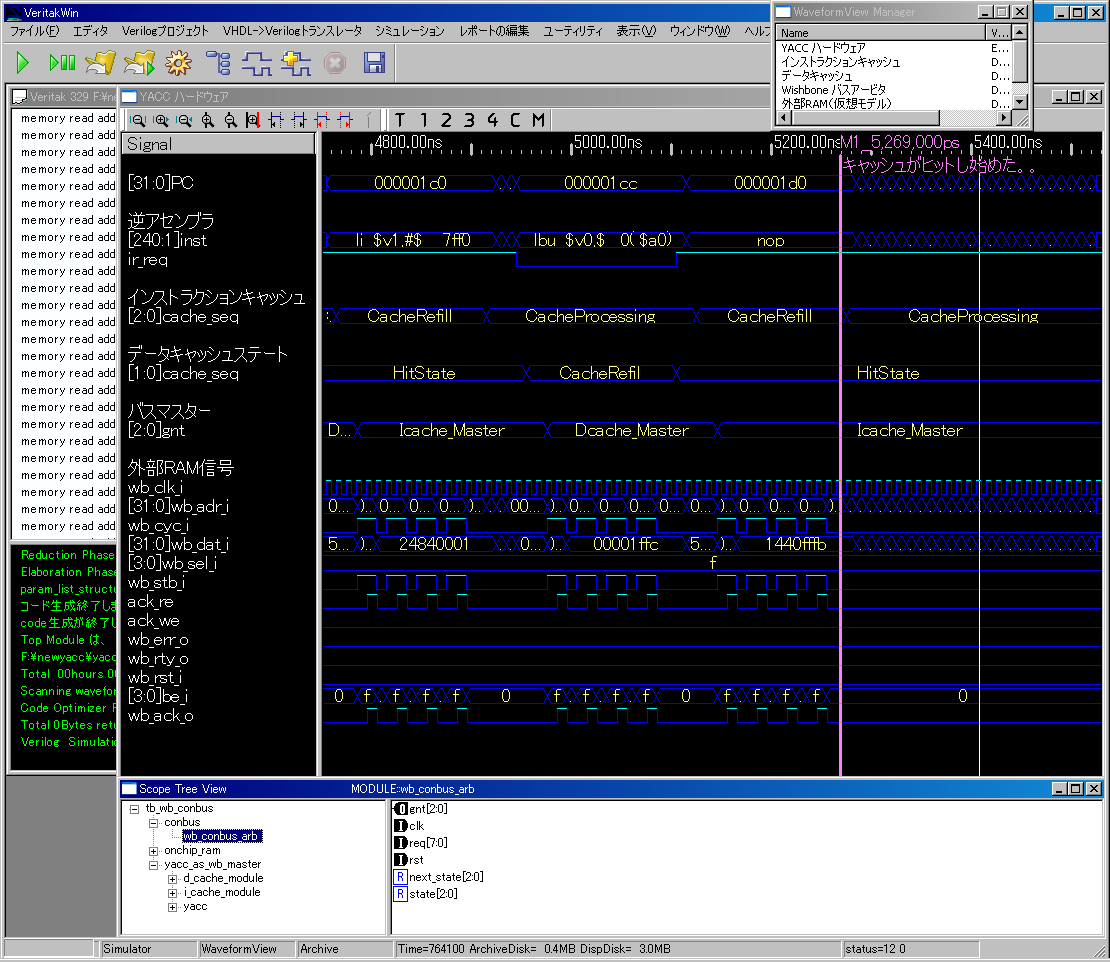

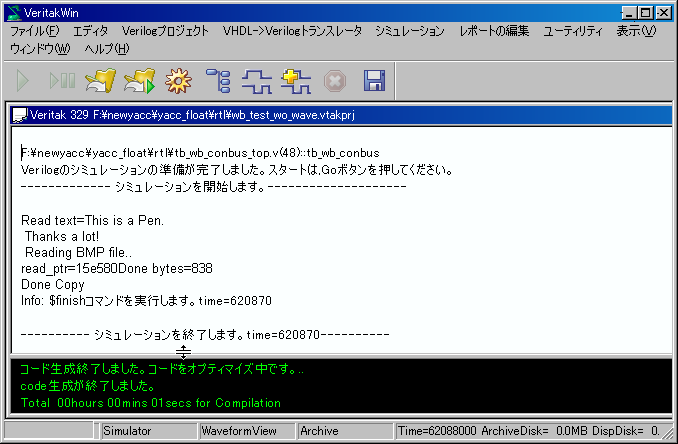

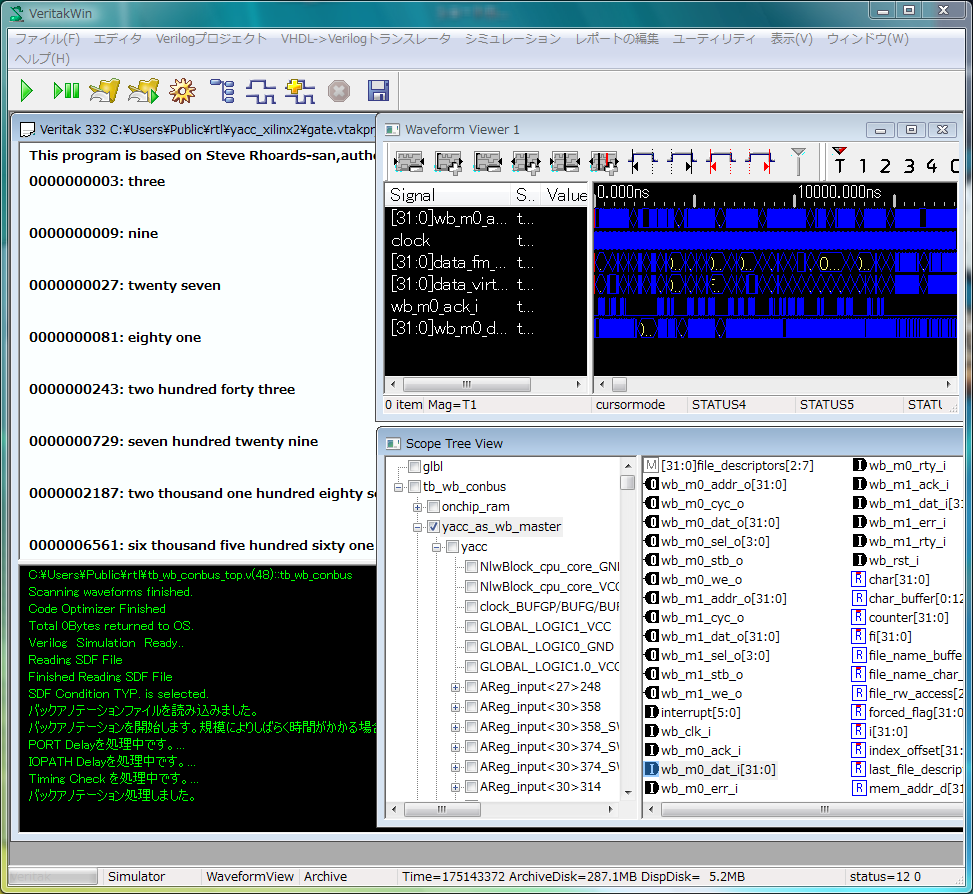

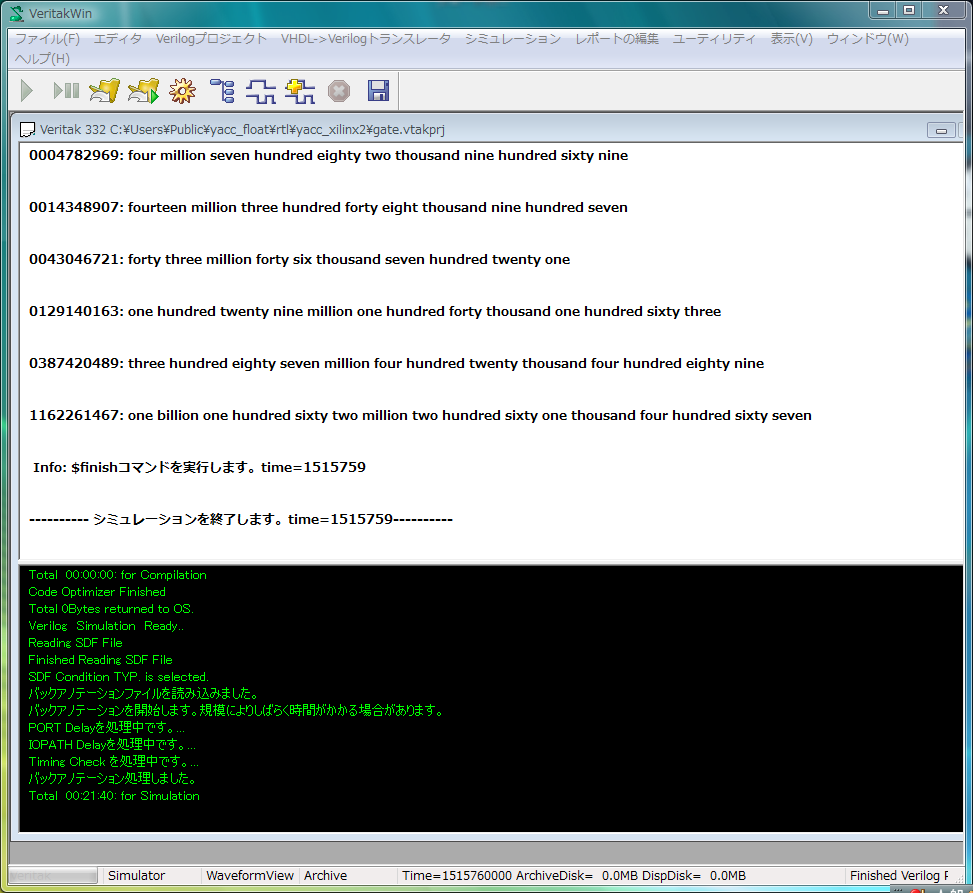

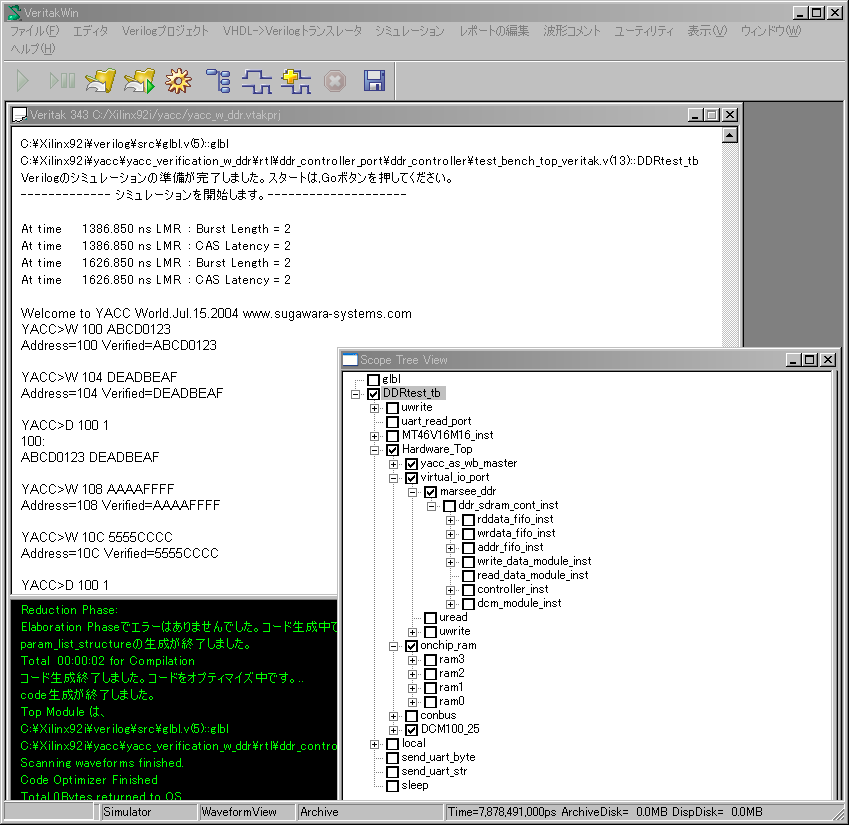

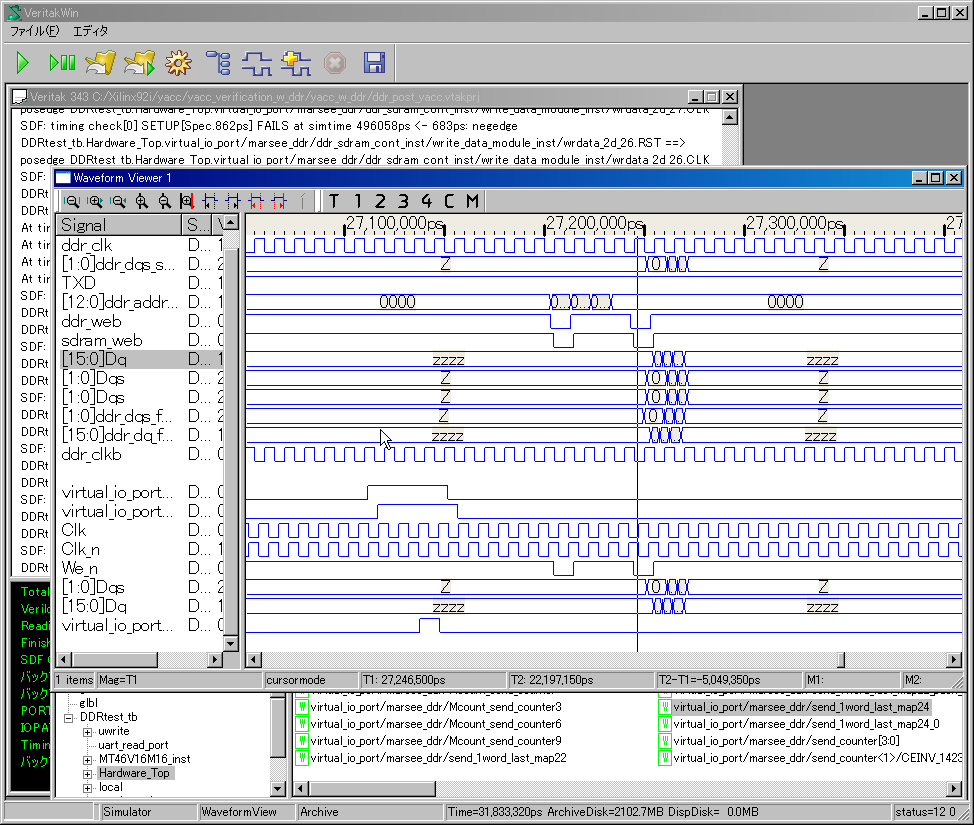

抶墑僔儈儏儗乕僔儑儞偱偡丅

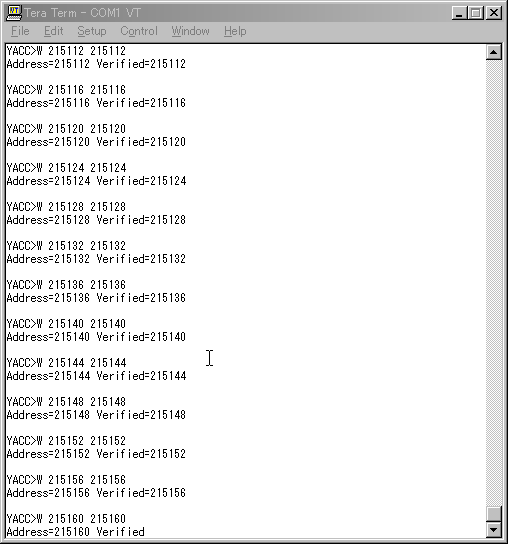

僋儘僢僋僄僢僕偐傜8ns掱搙抶傟傑偡偑丄偪傖傫偲100攞偵側偭偰曉偭偰偒傑偟偨丅

傕偆丄偙偺儅僕僢僋偼丄偍暘偐傝偱偡偹丅僴乕僪偲偟偰偺ROM傪夝愅偡傞偲ADD傗丄SUB丄偦偺懠儘僕僢僋偼巊傢傟偰偄側偄偙偲傪崌惉婍偼暘偐偭偨偺偱偟傚偆丅

偙傟傪丄弮ROM偲偟偰掕媊偟偰偟傑偆偲丄忔嶼婍偼惁偔怘偆偺偱丄摓掙嵹傜側偄偱偟傚偆丅

亙師偺奼挘傾僀僨傾亜

偲偙傠偱丄偙偺忔嶼婍偼丄JUMP偑擖偭偰偄傞偨傔偵丄俀CYCLE偐偐偭偰偟傑偭偰偄傑偡丅偙偙偵儖乕僾柦椷傪傕偭偰偔傟偽丄儖乕僾婜娫偼丄侾CYCLE偱張棟偱偒傑偡丅

偙傟偼丄儅僋儘柦椷傪掕媊偡傞偩偗偱壜擻偱偡丅埥偄偼丄JUMP柦椷偲梈崌偡傞偲偄偆傾僀僨傾傕壜擻偱偟傚偆丅柦椷偑廔傢偭偨傜忢偵僕儍儞僾偡傞偲偄偆嬶崌偱偡丅

乮IMMEDIATE柦椷傪彍偒丄偙偺僼傿乕儖僪偼丄梀傫偱偄傑偡乯岾偄丄儅僀僋儘僼傿乕儖僪偼丄枹偩2價僢僩巆偭偰偄傑偡偺偱丄偙偺價僢僩傪巊偭偰丄價僢僩偑棫偭偰偄傞偲偒偩偗丄偦偆偄偆晽偵偡傞偲偄偆偙偲傕偱偒傑偡丅

埥偄偼丄偙偺CPU傪壗屄偑暲楍偱巊偆傾僀僨傾傕偁傝偱偟傚偆丅妱傝崬傒側傫偰丄1僒僀僋儖偱張棟偱偒偰偟傑偄傑偡丅丅

僗僥乕僩儅僔儞偱偼丄暋嶨偡偓傞丄CPU偱偼抶偡偓傞偲偄偆応崌偵岲揔側僴乕僪偲僜僼僩偺拞娫傒偨偄側儅僔儞偱偡丅偙偆偄偆僴乕僪傪儅僀僋儘僔乕働儞僒偲屇傫偱偄傑偡丅

愄偺CISC儅僔儞乮俇俉侽侽侽偺帪戙乯偼丄儅僀僋儘僔乕働儞僒偱惂屼偝傟偰偄偨偲巚偄傑偡丅CPU偺拞偺CPU偦傟偑丄儅僀僋儘僔乕働儞僒偱偡丅

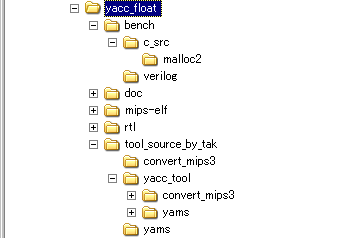

傾乕僇僀僽偱偡丅

亙斣奜曇亜

ST2偩偲偳偆側傞偐傗偭偰傒傑偟偨丅摦嶌懍搙140Mz丄儕僜乕僗2%偺徚旓偱偟偨丅

儐乕僓Contribution![]()

儐乕僓條偐傜丄奼挘椺傪偄偨偩偒傑偟偨丅

埲壓偼丄嶌幰偺曽偺僐儊儞僩偱偡丅

億乕僩擖弌椡傪柧帵揑偵暘偗偨傝丄柦椷僙僢僩傗摦嶌巇條傪

帺暘側傝偵偟偭偔傝棃傞傛偆偵曄峏偟偨傝偟偰傒傑偟偨丅

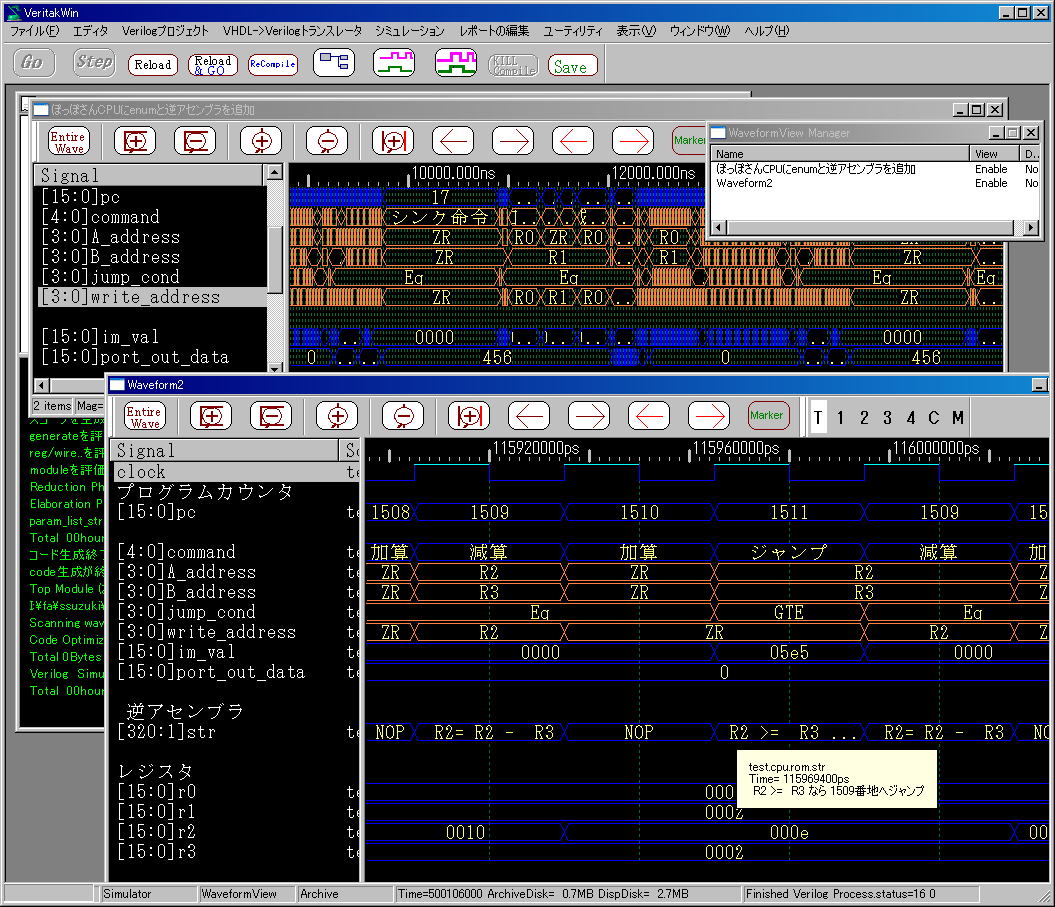

ROM偺儅僀僋儘僐乕僪偩偗尒偰偄傞偲丄傾僙儞僽儔傒偨偄(徫)

// 僶儗儖僔僼僞

1514: `SET(R0,

2);

1515: `SET(R1, 7);

1516: `SET(R2, 0);

1517: `BSHIFT_L(R0, R1,

R0);

1518: `BSHIFT_R(R0, R1, R0);

偱傕丄幚偼慻傒崌傢偣夞楬偵崌惉偝傟傞曈傝丄壗偩偐丄妝偟偄偱偡偹丅

挷巕偵忔偭偰丄柦椷偲偐憹傗偟偨傝丄

ROM弌椡偺價僢僩暆傪憹傗偟偨傝偟偰傒傑偟偨偑丄

僋儕僥傿僇儖僷僗偑塿乆挿偔側偭偰偟傑偄傑偟偨丅 丅

僜乕僗偱偡丅

// 儅僀僋儘僾儘僌儔儉曽幃 CPU

// 僱僀僥傿僽僐儅儞僪

`define ADD_com 5'b00000

`define SET_com 5'b00001

`define SUB_com 5'b00010

`define SHIFT_L_com 5'b00011

`define SHIFT_R_com 5'b00100

`define JMP_com 5'b00101

`define SYNC_com 5'b00110

`define AND_com 5'b00111

`define OR_com 5'b01000

`define XOR_com 5'b01001

`define NOT_com 5'b01010

`define MUL_com 5'b01011

`define BSHIFT_L_com 5'b01100

`define BSHIFT_R_com 5'b01101

// 僕儍儞僾忦審

`define Eq 4'b0000

`define Not_Eq 4'b0001

`define Always 4'b0010

`define LT 4'b0011

`define GT 4'b0100

`define LTE 4'b0101

`define GTE 4'b0110

// 儗僕僗僞傾僪儗僗

`define ZR 4'b0000

`define R0 4'b0001

`define R1 4'b0010

`define R2 4'b0011

`define R3 4'b0100

`define P_IN 4'b0101

`define P_OUT 4'b0110

// CPU

module cpu(input clock, reset,

input [15:0] port_in_data,

input sync,

output [15:0] port_out_data);

localparam integer Loop_counter_width=16;

localparam integer Stop_count = 2**Loop_counter_width -1;

reg [Loop_counter_width-1:0] loop_counter;

reg [15:0] pc;

// reg [15:0] port_in_reg;

reg sync_ff, sync_ff2;

/*----------------------------------------------------------------------------

ROM儚僀儎乕儅僢僾

價僢僩埵抲 價僢僩暆 撪梕

39:35 5 柦椷

34:31 4 儗僕僗僞僼傽僀儖A億乕僩偺傾僪儗僗

30:27 4 儗僕僗僞僼傽僀儖B億乕僩偺傾僪儗僗

26:23 4 儗僕僗僞僼傽僀儖儔僀僩億乕僩偺傾僪儗僗

22:19 4 僕儍儞僾斾妑忦審

18:16 3 彨棃奼挘梡

16:16 1 loop_flag 儖乕僾張棟偡傞偐偳偆偐偺僼儔僌丄侾偱儖乕僾張棟

15:0 16 懄抣傑偨偼丄旘傃愭

-----------------------------------------------------------------------------*/

wire [39:0] rom_data;

wire [4:0] command = rom_data[39:35];

wire [3:0] A_address = rom_data[34:31];

wire [3:0] B_address = rom_data[30:27];

wire [3:0] write_address = rom_data[26:23];

wire [3:0] jump_cond = rom_data[22:19];

wire [2:0] reserved = rom_data[18:16];

wire [15:0] immediate_data = rom_data[15:0];

wire loop_flag = reserved[0];

wire [15:0] out_dataA, out_dataB;

wire [15:0] alu_data;

// SET僐儅儞僪偺帪偼丄"A億乕僩偵戙擖偡傞抣" 傪愙懕偡傞丅

// 仸 ALU偱 僛儘儗僕僗僞偲壛嶼偟偰戙擖偡傞帠偱丄SET傪幚尰偡傞堊丅

wire [15:0] Aport_data = (command==`SET_com) ? immediate_data : port_in_data;

//儖乕僾僇僂儞僞儕僙僢僩忦審

wire Reset_loop_counter = (loop_counter<2)||

(loop_counter==Stop_count && immediate_data == 16'b0)

? 1 : 0;

//儖乕僾僇僂儞僞偺張棟

always @(posedge clock, posedge reset) begin

if(reset)

begin

loop_counter <= Stop_count;

end

else if(Reset_loop_counter)

begin

loop_counter <= Stop_count;

end

else if(loop_flag && loop_counter==Stop_count)

begin

// 儖乕僾僇僂儞僩抣傪僙僢僩

loop_counter <= immediate_data;

end

//else if ((loop_flag) && (loop_counter>1))

else if(loop_flag)

begin

// 儖乕僾張棟

loop_counter <= loop_counter - 16'b1;

end

else

begin

loop_counter <= Stop_count;

end

end

// 擖椡摨婜僄僢僕専弌

always @(posedge clock, posedge reset) begin

if (reset) sync_ff<=0;

else sync_ff<=sync;

end

always @(posedge clock, posedge reset) begin

if (reset) sync_ff2<=0;

else sync_ff2<=sync_ff;

end

// 棫偪忋偑傝僄僢僕傪専弌

wire sync_pos_edge_detected = sync_ff & ~sync_ff2;

// 儅僀僋儘僾儘僌儔儉僇僂儞僞

always @(posedge clock, posedge reset) begin

if(reset)

begin

pc <= 0;

end

// 僕儍儞僾柦椷張棟

else if(command==`JMP_com && alu_data[0]==1'b1)

begin

//旘傫偱偄偗

pc <= immediate_data;

end

else if(command==`SYNC_com)

begin //摨婜懸偪僗僞乕僩張棟

if(sync_pos_edge_detected)

begin

//摨婜怣崋傪専弌丅師偺傾僪儗僗傪幚峴奐巒丅

pc <= pc + 1;

end

else

begin

//摨婜僄僢僕偑棃傞傑偱懸偮

pc <= pc;

end

end

else if(loop_flag)

begin //儖乕僾張棟

if(Reset_loop_counter)

begin

//儖乕僾張棟偐傜敳偗傞

pc <= pc + 1;

end

else

begin

//僟僂儞僇僂儞僩拞偼懸偮

pc <= pc;

end

end

else

begin

// 壗傕側偄帪偼師偺傾僪儗僗傪幚峴奐巒

pc <= pc + 1;

end

end

/*

//input reg

always @(posedge clock, posedge reset)

begin

if(reset)

begin

port_in_reg<=0;

end

else

begin

port_in_reg<=port_in_data;

end

end

*/

// 儗僕僗僞僼傽僀儖

register_file register_file(.clock(clock),

.reset(reset),

.A_address(A_address),

.B_address(B_address),

.write_address(write_address),

.alu_data(alu_data),

.out_dataA(out_dataA),

.out_dataB(out_dataB),

.port_in_data(Aport_data),

.port_out_data(port_out_data));

// ALU

alu alu(.command(command),

.jump_cond(jump_cond),

.portA(out_dataA),

.portB(out_dataB),

.alu_out(alu_data));

// ROM

rom rom(.rom_address(pc),.Data(rom_data));

endmodule

// 儗僕僗僞僼傽僀儖

// 婰壇慺巕傪儗僕僗僞偺廤傑傝偲偟偰丄傑偲傔偰儌僕儏乕儖壔丅

// 摨帪偵撉傒彂偒偱偒傞億乕僩偑俁偮

// 儔僀僩億乕僩偑侾偮丄儕乕僪億乕僩偑俀偮丅

module register_file(input clock,

input reset,

input [3:0] A_address,

input [3:0] B_address,

input [3:0] write_address,

input [15:0] alu_data, port_in_data,

output [15:0] out_dataA, out_dataB, port_out_data);

// CPU儗僕僗僞

reg [15:0] p_out_reg, r0, r1, r2, r3;

// 億乕僩傾僂僩儗僕僗僞

always @(posedge clock, posedge reset) begin

if(reset)

begin

p_out_reg <= 0;

end

else if(write_address == `P_OUT)

begin

p_out_reg <= alu_data;

end

else

begin

p_out_reg <= p_out_reg;

end

end

// 斈梡儗僕僗僞R0

always @(posedge clock, posedge reset) begin

if(reset)

begin

r0 <= 0;

end

else if(write_address == `R0)

begin

r0 <= alu_data;

end

else

begin

r0 <= r0;

end

end

// 斈梡儗僕僗僞R1

always @(posedge clock, posedge reset) begin

if(reset)

begin

r1 <= 0;

end

else if(write_address == `R1)

begin

r1 <= alu_data;

end

else

begin

r1 <= r1;

end

end

// 斈梡儗僕僗僞R2

always @(posedge clock, posedge reset) begin

if(reset)

begin

r2 <= 0;

end

else if(write_address == `R2)

begin

r2 <= alu_data;

end

else

begin

r2 <= r2;

end

end

// 斈梡儗僕僗僞R3

always @(posedge clock, posedge reset) begin

if(reset)

begin

r3 <= 0;

end

else if(write_address == `R3)

begin

r3 <= alu_data;

end

else

begin

r3 <= r3;

end

end

// A億乕僩弌椡(ALU傊)

assign out_dataA = (A_address==`P_OUT) ? p_out_reg :

(A_address==`P_IN) ? port_in_data :

(A_address==`R0) ? r0 :

(A_address==`R1) ? r1 :

(A_address==`R2) ? r2 :

(A_address==`R3) ? r3 : 16'b0;

// B億乕僩弌椡(ALU傊)

assign out_dataB = (B_address==`P_OUT) ? p_out_reg :

(B_address==`P_IN) ? port_in_data :

(B_address==`R0) ? r0 :

(B_address==`R1) ? r1 :

(B_address==`R2) ? r2 :

(B_address==`R3) ? r3 : 16'b0;

// 弌椡億乕僩(偦偺傑傑弌椡)

assign port_out_data = p_out_reg;

endmodule

// ALU

module alu(input [4:0] command,

input [3:0] jump_cond,

input [15:0] portA,portB,

output reg [15:0] alu_out);

always @(*) begin

case (command)

`ADD_com: alu_out=portA+portB;

`SUB_com: alu_out=portA-portB;

`SHIFT_L_com: alu_out=portB << 1;

`SHIFT_R_com: alu_out=portB >> 1;

`BSHIFT_L_com:alu_out=portA << portB;

`BSHIFT_R_com:alu_out=portA >> portB;

`MUL_com: alu_out=portA * portB;

`AND_com: alu_out=portA & portB;

`OR_com: alu_out=portA | portB;

`XOR_com: alu_out=portA ^ portB;

`NOT_com: alu_out=~portA;

`JMP_com:

case (jump_cond)

`Eq: alu_out=(portA == portB);

`Not_Eq: alu_out=(portA != portB);

`Always: alu_out=1;

`LT: if (portA < portB)

alu_out=1;

else

alu_out=0;

`GT: if (portA > portB)

alu_out=1;

else

alu_out=0;

`LTE: if (portA <= portB)

alu_out=1;

else

alu_out=0;

`GTE: if (portA >= portB)

alu_out=1;

else

alu_out=0;

default: alu_out=0;

endcase

default: alu_out=portA+portB;

endcase

end

endmodule

module rom(input [15:0] rom_address,

output [39:0] Data);

assign Data = romdata(rom_address);

//TAK start

wire [4:0] command = Data[39:35];

wire [3:0] A_address = Data[34:31];

wire [3:0] B_address = Data[30:27];

wire [3:0] write_address = Data[26:23];

wire [3:0] jump_cond = Data[22:19];

wire [15:0] im_val=Data[15:0];

wire [2:0] loop_cond=Data[18:16];

//TAK end

// 僐儅儞僪

parameter [4:0] Set=`SET_com,

Add=`ADD_com,

Sub=`SUB_com,

Shift_L=`SHIFT_L_com,

Shift_R=`SHIFT_R_com,

Jmp=`JMP_com,

Sync=`SYNC_com,

Mul=`MUL_com,

And=`AND_com,

Or =`OR_com,

Xor=`XOR_com,

Not=`NOT_com,

BShift_L=`BSHIFT_L_com,

BShift_R=`BSHIFT_R_com;

parameter [4:0] \僙僢僩 =`SET_com,

\壛嶼 =`ADD_com,

\尭嶼 =`SUB_com,

\嵍僔僼僩 =`SHIFT_L_com,

\塃僔僼僩 =`SHIFT_R_com,

\僕儍儞僾 =`JMP_com,

\僔儞僋柦椷 =`SYNC_com,

\忔嶼 =`MUL_com,

\仌 =`AND_com,

\OR =`OR_com,

\XOR =`XOR_com,

\NOT =`NOT_com,

\嵍僶儗儖僔僼僩 =`BSHIFT_L_com,

\塃僶儗儖僔僼僩 =`BSHIFT_R_com;

// 儗僕僗僞傾僪儗僗

parameter [3:0] P_OUT=`P_OUT,//IO億乕僩弌椡

P_IN=`P_IN, //IO億乕僩擖椡

R0= `R0,

R1= `R1,

R2= `R2,

R3= `R3,

ZR= `ZR; // 僛儘儗僕僗僞 (= 僛儘GND)

// 僕儍儞僾忦審

parameter [3:0] Eq=`Eq,

Not_Eq=`Not_Eq,

Always=`Always,

LT=`LT,

GT=`GT,

LTE=`LTE,

GTE=`GTE;

// 儖乕僾張棟

parameter [2:0] Reserved = 3'b000,

LoopEnabled = 3'b001;

// 儅僋儘柦椷

// NOP

`define NOP romdata={Add,ZR,ZR,ZR,Eq,Reserved,16'h 0000}

// 僐僺乕 : r0 仺 r1

`define MOV(r0,r1) romdata={Add,r0,ZR,r1,Eq,Reserved,16'h 0000}

// 僋儕傾 : r0 = 0

`define CLR(r0) romdata={Add,ZR,ZR,r0,Eq,Reserved,16'h 0000}

// 掕悢戙擖 : r0 = num

`define SET(r0,num) romdata={Set,P_IN,ZR,r0,Eq,Reserved,16'd num}

// 僕儍儞僾

`define JUMP(num) romdata={Jmp,ZR,ZR,ZR,Always,Reserved,16'd num}

// 榑棟斀揮

`define NOT(r0,r1) romdata={Not,r0,ZR,r1,Always,Reserved,16'h 0000}

// 懌偟嶼 : r2 = r0 + r1

`define ADD(r0,r1,r2) romdata={Add,r0,r1,r2,Eq,Reserved,16'h 0000}

// 堷偒嶼 : r2 = r0 - r1

`define SUB(r0,r1,r2) romdata={Sub,r0,r1,r2,Eq,Reserved,16'h 0000}

// 忔嶼 : r2 = r0 * r1

`define MUL(r0,r1,r2) romdata={Mul,r0,r1,r2,Eq,Reserved,16'h 0000}

// 忦審暥 : if(r0<r1) goto num;

`define JUMP_IF_LT(r0,r1,num) romdata={Jmp,r0,r1,ZR,LT,Reserved,16'd num}

// 忦審暥 : if(r0>r1) goto num;

`define JUMP_IF_GT(r0,r1,num) romdata={Jmp,r0,r1,ZR,GT,Reserved,16'd num}

// 忦審暥 : if(r0<=r1) goto num;

`define JUMP_IF_LTE(r0,r1,num) romdata={Jmp,r0,r1,ZR,LTE,Reserved,16'd num}

// 忦審暥 : if(r0>=r1) goto num;

`define JUMP_IF_GTE(r0,r1,num) romdata={Jmp,r0,r1,ZR,GTE,Reserved,16'd num}

// 忦審暥 : if(r0==r1) goto num;

`define JUMP_IF_EQ(r0,r1,num) romdata={Jmp,r0,r1,ZR,Eq,Reserved,16'd num}

// 1價僢僩僔僼僩

`define SHIFT_L(r0,r1) romdata={Shift_L,ZR,r0,r1,Eq,Reserved,16'h 0000}

`define SHIFT_R(r0,r1) romdata={Shift_R,ZR,r0,r1,Eq,Reserved,16'h 0000}

// 僶儗儖僔僼僩

`define BSHIFT_L(r0,r1,r2) romdata={BShift_L,r0,r1,r2,Eq,Reserved,16'h 0000}

`define BSHIFT_R(r0,r1,r2) romdata={BShift_R,r0,r1,r2,Eq,Reserved,16'h 0000}

// 奜晹擖椡丒棫偪忋偑傝僄僢僕傑偱懸偮

`define SYNC romdata={Sync,ZR,ZR,ZR,Eq,Reserved,16'h 0000}

// 儖乕僾孞傝曉偟柦椷(JUMP柦椷暘偺1僋儘僢僋傪愡栺)

// ex : r2 = r0 + r1 傪 num+1 夞孞傝曉偡丅偦偺娫丄pc 偼 尰傾僪儗僗偱懸婡丅

`define ADD_LOOP(r0,r1,r2,num) romdata={Add,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define SUB_LOOP(r0,r1,r2,num) romdata={Sub,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define MUL_LOOP(r0,r1,r2,num) romdata={Mul,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define SHIFT_L_LOOP(r0,num) romdata={Shift_L,ZR,r0,r0,Eq,LoopEnabled,16'd num}

`define SHIFT_R_LOOP(r0,num) romdata={Shift_R,ZR,r0,r0,Eq,LoopEnabled,16'd num}

//Tak start 丂媡傾僙儞僽儔

reg [8*40:1] str;

function [8*3:1] get_rn(input [3:0] addr);

case (addr)

P_OUT: get_rn="OUT";

P_IN: get_rn="IN"; //IO億乕僩擖椡

R0: get_rn="R0";

R1: get_rn="R1";

R2: get_rn="R2";

R3: get_rn="R3";

ZR: get_rn="ZR"; // 僛儘儗僕僗僞 (= 僛儘GND)

default: get_rn="???";

endcase

endfunction

always @* begin

case (command)

Add:

if(loop_cond==0) begin

if (A_address==ZR && B_address==ZR & write_address==ZR) $sformat(str,"NOP");

else if (B_address==ZR && A_address==ZR ) $sformat(str,"%s傪僋儕傾",get_rn(write_address));

else if (B_address==ZR ) $sformat(str,"%s偐傜%s傊僐僺乕",get_rn(A_address),get_rn(write_address));

else $sformat(str,"%s=%s + %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else begin

if (A_address==ZR && B_address==ZR & write_address==ZR) $sformat(str,"NOP %d儖乕僾晅",im_val);

else if (B_address==ZR && A_address==ZR ) $sformat(str,"%s傪僋儕傾丂 %d儖乕僾晅",get_rn(write_address),im_val);

else if (B_address==ZR ) $sformat(str,"%s偐傜%s傊僐僺乕丂 %d儖乕僾晅",get_rn(A_address),get_rn(write_address),im_val);

else $sformat(str,"%s=%s + %s %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

end

Set: $sformat(str,"%s=%h[Hex]",get_rn(write_address),im_val);

Mul:

if (loop_cond==0) begin

$sformat(str,"%s=%s * %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else $sformat(str,"%s=%s * %s 丂 %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

Sub:

if (loop_cond==0) begin

$sformat(str,"%s=%s - %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else $sformat(str,"%s=%s - %s %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

Sync:

$sformat(str,"僔儞僋柦椷");

Not: $sformat(str,"%s=~%s",get_rn(write_address),get_rn(A_address));

Jmp:

if (jump_cond==Always) $sformat(str,"%d斣抧傊僕儍儞僾",im_val);

else if (jump_cond==LT) $sformat(str,"%s < %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==GT) $sformat(str,"%s > %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==LTE) $sformat(str,"%s <= %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==GTE) $sformat(str,"%s >= %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==Eq) $sformat(str,"%s == %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

Shift_L:

if (loop_cond==0) $sformat(str,"%s=%s << 1",get_rn(write_address),get_rn(B_address));

else $sformat(str,"%s=%s << %d",get_rn(write_address),get_rn(B_address),im_val);

Shift_R:

if (loop_cond==0) $sformat(str,"%s=%s >> 1",get_rn(write_address),get_rn(B_address));

else $sformat(str,"%s=%s >> %d",get_rn(write_address),get_rn(B_address),im_val);

BShift_L:

$sformat(str,"%s=%s <<%s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

BShift_R:

$sformat(str,"%s=%s >> %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

endcase

end

//Tak end

// 儅僀僋儘僐乕僪

function [39:0]romdata;

input [15:0] address;

case(address)

//Commad A_addr, B_addr, Write_addr, Jmp_cond, Reserved, IM

0: `SET(P_OUT, 100);

1: `SET(R0, 5);

2: `MOV(R0, R1);

3: `MOV(R1, R2);

4: `MOV(R2, R3);

5: `SUB(R1, R2, R0);

6: `SUB(R3, R1, R3);

7: `ADD(P_IN, P_OUT, P_OUT);

8: `ADD(P_OUT, P_OUT, P_OUT);

9: `SUB(P_IN, P_IN, R1);

10: `SUB(P_OUT, P_IN, R2);

11: `SET(R0, 2);

12: `SET(R1, 8);

13: `MUL(R0, R1, R3);

14: `NOP;

15: `MUL(R3, R3, R3);

16: `ADD(P_OUT, R3, P_OUT);

17: `SYNC;

18: `JUMP(1000);

// 僔僼僩丒忔嶼

1000: `SET(R0, 5);

1001: `SET(R1, 2);

1002: `ADD_LOOP(R0, R1, R0, 10);

1003: `SHIFT_L_LOOP(R1, 5);

1004: `SHIFT_R_LOOP(R1, 5);

1005: `SUB_LOOP(R0, R1, R0, 10);

1006: `SET(P_OUT, 5);

1007: `MUL_LOOP(P_OUT, R1, P_OUT, 7);

1008: `JUMP(1500);

// 忦審暥

1500: `SET(R0, 16);

1501: `SET(R1, 2);

1502: `SET(P_OUT, 0);

1503: `SUB(R0, R1, R0);

1504: `JUMP_IF_GT(R0, R1 ,1503);

// 忦審暥

1505: `SET(R2, 16);

1506: `SET(R3, 2);

1507: `SET(P_OUT, 0);

1509: `SUB(R2, R3, R2);

1511: `JUMP_IF_GTE(R2, R3 ,1509);

// 1010_1010_1010_1010

// 價僢僩斀揮

1512: `SET(R0, 43690);

1513: `NOT(R0, R1);

// 僶儗儖僔僼僞

1514: `SET(R0, 2);

1515: `SET(R1, 7);

1516: `SET(R2, 0);

1517: `BSHIFT_L(R0, R1, R0);

1518: `BSHIFT_R(R0, R1, R0);

1519: `JUMP(0);

default: romdata = 0;

endcase

endfunction

endmodule

傾乕僇僀僽偱偡丅

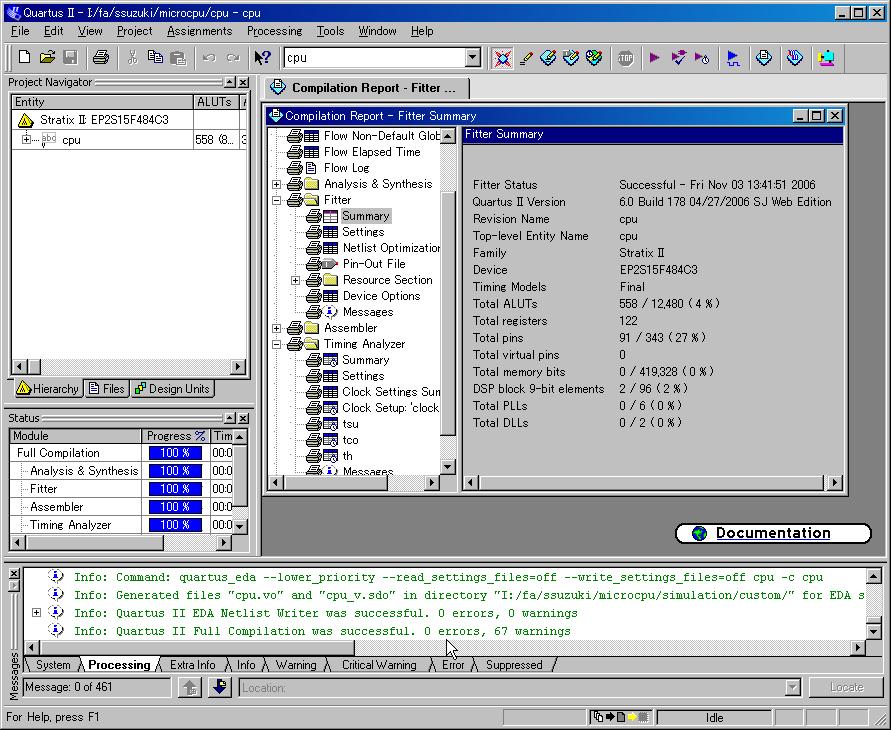

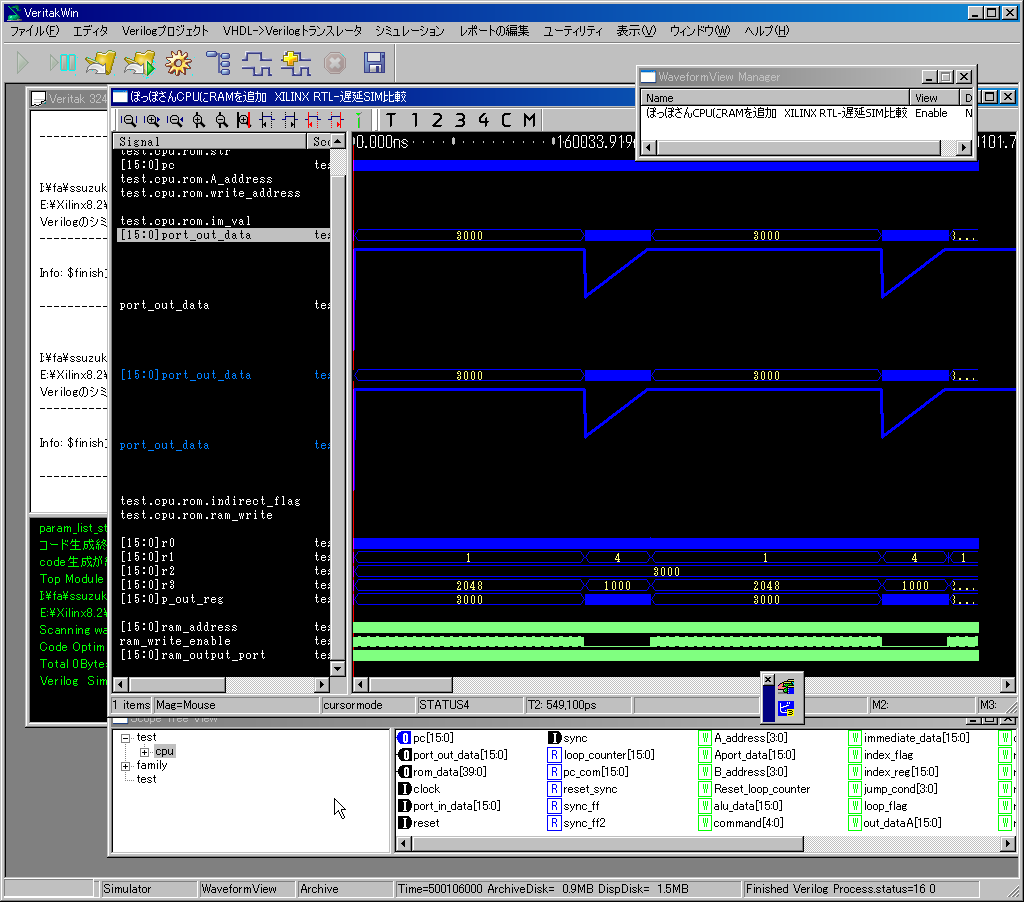

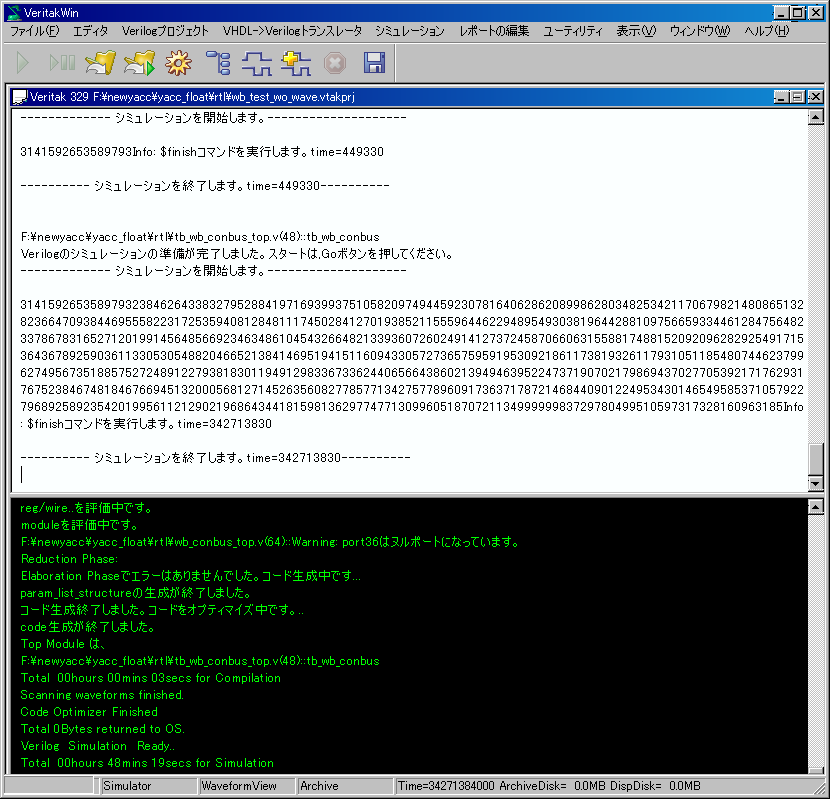

側偍丄婰弎偺摦嶌妋擣偲偟偰Quartas嘦偱崌惉傪偟偰傒傑偟偨丅僨僶僀僗偼Stratix2

懍搙偼丄72MHz偱偟偨丅

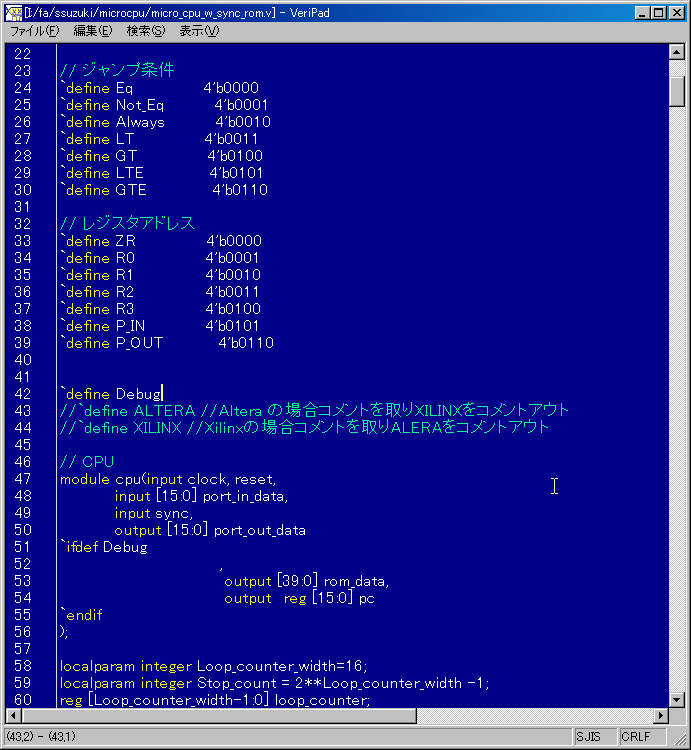

撪晹摦嶌偺妋擣傪偟偨偄堊偵丄pc偲rom_data傪堷偒弌偟偰偄傑偡丅

`Debug 偱丄愗傝懼偊偟偰偄傑偡丅

`define Debug

// CPU

module cpu(input clock, reset,

input [15:0] port_in_data,

input sync,

output [15:0] port_out_data

`ifdef Debug

,

output [39:0] rom_data,

output reg [15:0] pc

`endif

);

localparam integer Loop_counter_width=16;

localparam integer Stop_count = 2**Loop_counter_width -1;

reg [Loop_counter_width-1:0] loop_counter;

`ifndef Debug

reg [15:0] pc;

`endif

// reg [15:0] port_in_reg;

reg sync_ff, sync_ff2;

/*----------------------------------------------------------------------------

ROM儚僀儎乕儅僢僾

價僢僩埵抲 價僢僩暆 撪梕

39:35 5 柦椷

34:31 4 儗僕僗僞僼傽僀儖A億乕僩偺傾僪儗僗

30:27 4 儗僕僗僞僼傽僀儖B億乕僩偺傾僪儗僗

26:23 4 儗僕僗僞僼傽僀儖儔僀僩億乕僩偺傾僪儗僗

22:19 4 僕儍儞僾斾妑忦審

18:16 3 彨棃奼挘梡

16:16 1 loop_flag 儖乕僾張棟偡傞偐偳偆偐偺僼儔僌丄侾偱儖乕僾張棟

15:0 16 懄抣傑偨偼丄旘傃愭

-----------------------------------------------------------------------------*/

`ifndef Debug

wire [39:0] rom_data;

`endif

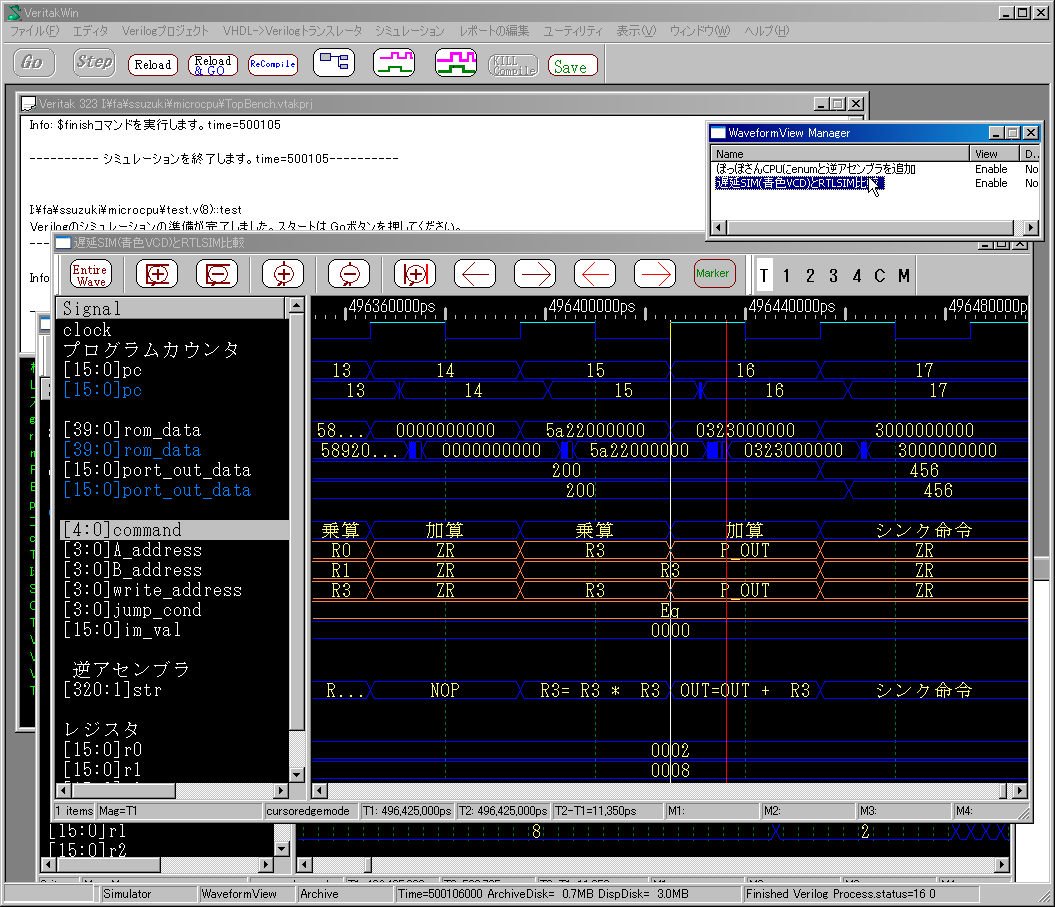

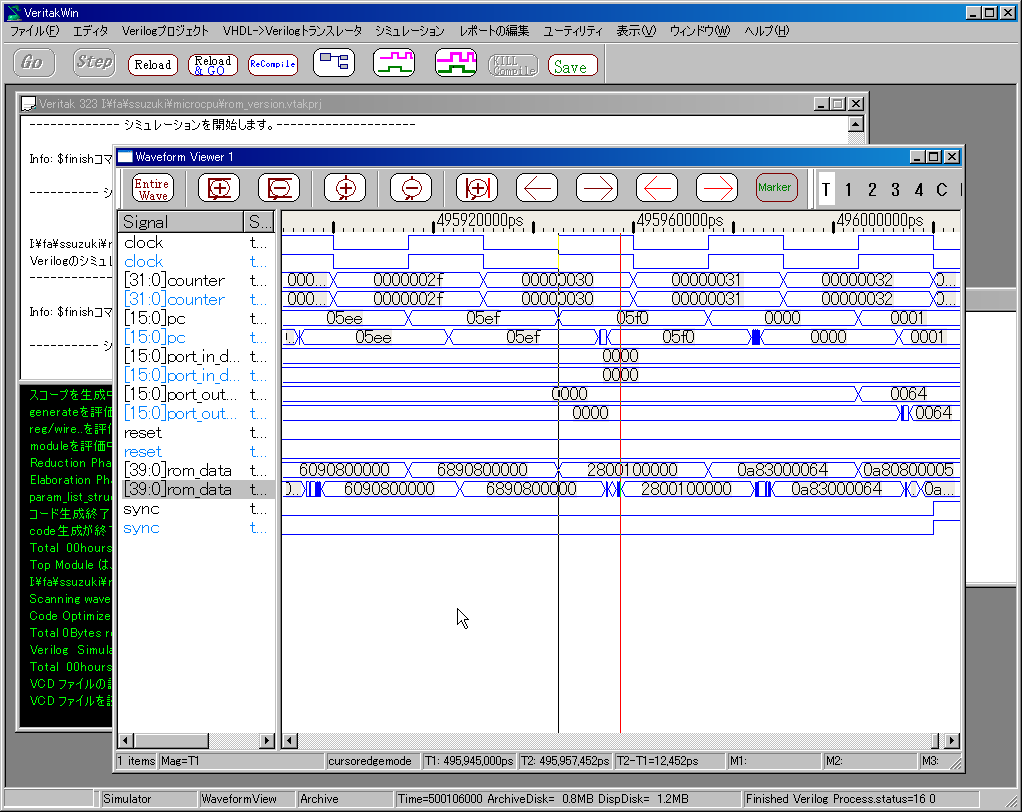

僔儈儏儗乕僔儑儞偺嵟屻偲偙傠偱偡丅惵怓偑抶墑SIM偱丄僩僢僾奒憌偺怣崋傪VCD偱婰榐偟偨傕偺偱偡丅

偝偡偑偵rom_data偺抶墑偑戝偒偔側偭偰偄傑偡偑丄RTL丂SIM偲堦抳偟偰偄傑偡丅

偙傟偱丄摦嶌偺専徹偼廔椆偱偡丅

偙偺CPU傪

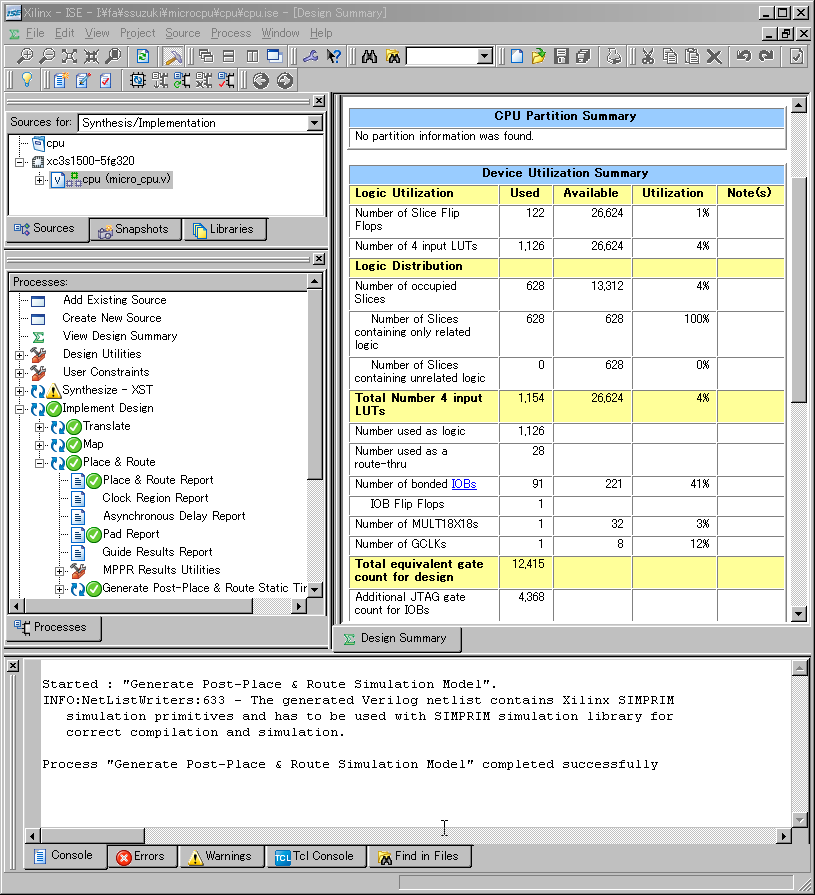

spartan3偱傕崌惉偟偰傒傑偟偨丅懍搙偼40MHz偱偡丅

抶墑僔儈儏儗乕僔儑儞偱偡丅Stratix嘦偲斾傋傞偲傗偼傝抶墑偼戝偒偔側傝傑偡丅

僔儞僋儘僫僗ROM偺幚憰

尰嵼偺FPGA偺RAM/ROM偼丄僋儘僢僋偵摨婜偟偰摦嶌偡傞僞僀僾偑庡棳偱偡偺偱丄崱傑偱偺RTL丂SIM偐傜偦偺曈傪廋惓偡傞昁梫偑偁傝傑偡丅

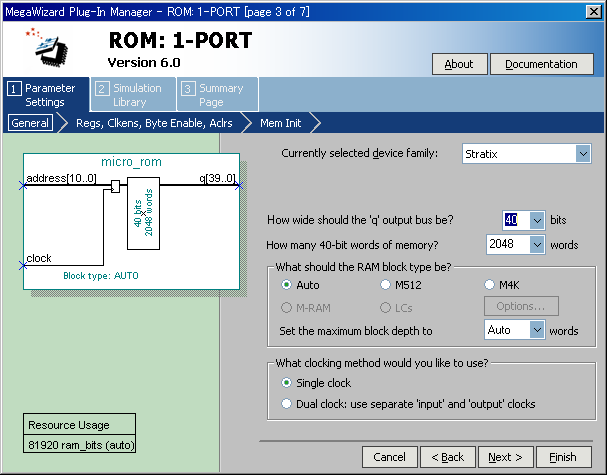

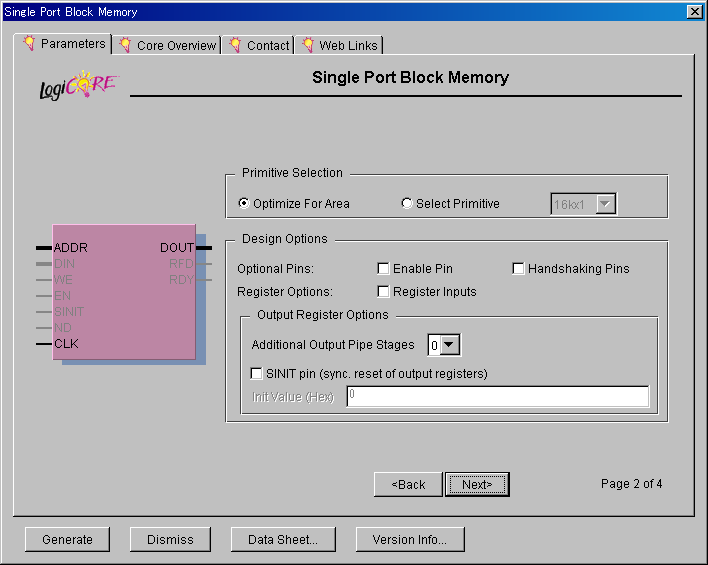

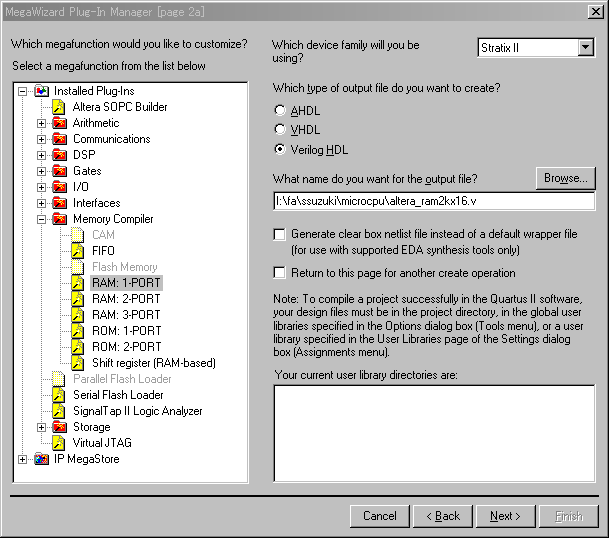

Altera偺ROM嶌惉

Mega亅Wizard偱惗惉偟傑偡丅

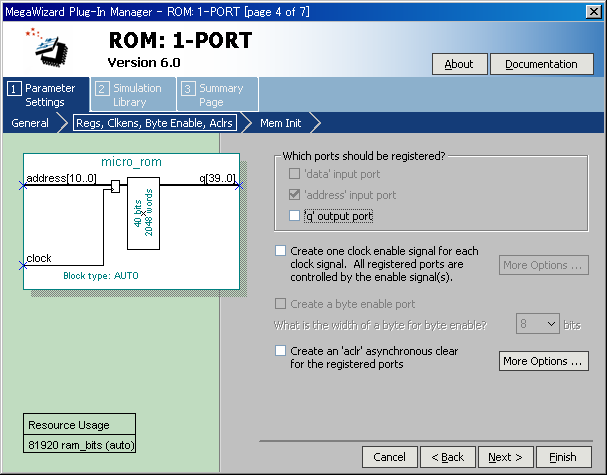

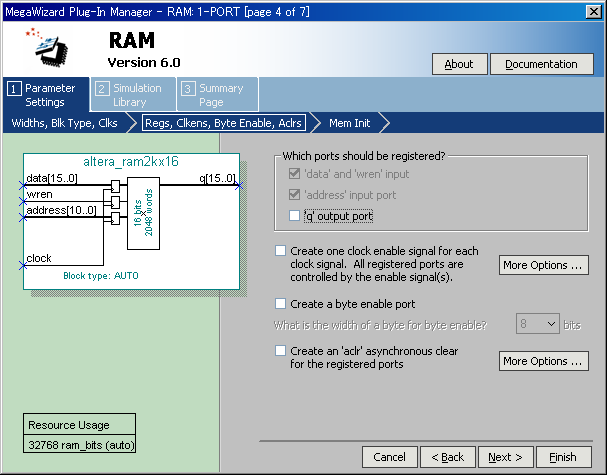

壓偺傛偆偵丄address_latach偑default 偱晅偄偰偟傑偄傑偡丅偙偺懳墳偵偮偄偰偼屻弎偟傑偡丅

價僢僩暆偼丄40價僢僩丄儚乕僪悢偼丄偲傝偁偊偢尰幚揑側抣偲偟偰俀K儚乕僪傪巜掕偟傑偡丅

屻抜偺弌椡偼丄儗僕僗僞側偟偵偟傑偡丅

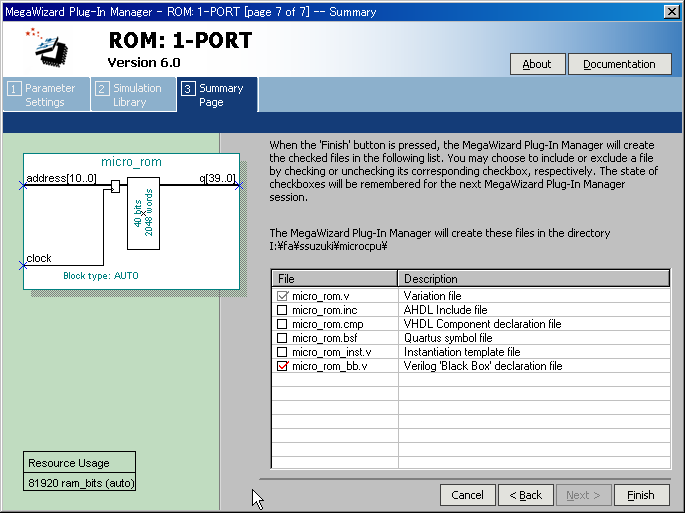

ROM偺弶婜壔偼丄hex僼傽僀儖傪巜掕偟傑偡丅乮hex僼傽僀儖偼屻弎乯

埲忋偱丄Wizard廔椆偱偡丅

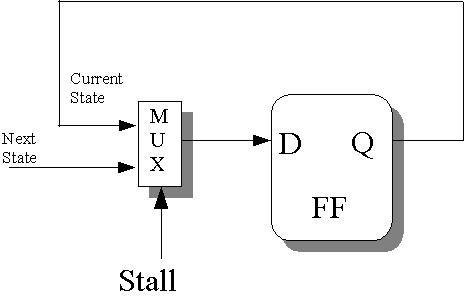

偝偰丄栤戣偼丄僾儘僌儔儉僇僂儞僞PC偲RAM撪偺傾僪儗僗儔僢僠摦嶌偑僟僽偭偰偄傞偙偲偱偡丅僞僟偱侾CLK抶傟偰偟傑偆偺偱柺敀偔偁傝傑偣傫丅偦偙偱丄ROM偵搉偡PC偼丄儗僕僗僞弌椡偱偼側偔丄慻傒崌傢偣夞楬偺傑傑丄ROM偵搉偟傑偡丅

Xilinx斉傕摨條偱丄pc_com傪搉偟傑偡丅

// ROM

`ifdef ALTERA

micro_rom rom(.address(pc_com),.q(rom_data),.clock(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`else

`ifdef XILINX

micro_rom_xilinx rom(.addr(pc_com),.dout(rom_data),.clk(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`else

rom rom(.rom_address(pc_com),.Data(rom_data),.clock(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`endif

`endif

pc_com偼丄儗僕僗僞pc偵偡傞慜偺慻傒崌傢偣夞楬偱丄埲壓偺傛偆偵側傝傑偡丅

偙偙偱丄pc_com偼丄clock偵懳偟偰摨婜偟偨怣崋偺傒偱峔惉偡傞偙偲偵拲堄偟傑偡丅FPGA撪晹偼丄旕摨婜儕僙僢僩偺FF傪彍偒丄慡晹摨婜偟偨怣崋偱峔惉偡傞偙偲偑廳梫偱偡丅reset偼丄旕摨婜側偺偱丄clock偱丄摨婜壔偟偨怣崋偵偟傑偡丅

// 儅僀僋儘僾儘僌儔儉僇僂儞僞

reg reset_sync;

always @(clock) reset_sync<=reset;//摨婜壔 pc慻傒崌傢偣夞楬偼丄摨婜壔偟偨傕偺偑昁梫

//pc 慻傒崌傢偣夞楬

//Altera sync rom 偼丄昁偢Address儔僢僠偑偮偄偰偟傑偆偺偱丄

//pc傪搉偟偰偟傑偆偺偼丄侾CLK丂DELAY偵側偭偰偟傑偆丅偦傟傪杊偖

//偨傔偵師傾僪儗僗傪慻傒崌傢偣夞楬偱搉偡丅儊儌儕撪儔僢僠偼PC偲Duplicate摦嶌偡傞

reg [15:0] pc_com;

always @* begin

if(reset_sync)

begin

pc_com= 0;

end

// 僕儍儞僾柦椷張棟

else if(command==`JMP_com && alu_data[0]==1'b1)

begin

//旘傫偱偄偗

pc_com= immediate_data;

end

else if(command==`SYNC_com)

begin //摨婜懸偪僗僞乕僩張棟

if(sync_pos_edge_detected)

begin

//摨婜怣崋傪専弌丅師偺傾僪儗僗傪幚峴奐巒丅

pc_com= pc + 1;

end

else

begin

//摨婜僄僢僕偑棃傞傑偱懸偮

pc_com= pc;

end

end

else if(loop_flag)

begin //儖乕僾張棟

if(Reset_loop_counter)

begin

//儖乕僾張棟偐傜敳偗傞

pc_com= pc + 1;

end

else

begin

//僟僂儞僇僂儞僩拞偼懸偮

pc_com= pc;

end

end

else

begin

// 壗傕側偄帪偼師偺傾僪儗僗傪幚峴奐巒

pc_com= pc + 1;

end

end

always @(posedge clock, posedge reset) begin

if(reset)

begin

pc <= 0;

end

else pc<=pc_com;

end

偙偺傛偆偵偡傟偽丄RAM撪偺傾僪儗僗儔僢僠偼丄PC偺傛偆偵怳傞傑偆偺偱丄崱傑偱偺RTL丂SIM偲摨偠僞僀儈儞僌偱摦嶌偡傞偙偲偵側傝傑偡丅

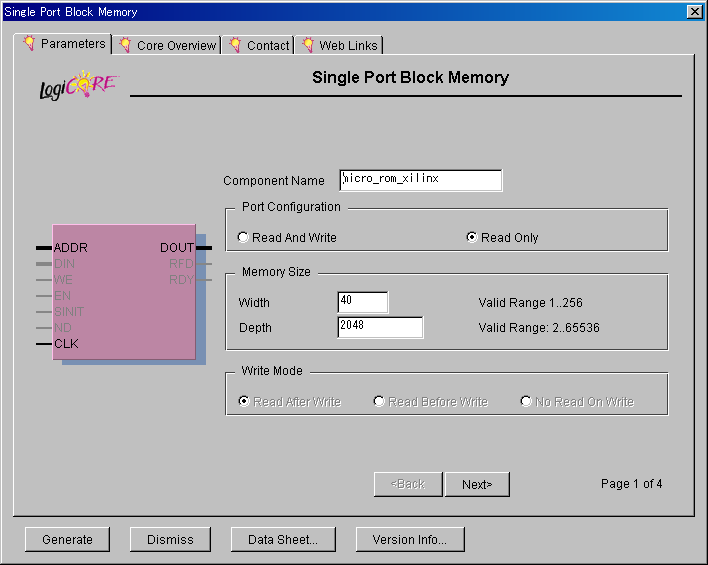

Xilinx偺ROM

coregen偱丄1億乕僩ROM傪惗惉偟傑偡丅

側偵傕巜掕偣偢偵恑傒傑偡丅

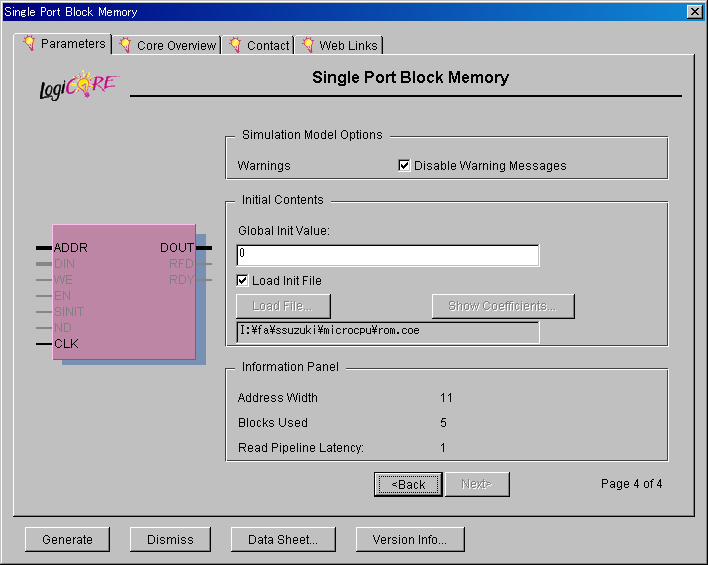

ROM偺弶婜壔僼傽僀儖偼丄rom.coe乮屻弎乯傪巜掕偟傑偡丅

ROM弶婜壔僼傽僀儖偺惗惉

Altera丄Xilinx嫟愱梡偺弶婜壔僼傽僀儖偑昁梫偵側傝傑偡丅偙傟偐傜愭丄偄偪偄偪懠偺僣乕儖偱曄姺偡傞偺偼丄柺搢側偺偱丄Verilog丂HDL僜乕僗拞丄RTL丂SIM帪偵帺摦惗惉偡傞傛偆偵偟傑偡丅

HEX僼傽僀儖偺惗惉僞僗僋偱偡丅micro_rom偺撪梕傪INTEL丂HEX僼傽僀儖(rom.hex乯偵偡傞僞僗僋偱偡丅

//memory 偺撪梕傪Altera丂ROM弶婜壔梡偵

//intel-hex僼僅乕儅僢僩偵曄姺偡傞

//僼傽僀儖->rom.hex 偲偟偰弌椡偡傞

//address 64K word max

//zx傪娷傑側偄偙偲

task make_intel_hex(input [7:0] bytes_per_word,

input integer address_max);

reg [9*8:1] str;

integer fi;

reg [15:0] ad;

integer bytes;

reg [7:0] parity;

begin

fi=$fopen("rom.hex","w");

for (ad=0;ad <=address_max;ad=ad+1) begin

$sformat(str,":%2h%4h00",bytes_per_word,ad);

parity=bytes_per_word;

parity =parity + ad[8*1 +:8];//僠僃僢僋僒儉

parity =parity + ad[0 +:8];//僠僃僢僋僒儉

$fwrite(fi,"%s",str);

for (bytes=0;bytes<bytes_per_word;bytes=bytes+1) begin: byte_loop

reg [7:0] byte;

byte=micro_rom[ad][(bytes_per_word-1-bytes)*8 +:8];

parity=parity+byte;//僠僃僢僋僒儉

$fwrite(fi,"%2h",byte);

end

parity=~parity +8'h01;//僠僃僢僋僒儉

$fwrite(fi,"%2h",parity);

$fwrite(fi,"\n");

end

$fdisplay(fi,":00000001FF");

$fclose(fi);

str="rom.ver";

//$convert_hex2ver("rom.hex",40,str);//僠僃僢僋Veritak丂Unique僼傽儞僋僔儑儞

end

endtask

micro_rom偺撪梕傪XILINX丂Coe僼傽僀儖偵偡傞僞僗僋偱偡丅

//xilinx coe file

task make_coe_file(input [7:0] bytes_per_word,

input integer address_max);

integer fi;

integer ad;

begin

fi=$fopen("rom.coe","w");

$fdisplay(fi,"memory_initialization_radix=16;");

$fdisplay(fi,"memory_initialization_vector=");

for (ad=0;ad <address_max;ad=ad+1) begin

$fdisplay(fi,"%h,",micro_rom[ad]);

end

$fdisplay(fi,"%h;",micro_rom[address_max]);

$fclose(fi);

end

endtask

埲忋偺僞僗僋傪RTL丂SIM帪偵惗惉偡傞傛偆偵偟傑偡丅

// 儅僀僋儘僐乕僪

`define PHY_ADD_MAX (1024*2-1)

//ALTERA丂ROM偺柾媅僐乕僪

reg [39:0] micro_rom [0:`PHY_ADD_MAX];

reg [15:0] address_latch;

always @(posedge clock) address_latch<=rom_address;

// always @(posedge clock ) begin//q latch 弌椡晅偺応崌丄彨棃僷僀僾儔僀儞壔偟偨偲偒偵昁梫偵側傞丅

always @* begin

Data=micro_rom[address_latch];

end

`ifdef RTL_SIM

integer i;

initial begin

for (i=0;i<= `PHY_ADD_MAX;i=i+1) begin

micro_rom[i]=romdata(i);

end

make_intel_hex(5,`PHY_ADD_MAX);//RTL SIM帪偵INTEL丂HEX僼傽僀儖傪惗惉偡傞 Altera 梡

make_coe_file(5,`PHY_ADD_MAX);//RTL SIM帪偵Xilinx梡丂Coe僼傽僀儖傪惗惉偡傞

end

`endif

埲忋偱丄僔儞僋儘僫僗ROM幚憰傊偺曄峏偑廔傢傝傑偟偨丅

XILINX,ALTERA偺愗傝懼偊偼丄朻摢偺Define偺掕媊偺桳柍偱偡丅RTL丂僔儈儏儗乕僔儑儞偺応崌偼丄Veritak丂Project偵Define傪擖傟崬傔偽巜掕偟側偔偰傕傛偄偺偱偡偑丄崌惉偡傞応崌偼丄偦傟偧傟掕媊傪曄偊傑偡丅

崱夞偺慡懱僜乕僗偱偡丅

// 儅僀僋儘僾儘僌儔儉曽幃 CPU

// 僱僀僥傿僽僐儅儞僪

`define ADD_com 5'b00000

`define SET_com 5'b00001

`define SUB_com 5'b00010

`define SHIFT_L_com 5'b00011

`define SHIFT_R_com 5'b00100

`define JMP_com 5'b00101

`define SYNC_com 5'b00110

`define AND_com 5'b00111

`define OR_com 5'b01000

`define XOR_com 5'b01001

`define NOT_com 5'b01010

`define MUL_com 5'b01011

`define BSHIFT_L_com 5'b01100

`define BSHIFT_R_com 5'b01101

// 僕儍儞僾忦審

`define Eq 4'b0000

`define Not_Eq 4'b0001

`define Always 4'b0010

`define LT 4'b0011

`define GT 4'b0100

`define LTE 4'b0101

`define GTE 4'b0110

// 儗僕僗僞傾僪儗僗

`define ZR 4'b0000

`define R0 4'b0001

`define R1 4'b0010

`define R2 4'b0011

`define R3 4'b0100

`define P_IN 4'b0101

`define P_OUT 4'b0110

`define Debug

//`define ALTERA //Altera 偺応崌僐儊儞僩傪庢傝XILINX傪僐儊儞僩傾僂僩

//`define XILINX //Xilinx偺応崌僐儊儞僩傪庢傝ALERA傪僐儊儞僩傾僂僩

// CPU

module cpu(input clock, reset,

input [15:0] port_in_data,

input sync,

output [15:0] port_out_data

`ifdef Debug

,

output [39:0] rom_data,

output reg [15:0] pc

`endif

);

localparam integer Loop_counter_width=16;

localparam integer Stop_count = 2**Loop_counter_width -1;

reg [Loop_counter_width-1:0] loop_counter;

`ifndef Debug

reg [15:0] pc;

reg [15:0] pc_com;//慻傒崌傢偣儘僕僢僋

`endif

// reg [15:0] port_in_reg;

reg sync_ff, sync_ff2;

/*----------------------------------------------------------------------------

ROM儚僀儎乕儅僢僾

價僢僩埵抲 價僢僩暆 撪梕

39:35 5 柦椷

34:31 4 儗僕僗僞僼傽僀儖A億乕僩偺傾僪儗僗

30:27 4 儗僕僗僞僼傽僀儖B億乕僩偺傾僪儗僗

26:23 4 儗僕僗僞僼傽僀儖儔僀僩億乕僩偺傾僪儗僗

22:19 4 僕儍儞僾斾妑忦審

18:16 3 彨棃奼挘梡

16:16 1 loop_flag 儖乕僾張棟偡傞偐偳偆偐偺僼儔僌丄侾偱儖乕僾張棟

15:0 16 懄抣傑偨偼丄旘傃愭

-----------------------------------------------------------------------------*/

`ifndef Debug

wire [39:0] rom_data;

`endif

wire [4:0] command = rom_data[39:35];

wire [3:0] A_address = rom_data[34:31];

wire [3:0] B_address = rom_data[30:27];

wire [3:0] write_address = rom_data[26:23];

wire [3:0] jump_cond = rom_data[22:19];

wire [2:0] reserved = rom_data[18:16];

wire [15:0] immediate_data = rom_data[15:0];

wire loop_flag = reserved[0];

wire [15:0] out_dataA, out_dataB;

wire [15:0] alu_data;

// SET僐儅儞僪偺帪偼丄"A億乕僩偵戙擖偡傞抣" 傪愙懕偡傞丅

// 仸 ALU偱 僛儘儗僕僗僞偲壛嶼偟偰戙擖偡傞帠偱丄SET傪幚尰偡傞堊丅

wire [15:0] Aport_data = (command==`SET_com) ? immediate_data : port_in_data;

//儖乕僾僇僂儞僞儕僙僢僩忦審

wire Reset_loop_counter = (loop_counter<2)||

(loop_counter==Stop_count && immediate_data == 16'b0)

? 1 : 0;

//儖乕僾僇僂儞僞偺張棟

always @(posedge clock, posedge reset) begin

if(reset)

begin

loop_counter <= Stop_count;

end

else if(Reset_loop_counter)

begin

loop_counter <= Stop_count;

end

else if(loop_flag && loop_counter==Stop_count)

begin

// 儖乕僾僇僂儞僩抣傪僙僢僩

loop_counter <= immediate_data;

end

//else if ((loop_flag) && (loop_counter>1))

else if(loop_flag)

begin

// 儖乕僾張棟

loop_counter <= loop_counter - 16'b1;

end

else

begin

loop_counter <= Stop_count;

end

end

// 擖椡摨婜僄僢僕専弌

always @(posedge clock, posedge reset) begin

if (reset) sync_ff<=0;

else sync_ff<=sync;

end

always @(posedge clock, posedge reset) begin

if (reset) sync_ff2<=0;

else sync_ff2<=sync_ff;

end

// 棫偪忋偑傝僄僢僕傪専弌

wire sync_pos_edge_detected = sync_ff & ~sync_ff2;

// 儅僀僋儘僾儘僌儔儉僇僂儞僞

reg reset_sync;

always @(clock) reset_sync<=reset;//摨婜壔 pc慻傒崌傢偣夞楬偼丄摨婜壔偟偨傕偺偑昁梫

//pc 慻傒崌傢偣夞楬

//Altera sync rom 偼丄昁偢Address儔僢僠偑偮偄偰偟傑偆偺偱丄

//pc傪搉偟偰偟傑偆偺偼丄侾CLK丂DELAY偵側偭偰偟傑偆丅偦傟傪杊偖

//偨傔偵師傾僪儗僗傪慻傒崌傢偣夞楬偱搉偡丅儊儌儕撪儔僢僠偼PC偲Duplicate摦嶌偡傞

reg [15:0] pc_com;

always @* begin

if(reset_sync)

begin

pc_com= 0;

end

// 僕儍儞僾柦椷張棟

else if(command==`JMP_com && alu_data[0]==1'b1)

begin

//旘傫偱偄偗

pc_com= immediate_data;

end

else if(command==`SYNC_com)

begin //摨婜懸偪僗僞乕僩張棟

if(sync_pos_edge_detected)

begin

//摨婜怣崋傪専弌丅師偺傾僪儗僗傪幚峴奐巒丅

pc_com= pc + 1;

end

else

begin

//摨婜僄僢僕偑棃傞傑偱懸偮

pc_com= pc;

end

end

else if(loop_flag)

begin //儖乕僾張棟

if(Reset_loop_counter)

begin

//儖乕僾張棟偐傜敳偗傞

pc_com= pc + 1;

end

else

begin

//僟僂儞僇僂儞僩拞偼懸偮

pc_com= pc;

end

end

else

begin

// 壗傕側偄帪偼師偺傾僪儗僗傪幚峴奐巒

pc_com= pc + 1;

end

end

always @(posedge clock, posedge reset) begin

if(reset)

begin

pc <= 0;

end

else pc<=pc_com;

end

// 儗僕僗僞僼傽僀儖

register_file register_file(.clock(clock),

.reset(reset),

.A_address(A_address),

.B_address(B_address),

.write_address(write_address),

.alu_data(alu_data),

.out_dataA(out_dataA),

.out_dataB(out_dataB),

.port_in_data(Aport_data),

.port_out_data(port_out_data));

// ALU

alu alu(.command(command),

.jump_cond(jump_cond),

.portA(out_dataA),

.portB(out_dataB),

.alu_out(alu_data));

// ROM

`ifdef ALTERA

micro_rom rom(.address(pc_com),.q(rom_data),.clock(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`else

`ifdef XILINX

micro_rom_xilinx rom(.addr(pc_com),.dout(rom_data),.clk(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`else

rom rom(.rom_address(pc_com),.Data(rom_data),.clock(clock));//ROM 偵偼pc偱偼側偔pc_com傪搉偡宍偵曄峏

`endif

`endif

endmodule

// 儗僕僗僞僼傽僀儖

// 婰壇慺巕傪儗僕僗僞偺廤傑傝偲偟偰丄傑偲傔偰儌僕儏乕儖壔丅

// 摨帪偵撉傒彂偒偱偒傞億乕僩偑俁偮

// 儔僀僩億乕僩偑侾偮丄儕乕僪億乕僩偑俀偮丅

module register_file(input clock,

input reset,

input [3:0] A_address,

input [3:0] B_address,

input [3:0] write_address,

input [15:0] alu_data, port_in_data,

output [15:0] out_dataA, out_dataB, port_out_data);

// CPU儗僕僗僞

reg [15:0] p_out_reg, r0, r1, r2, r3;

// 億乕僩傾僂僩儗僕僗僞

always @(posedge clock, posedge reset) begin

if(reset)

begin

p_out_reg <= 0;

end

else if(write_address == `P_OUT)

begin

p_out_reg <= alu_data;

end

else

begin

p_out_reg <= p_out_reg;

end

end

// 斈梡儗僕僗僞R0

always @(posedge clock, posedge reset) begin

if(reset)

begin

r0 <= 0;

end

else if(write_address == `R0)

begin

r0 <= alu_data;

end

else

begin

r0 <= r0;

end

end

// 斈梡儗僕僗僞R1

always @(posedge clock, posedge reset) begin

if(reset)

begin

r1 <= 0;

end

else if(write_address == `R1)

begin

r1 <= alu_data;

end

else

begin

r1 <= r1;

end

end

// 斈梡儗僕僗僞R2

always @(posedge clock, posedge reset) begin

if(reset)

begin

r2 <= 0;

end

else if(write_address == `R2)

begin

r2 <= alu_data;

end

else

begin

r2 <= r2;

end

end

// 斈梡儗僕僗僞R3

always @(posedge clock, posedge reset) begin

if(reset)

begin

r3 <= 0;

end

else if(write_address == `R3)

begin

r3 <= alu_data;

end

else

begin

r3 <= r3;

end

end

// A億乕僩弌椡(ALU傊)

assign out_dataA = (A_address==`P_OUT) ? p_out_reg :

(A_address==`P_IN) ? port_in_data :

(A_address==`R0) ? r0 :

(A_address==`R1) ? r1 :

(A_address==`R2) ? r2 :

(A_address==`R3) ? r3 : 16'b0;

// B億乕僩弌椡(ALU傊)

assign out_dataB = (B_address==`P_OUT) ? p_out_reg :

(B_address==`P_IN) ? port_in_data :

(B_address==`R0) ? r0 :

(B_address==`R1) ? r1 :

(B_address==`R2) ? r2 :

(B_address==`R3) ? r3 : 16'b0;

// 弌椡億乕僩(偦偺傑傑弌椡)

assign port_out_data = p_out_reg;

endmodule

// ALU

module alu(input [4:0] command,

input [3:0] jump_cond,

input [15:0] portA,portB,

output reg [15:0] alu_out);

always @(*) begin

case (command)

`ADD_com: alu_out=portA+portB;

`SUB_com: alu_out=portA-portB;

`SHIFT_L_com: alu_out=portB << 1;

`SHIFT_R_com: alu_out=portB >> 1;

`BSHIFT_L_com:alu_out=portA << portB;

`BSHIFT_R_com:alu_out=portA >> portB;

`MUL_com: alu_out=portA * portB;

`AND_com: alu_out=portA & portB;

`OR_com: alu_out=portA | portB;

`XOR_com: alu_out=portA ^ portB;

`NOT_com: alu_out=~portA;

`JMP_com:

case (jump_cond)

`Eq: alu_out=(portA == portB);

`Not_Eq: alu_out=(portA != portB);

`Always: alu_out=1;

`LT: if (portA < portB)

alu_out=1;

else

alu_out=0;

`GT: if (portA > portB)

alu_out=1;

else

alu_out=0;

`LTE: if (portA <= portB)

alu_out=1;

else

alu_out=0;

`GTE: if (portA >= portB)

alu_out=1;

else

alu_out=0;

default: alu_out=0;

endcase

default: alu_out=portA+portB;

endcase

end

endmodule

module rom(input [15:0] rom_address,

input clock,//僔儞僋儘僫僗ROM偵曄峏

output reg [39:0] Data);

//assign Data = romdata(rom_address);//僔儞僋儘僫僗ROM偵曄峏

//TAK start

wire [4:0] command = Data[39:35];

wire [3:0] A_address = Data[34:31];

wire [3:0] B_address = Data[30:27];

wire [3:0] write_address = Data[26:23];

wire [3:0] jump_cond = Data[22:19];

wire [15:0] im_val=Data[15:0];

wire [2:0] loop_cond=Data[18:16];

//TAK end

// 僐儅儞僪

parameter [4:0] Set=`SET_com,

Add=`ADD_com,

Sub=`SUB_com,

Shift_L=`SHIFT_L_com,

Shift_R=`SHIFT_R_com,

Jmp=`JMP_com,

Sync=`SYNC_com,

Mul=`MUL_com,

And=`AND_com,

Or =`OR_com,

Xor=`XOR_com,

Not=`NOT_com,

BShift_L=`BSHIFT_L_com,

BShift_R=`BSHIFT_R_com;

parameter [4:0] \僙僢僩 =`SET_com,

\壛嶼 =`ADD_com,

\尭嶼 =`SUB_com,

\嵍僔僼僩 =`SHIFT_L_com,

\塃僔僼僩 =`SHIFT_R_com,

\僕儍儞僾 =`JMP_com,

\僔儞僋柦椷 =`SYNC_com,

\忔嶼 =`MUL_com,

\仌 =`AND_com,

\OR =`OR_com,

\XOR =`XOR_com,

\NOT =`NOT_com,

\嵍僶儗儖僔僼僩 =`BSHIFT_L_com,

\塃僶儗儖僔僼僩 =`BSHIFT_R_com;

// 儗僕僗僞傾僪儗僗

parameter [3:0] P_OUT=`P_OUT,//IO億乕僩弌椡

P_IN=`P_IN, //IO億乕僩擖椡

R0= `R0,

R1= `R1,

R2= `R2,

R3= `R3,

ZR= `ZR; // 僛儘儗僕僗僞 (= 僛儘GND)

// 僕儍儞僾忦審

parameter [3:0] Eq=`Eq,

Not_Eq=`Not_Eq,

Always=`Always,

LT=`LT,

GT=`GT,

LTE=`LTE,

GTE=`GTE;

// 儖乕僾張棟

parameter [2:0] Reserved = 3'b000,

LoopEnabled = 3'b001;

// 儅僋儘柦椷

// NOP

`define NOP romdata={Add,ZR,ZR,ZR,Eq,Reserved,16'h 0000}

// 僐僺乕 : r0 仺 r1

`define MOV(r0,r1) romdata={Add,r0,ZR,r1,Eq,Reserved,16'h 0000}

// 僋儕傾 : r0 = 0

`define CLR(r0) romdata={Add,ZR,ZR,r0,Eq,Reserved,16'h 0000}

// 掕悢戙擖 : r0 = num

`define SET(r0,num) romdata={Set,P_IN,ZR,r0,Eq,Reserved,16'd num}

// 僕儍儞僾

`define JUMP(num) romdata={Jmp,ZR,ZR,ZR,Always,Reserved,16'd num}

// 榑棟斀揮

`define NOT(r0,r1) romdata={Not,r0,ZR,r1,Always,Reserved,16'h 0000}

// 懌偟嶼 : r2 = r0 + r1

`define ADD(r0,r1,r2) romdata={Add,r0,r1,r2,Eq,Reserved,16'h 0000}

// 堷偒嶼 : r2 = r0 - r1

`define SUB(r0,r1,r2) romdata={Sub,r0,r1,r2,Eq,Reserved,16'h 0000}

// 忔嶼 : r2 = r0 * r1

`define MUL(r0,r1,r2) romdata={Mul,r0,r1,r2,Eq,Reserved,16'h 0000}

// 忦審暥 : if(r0<r1) goto num;

`define JUMP_IF_LT(r0,r1,num) romdata={Jmp,r0,r1,ZR,LT,Reserved,16'd num}

// 忦審暥 : if(r0>r1) goto num;

`define JUMP_IF_GT(r0,r1,num) romdata={Jmp,r0,r1,ZR,GT,Reserved,16'd num}

// 忦審暥 : if(r0<=r1) goto num;

`define JUMP_IF_LTE(r0,r1,num) romdata={Jmp,r0,r1,ZR,LTE,Reserved,16'd num}

// 忦審暥 : if(r0>=r1) goto num;

`define JUMP_IF_GTE(r0,r1,num) romdata={Jmp,r0,r1,ZR,GTE,Reserved,16'd num}

// 忦審暥 : if(r0==r1) goto num;

`define JUMP_IF_EQ(r0,r1,num) romdata={Jmp,r0,r1,ZR,Eq,Reserved,16'd num}

// 1價僢僩僔僼僩

`define SHIFT_L(r0,r1) romdata={Shift_L,ZR,r0,r1,Eq,Reserved,16'h 0000}

`define SHIFT_R(r0,r1) romdata={Shift_R,ZR,r0,r1,Eq,Reserved,16'h 0000}

// 僶儗儖僔僼僩

`define BSHIFT_L(r0,r1,r2) romdata={BShift_L,r0,r1,r2,Eq,Reserved,16'h 0000}

`define BSHIFT_R(r0,r1,r2) romdata={BShift_R,r0,r1,r2,Eq,Reserved,16'h 0000}

// 奜晹擖椡丒棫偪忋偑傝僄僢僕傑偱懸偮

`define SYNC romdata={Sync,ZR,ZR,ZR,Eq,Reserved,16'h 0000}

// 儖乕僾孞傝曉偟柦椷(JUMP柦椷暘偺1僋儘僢僋傪愡栺)

// ex : r2 = r0 + r1 傪 num+1 夞孞傝曉偡丅偦偺娫丄pc 偼 尰傾僪儗僗偱懸婡丅

`define ADD_LOOP(r0,r1,r2,num) romdata={Add,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define SUB_LOOP(r0,r1,r2,num) romdata={Sub,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define MUL_LOOP(r0,r1,r2,num) romdata={Mul,r0,r1,r2,Eq,LoopEnabled,16'd num}

`define SHIFT_L_LOOP(r0,num) romdata={Shift_L,ZR,r0,r0,Eq,LoopEnabled,16'd num}

`define SHIFT_R_LOOP(r0,num) romdata={Shift_R,ZR,r0,r0,Eq,LoopEnabled,16'd num}

//Tak start 丂媡傾僙儞僽儔

reg [8*40:1] str;

function [8*3:1] get_rn(input [3:0] addr);

case (addr)

P_OUT: get_rn="OUT";

P_IN: get_rn="IN"; //IO億乕僩擖椡

R0: get_rn="R0";

R1: get_rn="R1";

R2: get_rn="R2";

R3: get_rn="R3";

ZR: get_rn="ZR"; // 僛儘儗僕僗僞 (= 僛儘GND)

default: get_rn="???";

endcase

endfunction

always @* begin

case (command)

Add:

if(loop_cond==0) begin

if (A_address==ZR && B_address==ZR & write_address==ZR) $sformat(str,"NOP");

else if (B_address==ZR && A_address==ZR ) $sformat(str,"%s傪僋儕傾",get_rn(write_address));

else if (B_address==ZR ) $sformat(str,"%s偐傜%s傊僐僺乕",get_rn(A_address),get_rn(write_address));

else $sformat(str,"%s=%s + %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else begin

if (A_address==ZR && B_address==ZR & write_address==ZR) $sformat(str,"NOP %d儖乕僾晅",im_val);

else if (B_address==ZR && A_address==ZR ) $sformat(str,"%s傪僋儕傾丂 %d儖乕僾晅",get_rn(write_address),im_val);

else if (B_address==ZR ) $sformat(str,"%s偐傜%s傊僐僺乕丂 %d儖乕僾晅",get_rn(A_address),get_rn(write_address),im_val);

else $sformat(str,"%s=%s + %s %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

end

Set: $sformat(str,"%s=%h[Hex]",get_rn(write_address),im_val);

Mul:

if (loop_cond==0) begin

$sformat(str,"%s=%s * %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else $sformat(str,"%s=%s * %s 丂 %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

Sub:

if (loop_cond==0) begin

$sformat(str,"%s=%s - %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

end else $sformat(str,"%s=%s - %s %d儖乕僾晅",get_rn(write_address),get_rn(A_address),get_rn(B_address),im_val);

Sync:

$sformat(str,"僔儞僋柦椷");

Not: $sformat(str,"%s=~%s",get_rn(write_address),get_rn(A_address));

Jmp:

if (jump_cond==Always) $sformat(str,"%d斣抧傊僕儍儞僾",im_val);

else if (jump_cond==LT) $sformat(str,"%s < %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==GT) $sformat(str,"%s > %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==LTE) $sformat(str,"%s <= %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==GTE) $sformat(str,"%s >= %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

else if (jump_cond==Eq) $sformat(str,"%s == %s 側傜%d斣抧傊僕儍儞僾",get_rn(A_address),get_rn(B_address),im_val);

Shift_L:

if (loop_cond==0) $sformat(str,"%s=%s << 1",get_rn(write_address),get_rn(B_address));

else $sformat(str,"%s=%s << %d",get_rn(write_address),get_rn(B_address),im_val);

Shift_R:

if (loop_cond==0) $sformat(str,"%s=%s >> 1",get_rn(write_address),get_rn(B_address));

else $sformat(str,"%s=%s >> %d",get_rn(write_address),get_rn(B_address),im_val);

BShift_L:

$sformat(str,"%s=%s <<%s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

BShift_R:

$sformat(str,"%s=%s >> %s",get_rn(write_address),get_rn(A_address),get_rn(B_address));

endcase

end

//Tak end

// 儅僀僋儘僐乕僪

`define PHY_ADD_MAX (1024*2-1)

//ALTERA丂ROM偺柾媅僐乕僪

reg [39:0] micro_rom [0:`PHY_ADD_MAX];

reg [15:0] address_latch;

always @(posedge clock) address_latch<=rom_address;

// always @(posedge clock ) begin//q latch 弌椡晅偺応崌丄彨棃僷僀僾儔僀儞壔偟偨偲偒偵昁梫偵側傞丅

always @* begin

Data=micro_rom[address_latch];

end

`ifdef RTL_SIM

integer i;

initial begin

for (i=0;i<= `PHY_ADD_MAX;i=i+1) begin

micro_rom[i]=romdata(i);

end

make_intel_hex(5,`PHY_ADD_MAX);//RTL SIM帪偵INTEL丂HEX僼傽僀儖傪惗惉偡傞 Altera 梡

make_coe_file(5,`PHY_ADD_MAX);//RTL SIM帪偵Xilinx梡丂Coe僼傽僀儖傪惗惉偡傞

end

`endif

//memory 偺撪梕傪Altera丂ROM弶婜壔梡偵

//intel-hex僼僅乕儅僢僩偵曄姺偡傞

//僼傽僀儖->rom.hex 偲偟偰弌椡偡傞

//address 64K word max

//zx傪娷傑側偄偙偲

task make_intel_hex(input [7:0] bytes_per_word,

input integer address_max);

reg [9*8:1] str;

integer fi;

reg [15:0] ad;

integer bytes;

reg [7:0] parity;

begin

fi=$fopen("rom.hex","w");

for (ad=0;ad <=address_max;ad=ad+1) begin

$sformat(str,":%2h%4h00",bytes_per_word,ad);

parity=bytes_per_word;

parity =parity + ad[8*1 +:8];//僠僃僢僋僒儉

parity =parity + ad[0 +:8];//僠僃僢僋僒儉

$fwrite(fi,"%s",str);

for (bytes=0;bytes<bytes_per_word;bytes=bytes+1) begin: byte_loop

reg [7:0] byte;

byte=micro_rom[ad][(bytes_per_word-1-bytes)*8 +:8];

parity=parity+byte;//僠僃僢僋僒儉

$fwrite(fi,"%2h",byte);

end

parity=~parity +8'h01;//僠僃僢僋僒儉

$fwrite(fi,"%2h",parity);

$fwrite(fi,"\n");

end

$fdisplay(fi,":00000001FF");

$fclose(fi);

str="rom.ver";

//$convert_hex2ver("rom.hex",40,str);//僠僃僢僋Veritak丂Unique僼傽儞僋僔儑儞

end

endtask

//xilinx coe file

task make_coe_file(input [7:0] bytes_per_word,

input integer address_max);

integer fi;

integer ad;

begin

fi=$fopen("rom.coe","w");

$fdisplay(fi,"memory_initialization_radix=16;");

$fdisplay(fi,"memory_initialization_vector=");

for (ad=0;ad <address_max;ad=ad+1) begin

$fdisplay(fi,"%h,",micro_rom[ad]);

end

$fdisplay(fi,"%h;",micro_rom[address_max]);

$fclose(fi);

end

endtask

function [39:0]romdata;

input [15:0] address;

case(address)

//Commad A_addr, B_addr, Write_addr, Jmp_cond, Reserved, IM

0: `SET(P_OUT, 100);

1: `SET(R0, 5);

2: `MOV(R0, R1);

3: `MOV(R1, R2);

4: `MOV(R2, R3);

5: `SUB(R1, R2, R0);

6: `SUB(R3, R1, R3);

7: `ADD(P_IN, P_OUT, P_OUT);

8: `ADD(P_OUT, P_OUT, P_OUT);

9: `SUB(P_IN, P_IN, R1);

10: `SUB(P_OUT, P_IN, R2);

11: `SET(R0, 2);

12: `SET(R1, 8);

13: `MUL(R0, R1, R3);

14: `NOP;

15: `MUL(R3, R3, R3);

16: `ADD(P_OUT, R3, P_OUT);

17: `SYNC;

18: `JUMP(1000);

// 僔僼僩丒忔嶼

1000: `SET(R0, 5);

1001: `SET(R1, 2);

1002: `ADD_LOOP(R0, R1, R0, 10);

1003: `SHIFT_L_LOOP(R1, 5);

1004: `SHIFT_R_LOOP(R1, 5);

1005: `SUB_LOOP(R0, R1, R0, 10);

1006: `SET(P_OUT, 5);

1007: `MUL_LOOP(P_OUT, R1, P_OUT, 7);

1008: `JUMP(1500);

// 忦審暥

1500: `SET(R0, 16);

1501: `SET(R1, 2);

1502: `SET(P_OUT, 0);

1503: `SUB(R0, R1, R0);

1504: `JUMP_IF_GT(R0, R1 ,1503);

1505: `NOP ;//NOP憓擖 丂僨傿儗僀僪僗儘僢僩

// 忦審暥

1506: `SET(R2, 16);

1507: `SET(R3, 2);

1508: `SET(P_OUT, 0);

1509: `SUB(R2, R3, R2);

1511: `JUMP_IF_GTE(R2, R3 ,1509);

1512:`NOP;//NOP憓擖丂僨傿儗僀僪僗儘僢僩

// 1010_1010_1010_1010

// 價僢僩斀揮

1513: `SET(R0, 43690);

1514: `NOT(R0, R1);

// 僶儗儖僔僼僞

1515: `SET(R0, 2);

1516: `SET(R1, 7);

1517: `SET(R2, 0);

1518: `BSHIFT_L(R0, R1, R0);

1519: `BSHIFT_R(R0, R1, R0);

1520: `JUMP(0);

default: romdata = 0;

endcase

endfunction

endmodule

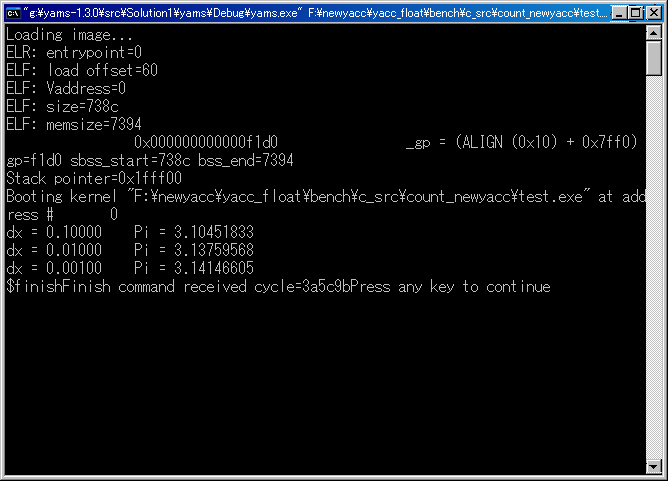

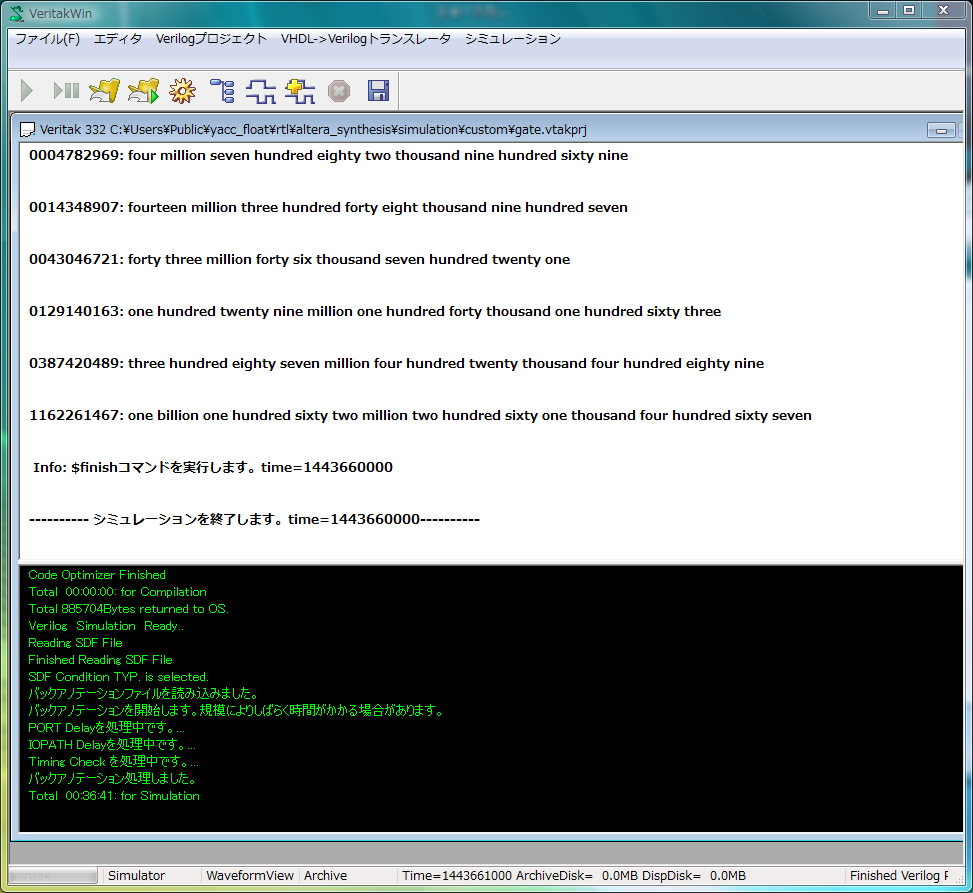

側偍丄崱夞偺曄峏偱丄

Staratix嘦偼丄88MHz

Spartan 3偼丄44MHz 偲側傝傑偟偨丅

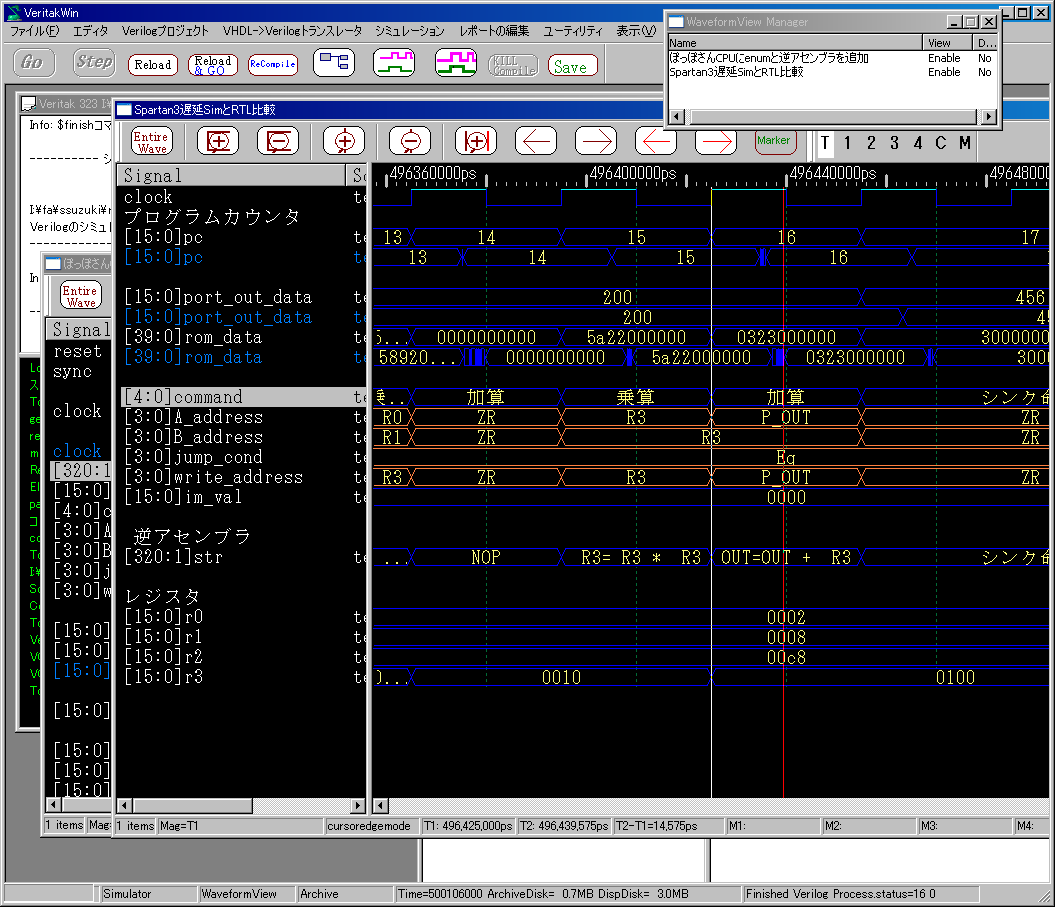

崌惉屻偺抶墑僔儈儏儗乕僔儑儞寢壥(惵怓VCD)偱偡丅

Spartan3

摨條偵Staratix嘦偱偡丅

僔儞僋儘僫僗ROM偺傾乕僇僀僽偱偡丅

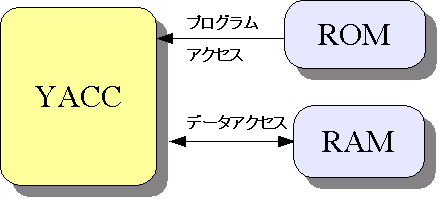

RAM偺幚憰

FPGA偺RAM傪僨乕僞儊儌儕偲偟偰巊偆偙偲傪峫偊傑偡丅偙偙偱偼丄奜晹RAM傪巊偆偙偲偼峫椂偣偢偵丄FPGA撪偺RAM傪巊偆偙偲傪峫偊傑偡丅

偝偰偙偙偱偺栤戣偼丄摨婜RAM偵偁傝傑偡丅偲傝偁偊偢WIZARD偱RAM傪嶌偭偰傒傑偟傚偆丅

Single_PortRAM傪惗惉偟傑偡丅

偲傝偁偊偢丄16價僢僩暆2K儚乕僪偱偡丅

Q弌椡側偟偵偟傑偡丅偙偺僟僀傾僌儔儉偺捠傝丄RAM偵偍偄偰傕慜抜偵FF偑擖偭偰偟傑偄傑偡丅廬偭偰丄侾CLOCK抶傟偰偟傑偆偙偲偵拲堄偟偰偔偩偝偄丅CPU偐傜尒偰WRITE偼丄彂偒偭傁側偟側偺偱侾CLOCK偱WRITE偱偒傑偡偑丄READ偼丄侾CLOCK偱偼曉偭偰偒傑偣傫丅偙偙偱偺愝寁偼戝偒側暘偐傟栚偱偡丅俀CLOCK傪嫋梕偱偒側偄偲偡傞偐丄尒偨栚偵侾CLOCK丂R/W偲側傞傛偆偵丄慡懱偺僽儘僢僋傪峫偊側偍偡偐偲偄偆栤戣偵側傝傑偡丅屻幰偼丄CPU慡懱偺僷僀僾儔僀儞壔偵傛偭偰払惉偡傞偙偲偑偱偒丄僷僀僾儔僀儞偵傛傝丄摦嶌懍搙傪岦忋偝偣傞偙偲偑偱偒傑偡丅偟偐偟椙偄帠偽偐傝偱偼側偔丄偟傢婑偣偼丄JUMP柦椷偵尰傟傑偡丅JUMP傾僪儗僗偑惷揑偵寛傑偭偰偄傞側傜偽丄愭撉傒偵傛傝夞旔偡傞偙偲偑偱偒傑偡偑丅JUMP傾僪儗僗偑摦嶌帪偵偟偐寛傑傜側偄応崌丄懄偪丄忦審僽儔儞僠傗丄忦審CALL偑偁傞応崌丄僷僀僾儔僀儞暘偺抜悢偵墳偠偨僋儘僢僋悢偑偐偐偭偰偟傑偄傑偡丅丂乮侾CLOCK偱READ/WRITE偡傞僷僀僾儔僀儞偺椺偼丄偙偪傜偺僷僀僾儔僀儞偺専摙傪尒偰偔偩偝偄丅僷僀僾儔僀儞偑怺偄偲偦傟偩偗儁僫儖僥傿傕戝偒偔側傝傑偡丅乯

崱夞偼丄娙扨側愝寁傪栚巜偟偰偄傞偺偱丄僷僀僾儔僀儞偼巊傢偢丄READ偺傒俀CLOCK丄偦偺懠偼侾CLOCK偲偡傞曽恓偱愝寁偟傑偡丅

傾僪儗僔儞僌儌乕僪

壓婰偺擇偮傪旛偊傑偡丅R0傪僀儞僨僢僋僗偲偟偨傾僪儗僔儞僌偱偡丅

- Immediate

- Immediate+R0

埲壓捛壛晹偱偡丅

Altera/Xilinx 偺RAM傪擖傟崬傓慜偵柾媅僶乕僕儑儞偱摦嶌妋擣偟偰偍偒傑偡丅

//ALTERA RAM偺柾媅僐乕僪

`define PHY_ADD_MAX_RAM (1024*2-1)//Dec.17.2006

reg [15:0] ram [0:`PHY_ADD_MAX_RAM];

reg [15:0] ram_address_latch;

reg ram_write_enable_latch;

reg [15:0] ram_data_latch,ram_output_data;

//傾僪儗僗儔僢僠丄僨乕僞儔僢僠丄儔僀僩Enable儔僢僠偑偁傞

always @(posedge clock) ram_address_latch<=ram_address;

always @(posedge clock) ram_write_enable_latch<=ram_write_enable;

always @(posedge clock) ram_data_latch<=ram_input_port;

always @* begin

ram_output_data=ram[ram_address_latch];

end

assign ram_output_port=ram_output_data;

always @(negedge clock) begin//棫壓傝偱撪晹RAM偵彂偒崬傒

if (ram_write_enable_latch) begin

ram[ram_address_latch] <=ram_data_latch;

end

end

RAM傪儗僕僗僞偲摨偠傛偆偵埖偆偺偱丄儗僕僗僞傾僪儗僗偺傾僪儗僗嬻娫偵捛壛偟傑偡丅

// 儗僕僗僞傾僪儗僗 `define ZR 4'b0000 `define R0 4'b0001 `define R1 4'b0010 `define R2 4'b0011 `define R3 4'b0100 `define P_IN 4'b0101 `define P_OUT 4'b0110 `define RAM_PORT 4'b0111 //Dec.17.2006

ROM偺價僢僩僼傿乕儖僪偵傕捛壛偟傑偡丅

價僢僩18偼丄RAM偺WriteEnable偵偟傑偡丅

價僢僩17偼丄僀儞僨僢僋僗傾僪儗僔儞僌偐愨懳傾僪儗僗偐傪寛傔偰偄傞僼儔僌偱偡丅

ROM儚僀儎乕儅僢僾

價僢僩埵抲 價僢僩暆 撪梕

39:35 5 柦椷

34:31 4 儗僕僗僞僼傽僀儖A億乕僩偺傾僪儗僗

30:27 4 儗僕僗僞僼傽僀儖B億乕僩偺傾僪儗僗