例によってOpencoresから頂いてきます。筆者が追加修正したものをここに置いておきます。(Dec.29.2006 Veritak VersionUpに伴い一部修正しました。)

F.A.Q.

Q.Xilinx ISEにおいてコンパイルする事が出来ませんでした。

どのようにすれば使用する事が出来るのでしょうか?

Ans.ソースは、VHDLから自動変換をしたものですが、限界があり、一般には、手修正が必要になります。論理合成には、また別な手修正が必要になります。この場合、論理合成可能な記述に変換するVHDL・Verilog両方のスキルが必要になることは言うまでもありません。

| ・Cコンパイル WinAVRを使いました。以下は筆者環境でのバッチファイルです。

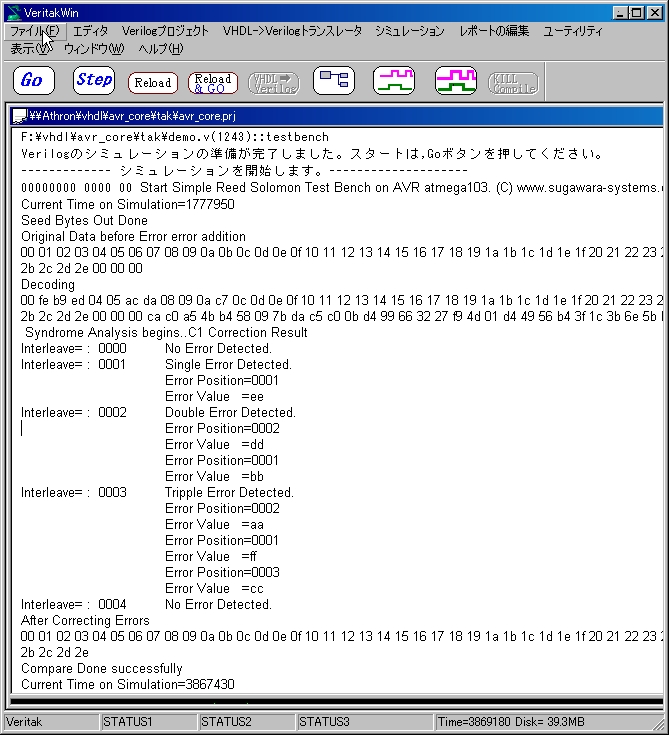

テストベンチTOPがありませんので追加しました。 ・トランスレート(VHDL->Verilogに変換します。) translated.vが生成されます。 ・Verilogソース追加修正 log2__等によるビット幅指定→[15:0]にします。 ramsize → 1024*64 にします。 デバッガを入れ込みます。 以上の修正したもの->demo.v ・シミュレーション arv_core.prj をLoadVerilogします。 しばらくしてからコンソールにメッセージが現れます。StartUpでRAMの初期化に時間がかかるようです。  Test時間は、3867430-1777950=2.1msとなりました。 予想以上に速いです。16ビットバスとハーバードアーキテクチャ、そしてコンパイラが優秀なのでしょう。 |