Xilinx DDR3 偺MIG丂Simulation

Veritak偱偼丄SecureIP偱埫崋壔偝傟偨IP偼丄僔儈儏儗乕僔儑儞偡傞偙偲偑偱偒傑偣傫丅

SecureIP偱埫崋壔偝傟偰偄側偄IP偼丄僔儈儏儗乕僔儑儞偡傞偙偲偑偱偒傑偡偑丄尰帪揰偱偼丄廋惓偑昁梫偱偡丅

埲壓偼丄椺偱偡丅

侾丏Mig33偱丂Virtex6丂DDR3偱惗惉

埲壓偼丄mig33偑惗惉偟偨僨乕僞僔乕僩偱偡丅

CORE Generator Options:

Target Device : xc6vlx550t-ff1759

Speed Grade : -2

HDL : verilog

Synthesis Tool : XST

MIG Output Options:

Module Name : mig33

No of Controllers : 1

Selected Compatible Device(s) : --

Hardware Test Bench : enabled

FPGA Options:

Clock Type : Differential

Debug Port : OFF

Extended FPGA Options:

DCI for DQ,DQS/DQS#,DM : enabled

DCI for Address/Control : enabled

/*******************************************************/

/* Controller 0 */

/*******************************************************/

Controller Options :

Memory : DDR3_SDRAM

Design Clock Frequency : 1875 ps (533.33 MHz)

Memory Type : Components

Memory Part : MT41J128M8XX-15E

Equivalent Part(s) : MT41J128M8HX-15E

Data Width : 8

ECC : Disabled

Data Mask : enabled

ORDERING : Normal

Memory Options:

Burst Length (MR0[1:0]) : 8 - Fixed

Read Burst Type (MR0[3]) : Sequential

CAS Latency (MR0[6:4]) : 8

Write Recovery (MR0[11:9]) : 5

Output Drive Strength (MR1[5,1]) : RZQ/7

Rtt_NOM - ODT (MR1[9,6,2]) : RZQ/4

Rtt_WR - Dynamic ODT (MR2[10:9]) : Dynamic ODT off

FPGA Options:

IODELAY PERFORMANCE MODE : HIGH

Selected Banks and Pins usage :

Data :bank 26(40) -> Number of pins used : 12

Address/Control:bank 25(40) -> Number of pins used : 27

System Clock :bank 35(40) -> Number of pins used : 7

BUFR :bank 25(40) -> Number of pins used : 1

BUFIO :bank 26(40) -> Number of pins used : 1

Total IOs used : 47

俀丏僜乕僗偺廋惓

俀丏侾丂ISE11.1/12.1嫟捠

俀丏侾丏侾丂價僢僩暆偺廋惓/僌儕僢僠偺彍嫀

unisim偺oserdes1.v丗

`ifdef Veritak

output [1:0] qwc, qrd;//價僢僩暆愰尵傪壓偵崌傢偣傞

`else

output qwc, qrd;

`endif

output rd_gap1, extra;

reg [1:0] qwc;

reg [1:0] qrd;

`ifdef VeritakSV

assign OQ = oq_out;//VeritakSV偼丄SpecifySection傪僒億乕僩

`elsif Veritak

assign #(100) OQ = oq_out;//姷惈抶墑偱丄僌儕僢僠偵傛傞岆僩儕僈傪彍嫀

`else

assign OQ = oq_out;//TAK

`endif

assign SHIFTOUT1 = shiftout1_out;

assign SHIFTOUT2 = shiftout2_out;

assign TFB = tfb_out;

`ifdef VeritakSV

assign TQ = tq_out;//TAK

`elsif Veritak

assign #(100) TQ = tq_out;

`else

assign TQ = tq_out;//TAK

`endif

specify

( CLK => OFB) = (0, 0);

( CLK => OQ) = (100, 100);

( CLK => SHIFTOUT1) = (0, 0);

( CLK => SHIFTOUT2) = (0, 0);

( CLK => TFB) = (0, 0);

( CLK => TQ) =(100, 100);

( CLKPERF => OFB) = (0, 0);

( CLKPERF => OQ) = (100, 100);

( CLKPERF => SHIFTOUT1) = (0, 0);

( CLKPERF => SHIFTOUT2) = (0, 0);

( CLKPERF => TFB) = (0, 0);

( CLKPERF => TQ) = (100 , 100);

( CLKPERFDELAY => OFB) = (0, 0);

( CLKPERFDELAY => OQ) = (100, 100);

( CLKPERFDELAY => SHIFTOUT1) = (0, 0);

( CLKPERFDELAY => SHIFTOUT2) = (0, 0);

( CLKPERFDELAY => TFB) = (0, 0);

( CLKPERFDELAY => TQ) = (100, 100);

( T1 => TQ) = (0, 0);

`ifdef VeritakSV

specparam PATHPULSE$ = 1;

`else

specparam PATHPULSE$ = 0;

`endif

endspecify

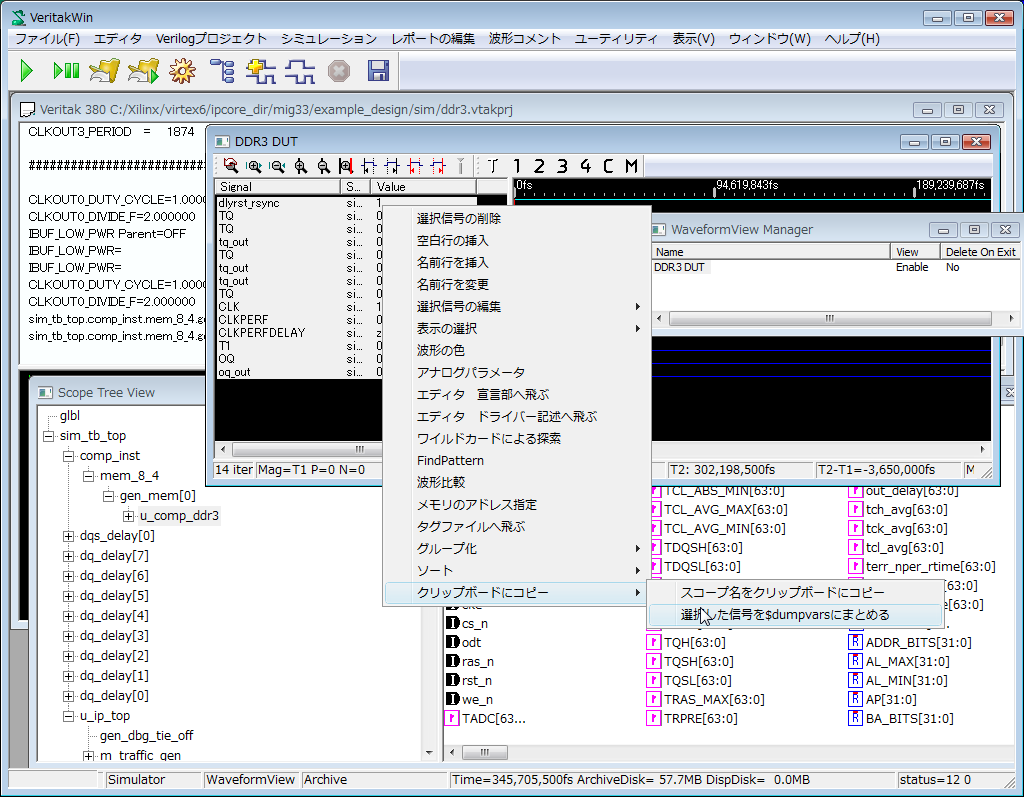

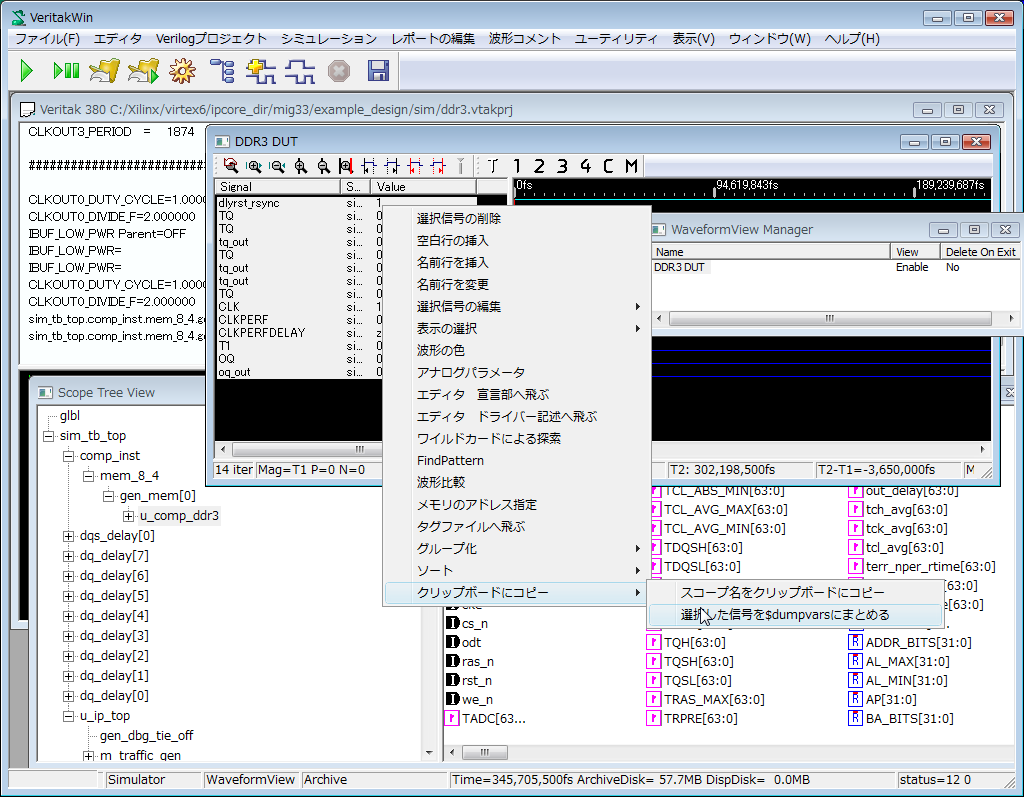

俁丏Veritak僾儘僕僃僋僩僼傽僀儖

丂example_design/sim 僼僅儖僟偵偍偄偰僾儘僕僃僋僩傪惗惉偟偰偔偩偝偄丅埲壓偼丄偙偪傜偱峴偭偨僾儘僕僃僋僩傪僄僋僗億乕僩偟傑偟偨丅

-Define

x8

-Define

sg15E

-Define

x1Gb

wiredly.v

ddr3_model.v

glbl.v

sim_tb_top.v

../rtl/phy/rd_bitslip.v

../rtl/phy/circ_buffer.v

../rtl/phy/phy_ck_iob.v

../rtl/phy/phy_clock_io.v

../rtl/phy/phy_control_io.v

../rtl/phy/phy_data_io.v

../rtl/phy/phy_dly_ctrl.v

../rtl/phy/phy_dm_iob.v

../rtl/phy/phy_dq_iob.v

../rtl/phy/phy_dqs_iob.v

../rtl/phy/phy_init.v

../rtl/phy/phy_ocb_mon.v

../rtl/phy/phy_pd.v

../rtl/phy/phy_pd_top.v

../rtl/phy/phy_rdclk_gen.v

../rtl/phy/phy_rdctrl_sync.v

../rtl/phy/phy_rddata_sync.v

../rtl/phy/phy_rdlvl.v

../rtl/phy/phy_read.v

../rtl/phy/phy_top.v

../rtl/phy/phy_write.v

../rtl/phy/phy_wrlvl.v

../rtl/ui/ui_wr_data.v

../rtl/ui/ui_cmd.v

../rtl/ui/ui_rd_data.v

../rtl/ui/ui_top.v

../rtl/traffic_gen/write_data_path.v

../rtl/traffic_gen/afifo.v

../rtl/traffic_gen/cmd_gen.v

../rtl/traffic_gen/cmd_prbs_gen.v

../rtl/traffic_gen/data_prbs_gen.v

../rtl/traffic_gen/init_mem_pattern_ctr.v

../rtl/traffic_gen/mcb_flow_control.v

../rtl/traffic_gen/mcb_traffic_gen.v

../rtl/traffic_gen/pipeline_inserter.v

../rtl/traffic_gen/rd_data_gen.v

../rtl/traffic_gen/read_data_path.v

../rtl/traffic_gen/read_posted_fifo.v

../rtl/traffic_gen/sp6_data_gen.v

../rtl/traffic_gen/tg_status.v

../rtl/traffic_gen/v6_data_gen.v

../rtl/traffic_gen/wr_data_gen.v

../rtl/ip_top/memc_ui_top.v

../rtl/ip_top/clk_ibuf.v

../rtl/ip_top/ddr2_ddr3_chipscope.v

../rtl/ip_top/example_top.v

../rtl/ip_top/infrastructure.v

../rtl/ip_top/iodelay_ctrl.v

../rtl/ip_top/mem_intfc.v

../rtl/controller/col_mach.v

../rtl/controller/arb_mux.v

../rtl/controller/arb_row_col.v

../rtl/controller/arb_select.v

../rtl/controller/bank_cntrl.v

../rtl/controller/bank_common.v

../rtl/controller/bank_compare.v

../rtl/controller/bank_mach.v

../rtl/controller/bank_queue.v

../rtl/controller/bank_state.v

../rtl/ecc/ecc_merge_enc.v

../rtl/ecc/ecc_buf.v

../rtl/ecc/ecc_dec_fix.v

../rtl/ecc/ecc_gen.v

../rtl/phy/phy_pd_top.v

../rtl/phy/phy_ocb_mon_top.v

-lib_dir

../../../../../11.1/ISE/verilog/src/unisims

../rtl/controller/round_robin_arb.v

../rtl/controller/mc.v

../rtl/controller/rank_cntrl.v

../rtl/controller/rank_common.v

../rtl/controller/rank_mach.v

係丏攇宍娤應

僥僗僩儀儞僠偼丄柍尷儖乕僾偵側偭偰偄傞傛偆偱偡偺偱丄揔摉側偲偙傠偱巭傔偰偔偩偝偄丅

傑偨丄攇宍慡晹傪娤應偡傞偲Disk偑偡偖堦攖偵側偭偰偟傑偆偺偱丄攇宍慖戰傪峴偆偐乮僾儘斉偺傒乯丄傑偨偼丄壓偺傛偆側曽朄偱VCD偱娤應偟偰偔偩偝偄丅

俆丏侾俀丏侾偺廋惓

丂侾乯glbl.v 偺僐僺乕

丂丂丂mig33 偱sim 僼僅儖僟壓偵惗惉偝傟傑偡偑丄屆偄傛偆偱偡丅侾俀丏侾偺unisim僼僅儖僟偵偁傞傕偺傪僐僺乕偟偰抲偒姺偊偰偔偩偝偄丅

丂俀乯偦偺傑傑偱偡偲丄僄儔乕偱巭傑偭偰偟傑偄Sim偑恑傒傑偣傫偺偱丄嫮惂揑偵憱傜偣傞僷僢僠偱偡丅

丂丂丂unisim mmcm_adv.v;

`define FORCE_SIM

`ifdef FORCE_SIM

localparam M_MIN = 4.000;

`else

localparam M_MIN = 5.000;

`endif

`ifdef FORCE_SIM

chk_ok = para_real_range_chk(CLKFBOUT_MULT_F, tmp_string, 4.000, 64.000);

`else

chk_ok = para_real_range_chk(CLKFBOUT_MULT_F, tmp_string, 5.000, 64.000);

`endif