VeritakユーザF.A.Q.s

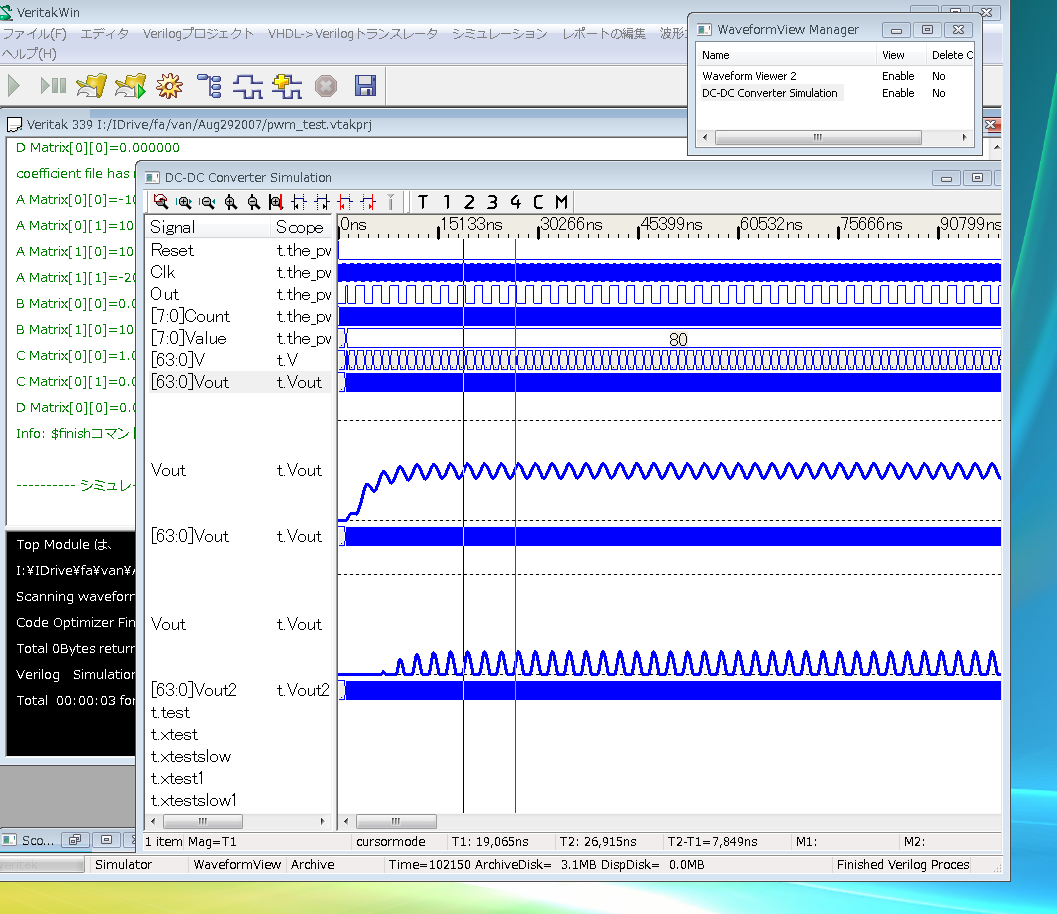

User F.A.Q.1 DCMのシミュレーーション

User F.A.Q.2 inout の記述

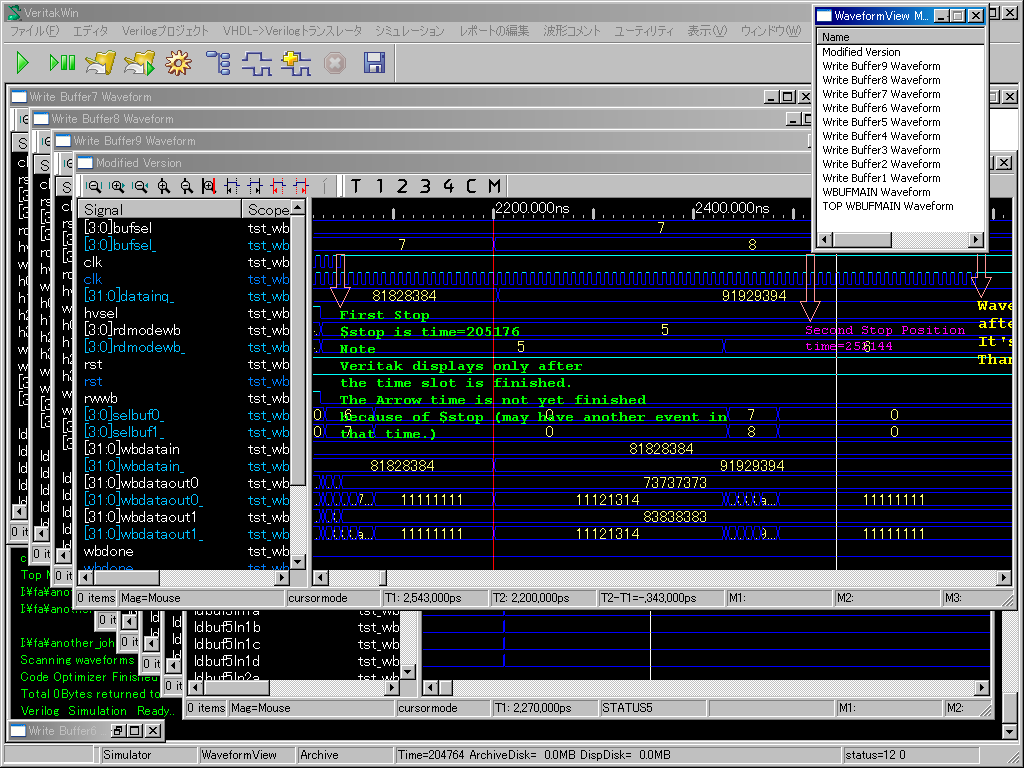

User F.A.Q.3 シミュレーション最後の波形

User Attached 4.

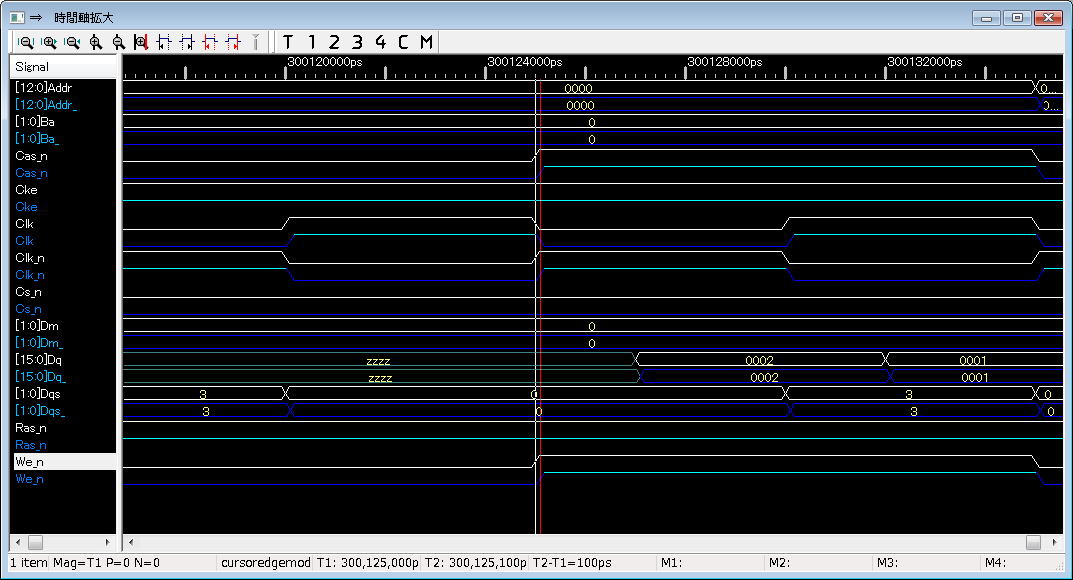

全くSIM波形は同じように見えるが..

よく見ると時間軸拡大 100psの差が観測される。(Veritakでは、Specify Sectionの遅延値100psを無視するため。)

#!/bin/sh var3="Display_Epilog" # "で囲んでください" var4="DISPLAY_MESSAGE" var5="MEM_FILE=\"write_random.txt\"" # Define中の"は、\"としてください ./VERITAK2 --W "..\samples" "..\samples\sample2.v" ./VERITAK2 --W "..\samples" --D "Display_Epilog" --D "DISPLAY_MESSAGE" --i "include" "hardware/alu.v" "test bench/alu_bench.v" >log1.txt ./VERITAK2 --W "..\samples" --D $var3 --D $var4 --i "include" "hardware/alu.v" "test bench/alu_bench.v" >> log1.txt ./VERITAK2 --W "..\samples" --i "include" "hardware/alu.v" "test bench/alu_bench.v" >>log1.txt ./veritak2 --F --NS --NB --B --C0 --M0 --a --ST --W "..\regression_test\plusarg" --D "MEM_FILE=\"write_random.txt\"" "plusarg_test7.v" >> log1.txt ./veritak2 --F --NS --NB --B --C0 --M0 --a --ST --W "..\regression_test\plusarg" --D $var5 "plusarg_test7.v" >> log1.txt