次の例は、`define の使用例です。

処理後のpreout.vを見てみると

17章 コンパイラDirective

以下のような`xxx でをコンパイラ Directiveといいます。

赤字は、Veritakでサポートしていません。

| `celldefine `default_nettype `define `else `elsif `endcelldefine `endif `ifdef `ifndef `include `line `nounconnected_drive `resetall `timescale `unconnected_drive `undef |

大方は、プロプロセッサで処理されますが、そうでないのもあります。シミュレータのなかには、プリプロセッサを実装しない処理系もあるようですが、Veritakでは、プリプロッサを使っているのでプリプロセッサで処理される方から説明します。

下のコンパイラDirectiveに関しては、プリプロセッサで処理しています。処理した結果は、Veritak プロジェクトオプションををONにすると 「preout.v」というファイルができます。このファイルを、シミュレータ本体は処理します。プロジェクトでたくさんのファイルが入っていても、最終的には、一つのファイル preout.vになります。マクロやifdefが多いと読むのに疲れますが、そういうときは、preout.vを見てみるのもいいでしょう。`line以外は、処理されて消えているので読みやすいです。(ただしコメントは消えてしまいます。)

また、preout.v単体でも走らせることができます。(Veritak 1.45より)

| `define `else `elsif `endif `ifdef `ifndef `include `line `undef |

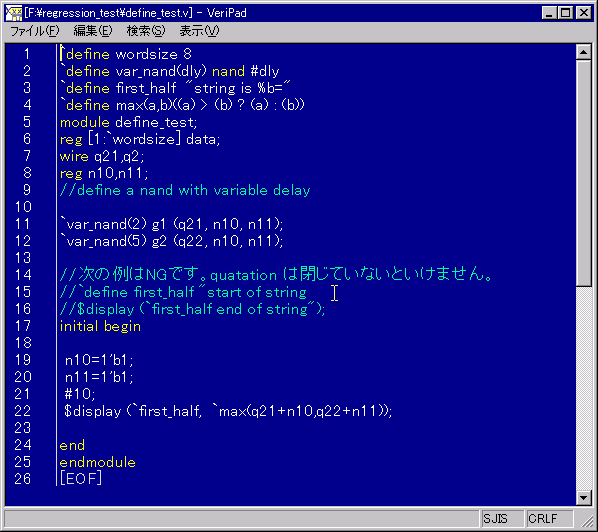

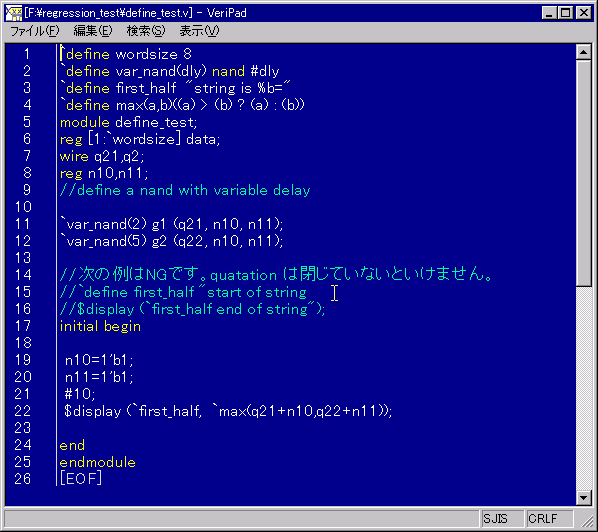

次の例は、`define の使用例です。

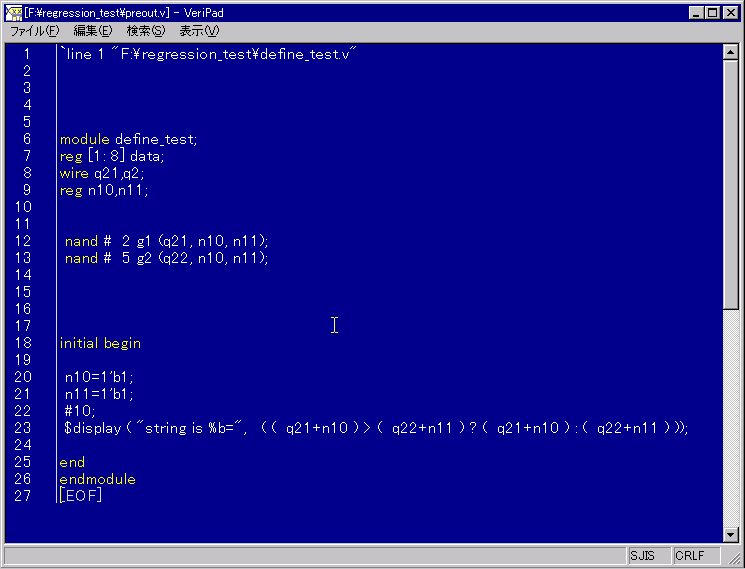

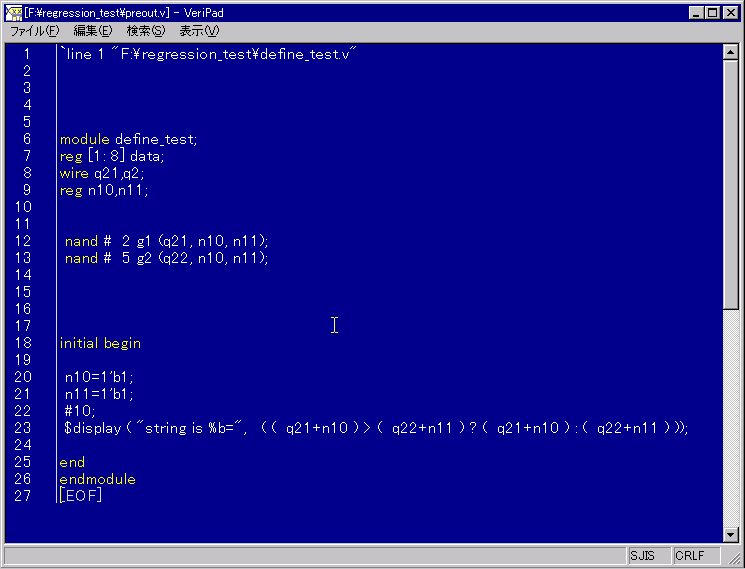

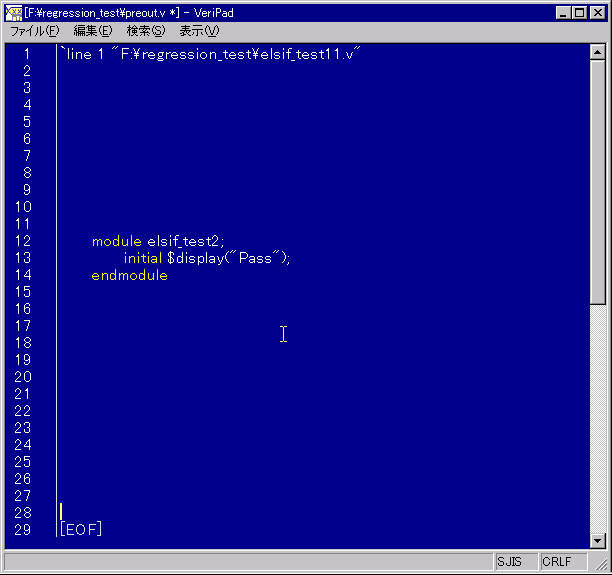

処理後のpreout.vを見てみると

となります。どちらが読みやすいでしょうか?

シミュレータ本体が読むのは、処理後のソースで、`define で定義した情報は残らないので、デバッグもやりずらいです。verilog2001になってparamter

が強力になっているので、できるだけparameter で書けるところはparameterにするべきでしょう。

'ifdef 'else 'ifndef 'elsif 'endif 'undef

これらは、Cで想像される機能に同じです。

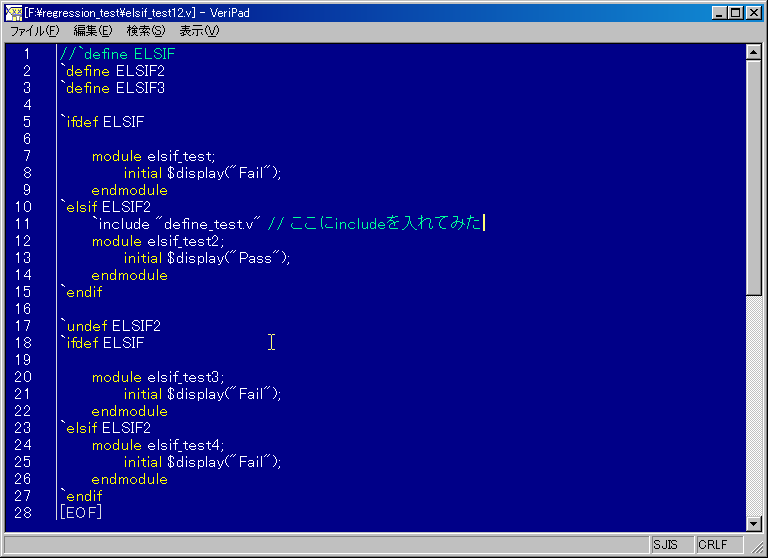

例によって処理前と

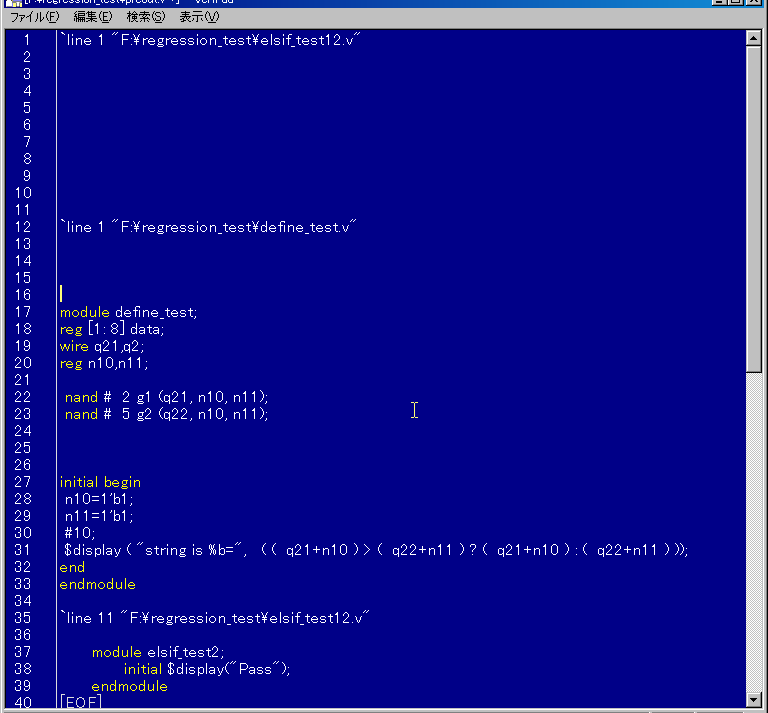

処理後です。

ところで、preout.vでは、`lineが付加されています。シミュレータ本体は、これで、ファイル名と行番号を管理しています。

`include もCのそれと同じです。

例によって

処理前と

処理後です。

このように、プリプロセッサの役目は、「後段のコンパイラが処理しやすい形に整形する」、ということにあります。

以上で、プリプロセッサに係わるところはおわりです。

`default_nettype

これは、暗黙のネットを禁止します。

`default_nettype none

としておく暗黙ネットのところでコンパイルエラーにします。

//Jan.14.2005 Make sure compile error occurs.

module default_nettype_test; wire a=c; endmodule

|

これだとVeritakの場合、

F:\regression_test\default_nettype_test.v(3)::Info: 構文解析中です。 構文解析が終了しました。スコープを生成中です。 parameterを評価中です。 generateを評価中です。 reg/wire..を評価中です。 moduleを評価中です。 F:\regression_test\default_nettype_test.v(7)::Error: c :Implicit Net はdefault_net==noneにより禁止されています。 Elaboration Phaseでエラーが発生しました。 コンパイル未完了のまま終了しました。 |

になります。これが厭な場合は、記述しないか

| `default_nettype wire |

とすると、暗黙宣言があってもエラーになりません。

`timescale

T.B.D.