3.10丂怣崋柤曐懚

丂僾儘僕僃僋僩傪嶌惉偟偰偍偔昁梫偑偁傝傑偡丅

丂丂曐懚偟偨偄夋柺偱

丂丂Verilog僾儘僕僃僋僩亖亜僾儘僕僃僋僩偺曇廤亖亜SaveProject傪墴偟傑偡偲丄偦偺偲偒偺WaveformView偺夋柺忋偺儕僗僩柤偑僾儘僕僃僋僩僼傽僀儖偵曐懚偝傟傑偡丅

亙椺亜丂

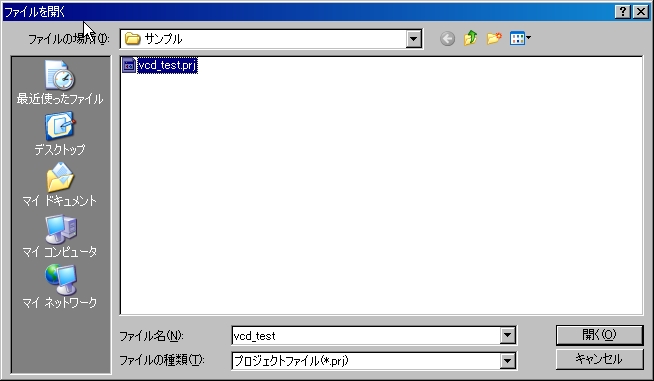

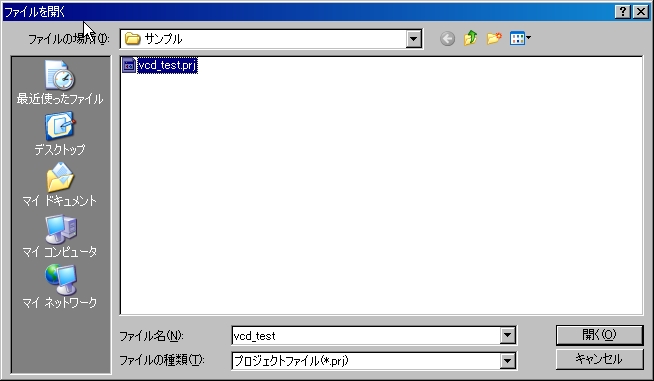

丂丂僒儞僾儖僼僅儖僟偵丄僾儘僕僃僋僩僼傽僀儖偵vcd_test.prj偑偁傝傑偡丅LoadProject偟偰傒傑偟傚偆丅

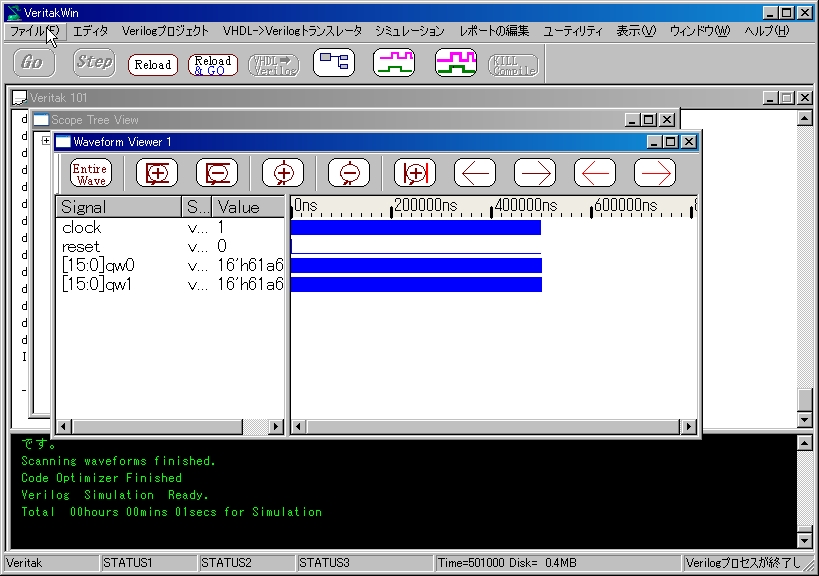

Go儃僞儞傪墴偡偲僔儈儏儗乕僔儑儞偑巒傑傝WaveformView傪弌偟傑偡丅

偙傟偼丄僾儘僕僃僋僩僼傽僀儖偵怣崋柤偺儕僗僩偑Save偝傟偰偄偨偨傔偱偡丅偙偺傛偆側攇宍偺弌偰偄傞忬懺偱丄

Verilog僾儘僕僃僋僩亖亜僾儘僕僃僋僩偺曇廤亖亜SaveProject傪墴偟傑偡偲丄偦偺偲偒偺WaveformView偺夋柺忋偺儕僗僩柤偑僾儘僕僃僋僩僼傽僀儖偵曐懚偝傟傑偡丅夋柺悢偼暋悢壜擻偱偡丅夋柺傪徚偟偨偄応崌偼丄夋柺傪徚偟偰SaveProject偡傟偽傛偄偱偡丅

嬻敀峴偵柤慜傪偮偗傞椺偱偡丅乮埲壓偼丄Veritak丂Version1.12A埲崀偱偡丅乯

杮椺偼丄僾儘僕僃僋僩偱偡丅僒儞僾儖僼僅儖僟偵擖偭偰偄傞"mul_div_test.prj"傪乽Load丂Verilog乿偟傑偡丅丂偪側傒偵mul_div_module偼

H8屳姺僾儘僕僃僋僩偱愝寁偟偨忔彍嶼儐僯僢僩偱偡丅

Go偝偣偰傒傑偟傚偆丅偡傞偲壓偺WaveformView偑尰傟傑偡丅

偙偺怣崋偺暲傃偲柤慜偼丄僾儘僕僃僋僩僼傽僀儖偵Save偝傟偰偄偨偨傔尰傟傑偟偨丅

柤慜偺晅偗曽傪傗偭偰傒傑偟傚偆丅嬻敀峴偺憓擖傪傑偢峴偄傑偡丅

師偵憓擖偟偨嬻敀峴偺忋偵柤慜傪偮偗傑偡丅

僟僀傾儘僌儃僢僋僗偵柤慜傪彂偒傑偡丅

埲忋偱柤慜偺晅偗曽偼廔傢傝傑偟偨丅偙偺忬懺偱師夞偺僔儈儏儗乕僔儑儞偺堊偵丄Disk偵怣崋偺暲傃傪Save偟偰偍偒傑偟傚偆丅

Verilog僾儘僕僃僋僩亖亜僾儘僕僃僋僩偺曇廤偱Disk偵Save偟偰偍偒傑偡丅側偍丄Load丂Project偲丂Reload偺堘偄偼丄Load丂Project偑Disk偐傜

撉傒弌偡偺偵懳偟丄Reload偼丄Disk傪撉傒弌偝偢偵儊儌儕忋偺愝掕偱嵞儘乕僪偟傑偡丅

拲堄丗![]()

丂僐儞僷僀儖僄儔乕偵側傞偲乭夋柺偑側偄乭偲偄偆忬懺偑丄儊儌儕偵巆偭偰偟傑偄傑偡丅嵞搙丄怣崋儕僗僩偺View傪弌偡偵偼丄Reload偱偼側偔丄Verilog僾儘僕僃僋僩=>Load丂Project傪峴偭偰丄Disk忋偐傜Load偡傞傛偆偵偟偰偔偩偝偄丅傑偨丄Verilog僾儘僕僃僋僩=>柤慜傪晅偗偰曐懚丂偱丄揔媂丄Project僼傽僀儖傪Save偟偰偍偔偙偲偱丄Save帪偺丄攇宍儕僗僩偺桳柍丒暲傃丄偦偺懠愝掕傪曐懚偟偰偍偔偙偲偑偱偒傑偡丅乮Version1.19埲崀丅偨偩偟丄僼僅儖僟偼丄嵟弶偵嶌偭偨僼僅儖僟偺傒偵Save壜擻偟偰偁傝傑偡丅偙傟偼丄Verilog僼傽僀儖偺憡懳埵抲娭學傪曐偮偨傔偱偡丅乯

ScopeView偺怴婡擻

ScopeView偺丂乽CLOCK乿偲乽Stop丵State乿偼柧帵揑側愰尵偑偝傟偰偄傑偣傫丅Reg愰尵偼丄R丄Wire愰尵偼W偵側偭偰偄傑偡偺偱

傢偐傝傗偡偄偲巚偄傑偡丅Verilog偱偼丄愰尵偟偰偄側偔偲傕1價僢僩偺wire偲傒側偝傟偰暥朄僄儔乕偵側傜側偄応崌傕偁傝傑偡偺偱

婰弎偑姰惉偟偨傜堦搙尒偰偍偔偲傛偄偱偟傚偆丅乮僶僌庢傝偺彆偗偵側傞偐傕偟傟傑偣傫丅乯