3.7 プロジェクトファイル

複数のVerilogファイルで、デザインを構成するときは、プロジェクトファイルを作成する必要があります。

(Veritak独自の仕様で他のシミュレータとは互換性がありません。)

ただし、`include文でファイルが明示的に結合して場合は、プリプロセッサで処理されますので、プロジェクトにする必要はなく、前述の単一ファイル例と同じように「ファイルを開く」でOKです。

プロジェクトの例としてOpencoresで公開されているもので説明します。

準備として、Opencoresから、generic_memories.tarとminirisc.tar

を頂いてきます。

Veritakプロジェクトを作成したものを含めてここに置いておきます。なお、miniriscは、PIC 16C57コンパチブルなコアだそうです。

解凍したら、すでに作成してあるプロジェクトを開いてシミュレーションしてみましょう。

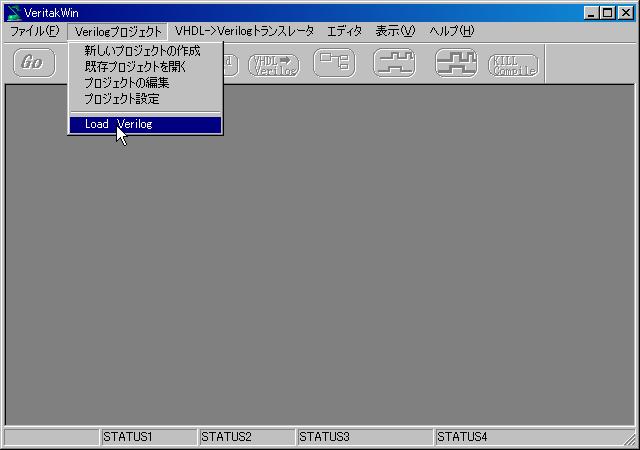

既存のプロジェクトをロードするには、Load Verilogを押します。

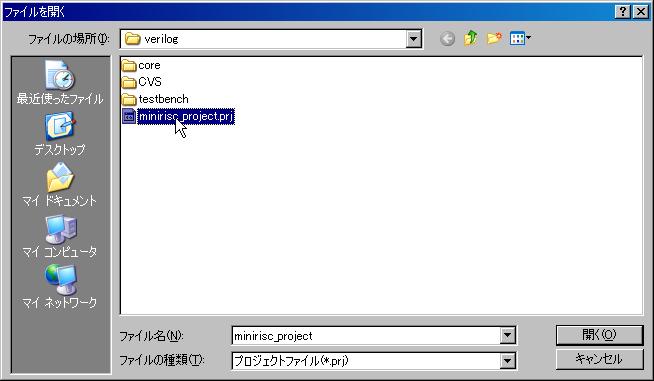

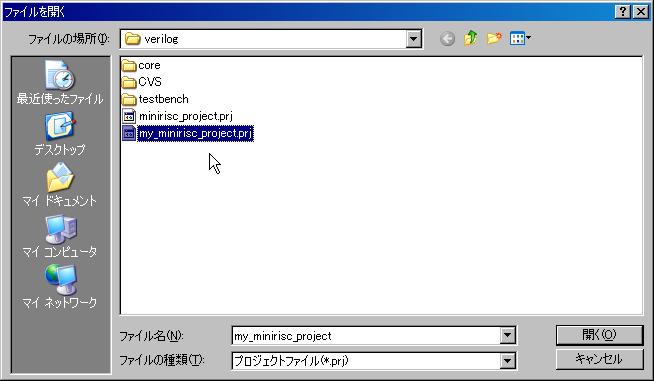

minirisc\verilog\の下にプロジェクトがあるので開いてみます。

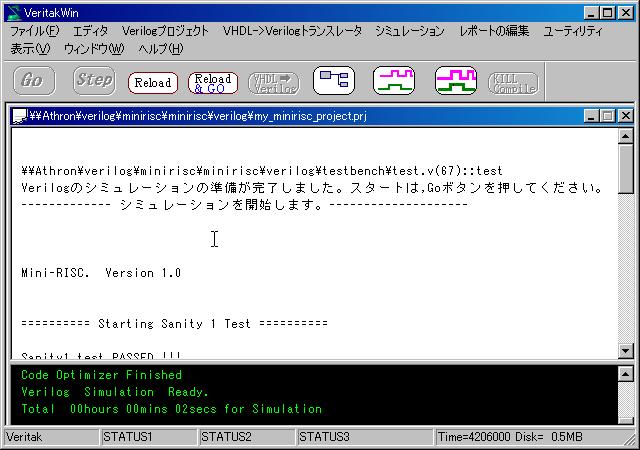

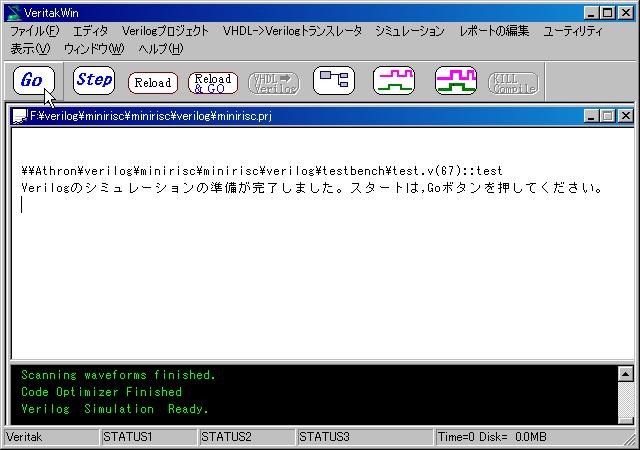

コンパイルは始まりSimulation Readyとなりました。Goボタンを押します。

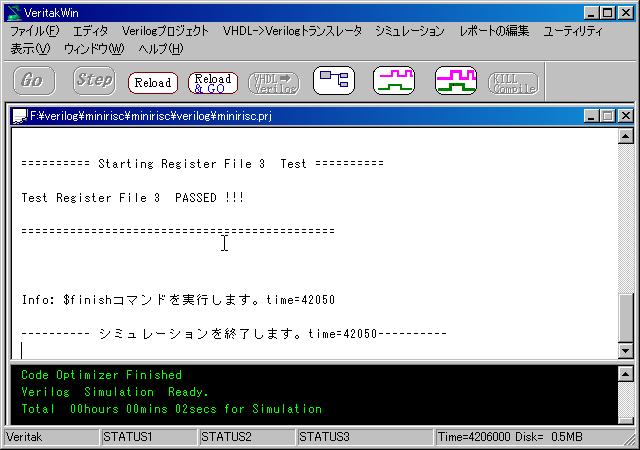

マシンにもよりますが、1秒足らずでシミュレーションは完了し次の画面となります。

シミュレーション中の波形は、メモリを除いて全部残っているので、WaveformViewerで覗いてみてください。

さて本題のプロジェクトの作成ですが、上のプロジェクトを実際に作ってみることにしましょう。

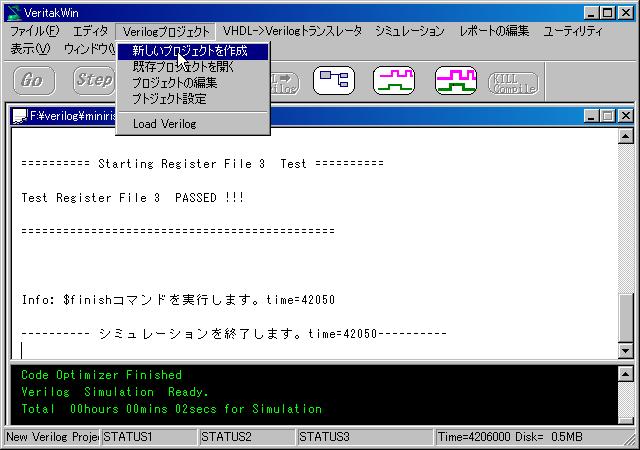

「新しいプロジェクトを作成」を押します。

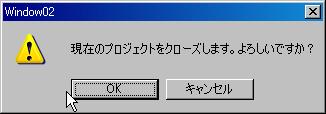

すると、次のように聞かれるので「OK」を押します。

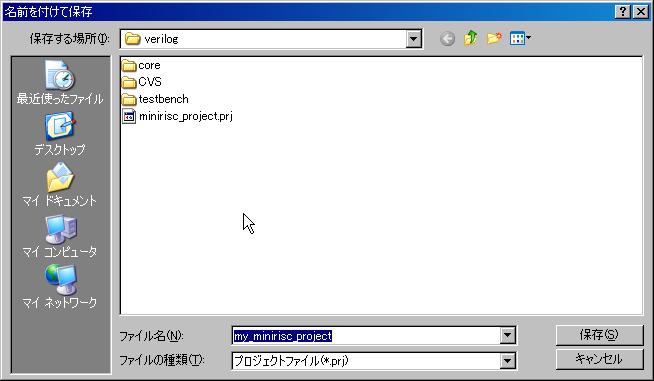

新しく作成するプロジェクトの名前を適当に決めて保存します。

このとき、このプロジェクトは、下画面のフォルダ位置に保存しないと、後でコンパイルエラーとなります。

というのは、HDLファイルの中でROMファイルを読み込んでいますが、基準パスがここになっているようです。

Veritakは、プロジェクトファイルの位置を基準パスとしています。

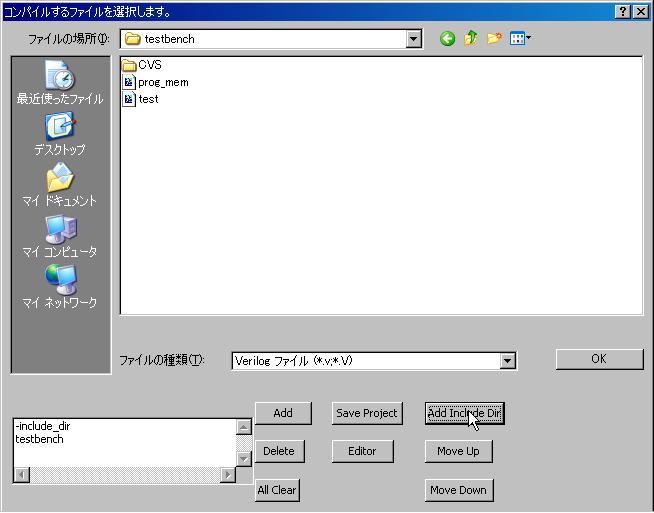

次にコンパイルするファイルの選択の画面になりますが、その前にソースのフォルダが二つに分かれていますので、

AddIncludeDirボタンで、フォルダのINCLUDEを指定してやります。

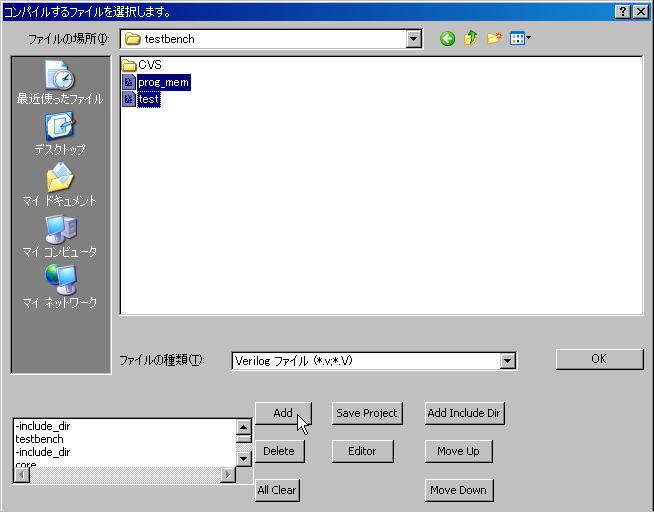

まずは、testbenchフォルダです。

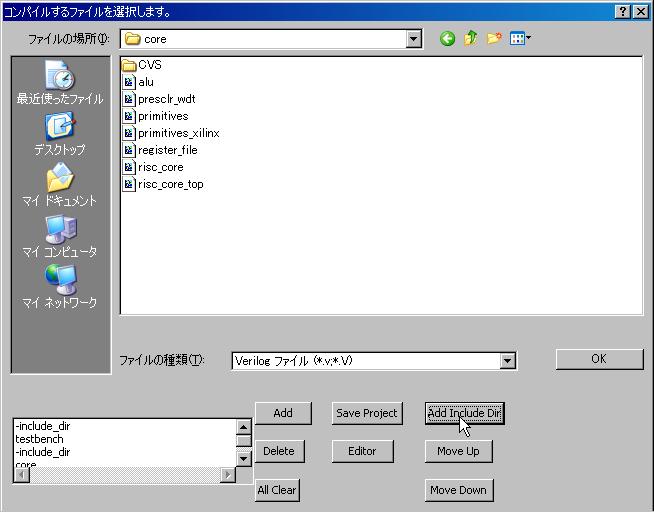

次にコアフォルダです。

こうしておくとファイルが見つからない場合、Veritakは、Includeフォルダも検索するようになります。

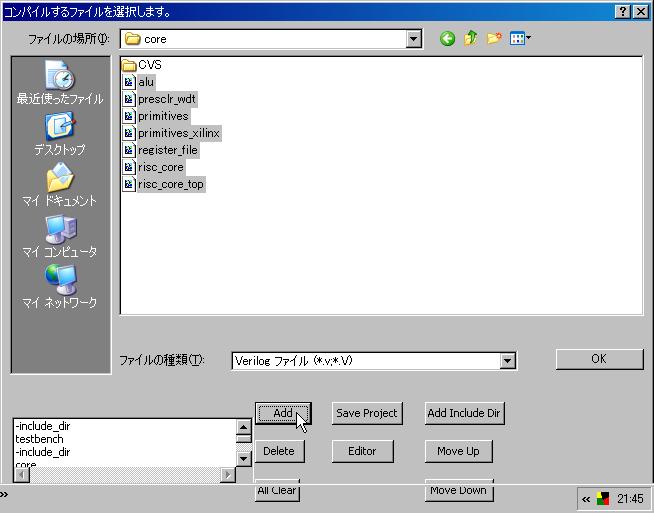

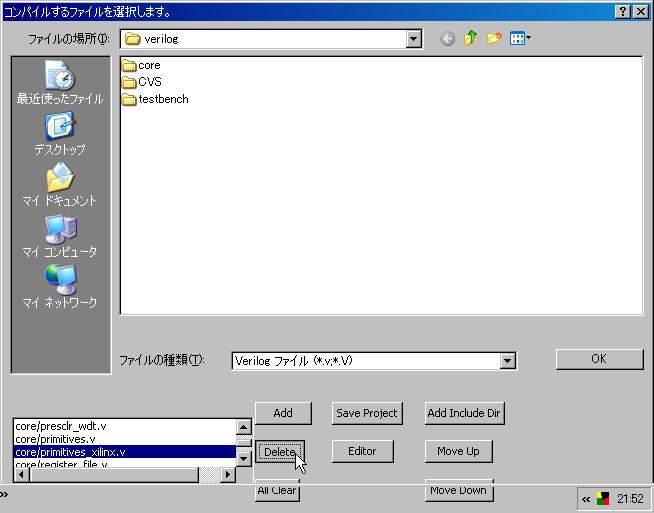

次にソースファイルを指定して「Add」します。

「Add]します。

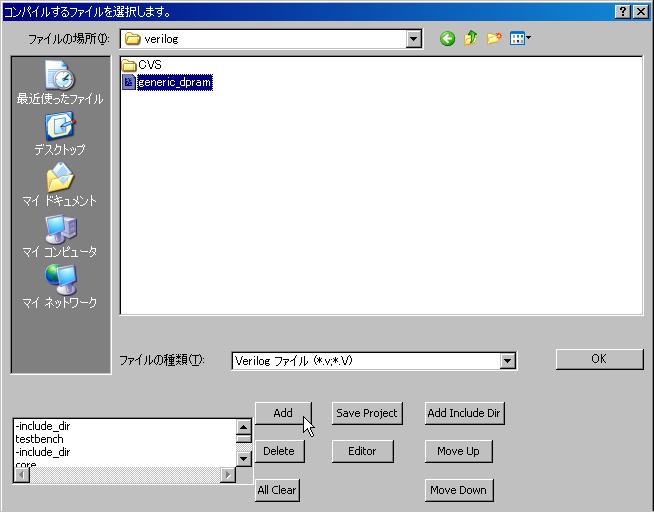

「Add]します。generic_memoriesの下にあります。

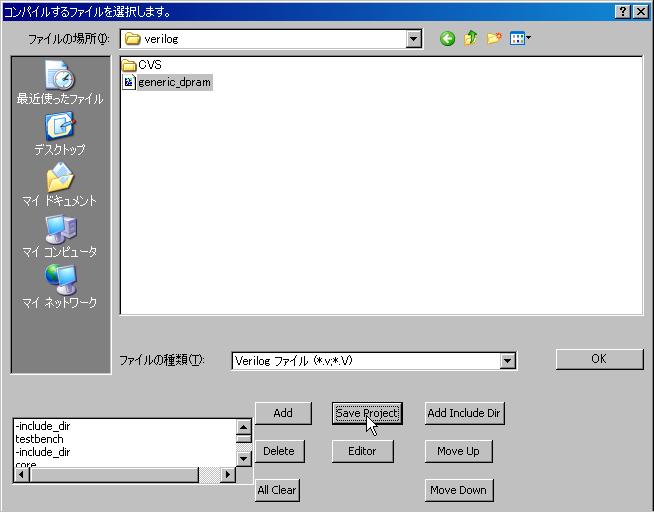

以上で、ソースファイルの指定が終わりましたが、この段階では、まだファイルの中身は空です。「SaveProject]を押して初めて書き込まれます。

「OK]を押します。

作ったプロジェクトを「ロード]してみます。

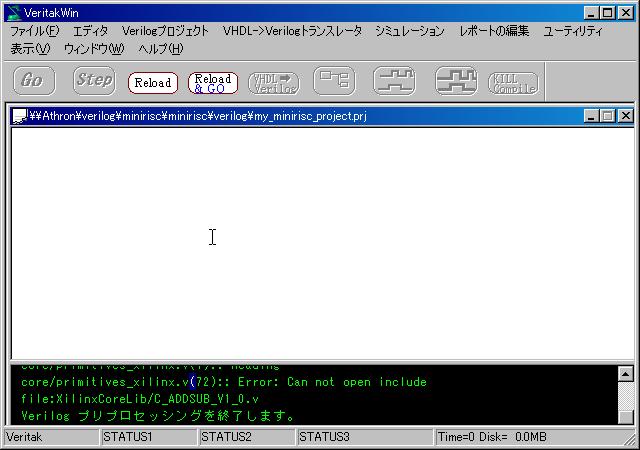

コンパイルエラーとなってしまいました。

Xilinxのファイルが余計だったようなので、「Delete」してコンパイル対象から外します。外した後、「Save Project」を忘れないでください。

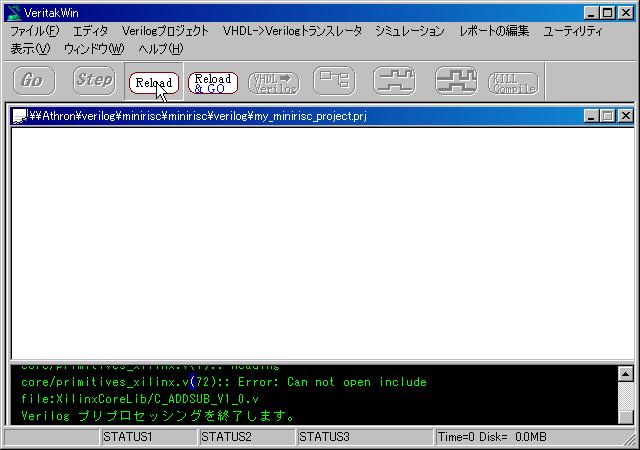

「Reload」ボタンを押します。

今度はOKになりました。