RTL プロジェクト

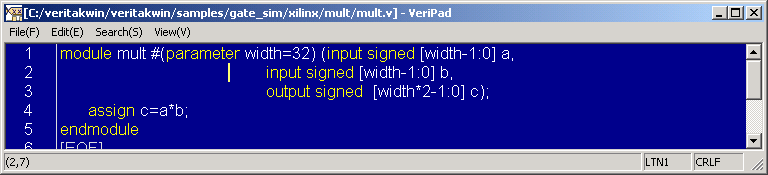

32x32bits 乗算器を設計してみましょう。.

Load Project "RTL_mult_test.vtakprj", 後 Go を押すと

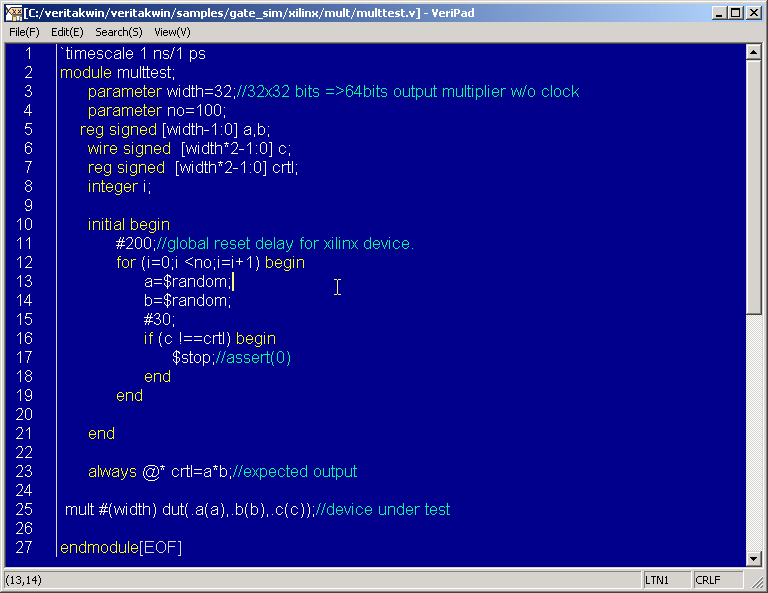

テストベンチソースは、

符号付乗算器のソースです。

Synthesis

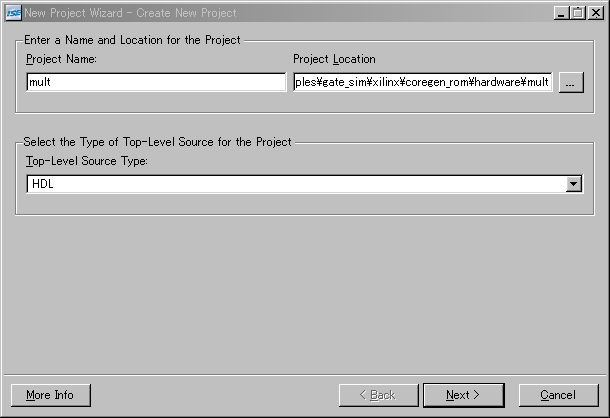

Xilinx のプロジェクトを作ります。

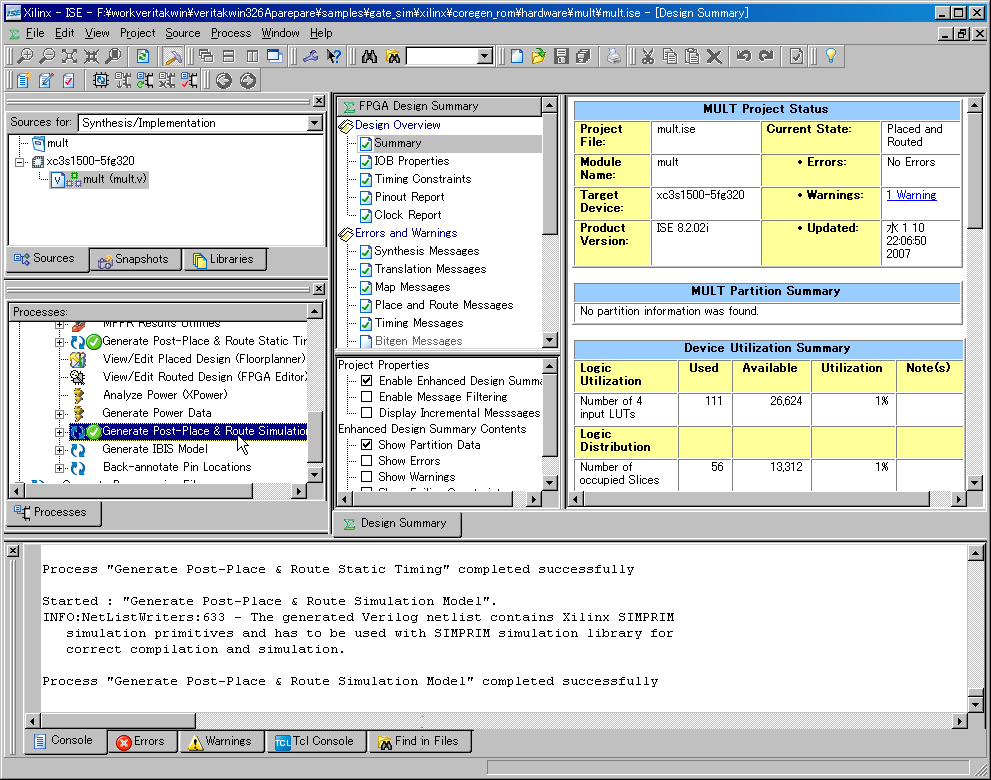

最終的なパスディレイは、Xilinx Timing analyzerを用いて知ることができます。これが、デザインの最大可能周波数を与えます。

Veritak ゲートシミュレーション

プロジェクト

ゲートシミュレーションのプロジェクトを作成します。SDFファイルを読み込む関係で、Xilinx

ツールが生成するフォルダnetgenの上に作成する必要があります。

既に作成済みのプロジェジェクトがありますのでそれを開いて見ます。Verilog プロジェクト=>既存プロジェクトを開くで、GateMult.vtakprjを開きます。

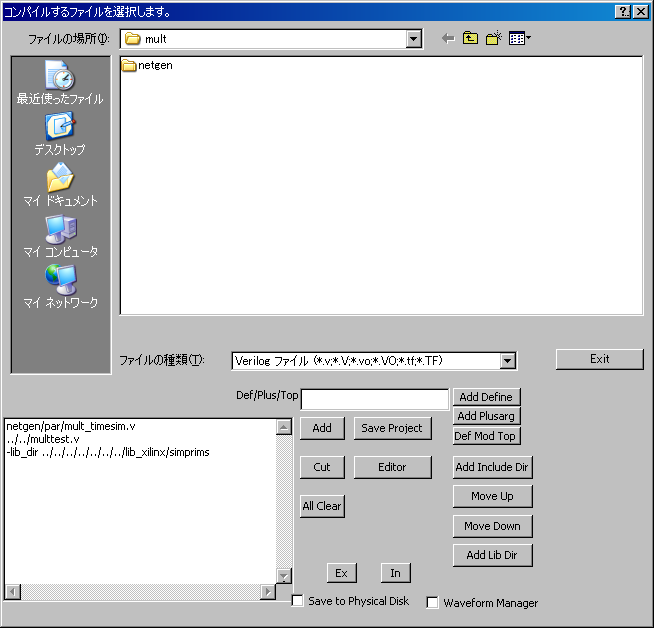

下で、mult_time_sim.v は、Xilinxツールが生成したレイアウト後のネットリストファイルです。parフォルダにはSDFファイル(遅延情報ファイル)も生成されています。SDFファイルは、mult_time_sim.vの中で呼ばれているのでここでは、SDFファイルを入れる必要はありません。

次のmult_test.v は、RTLシミュレーションのテストベンチです。そのまま流用します。

最後のsimprimes は、XilinxツールにあるXilinxのプリミティブライブラリです。お使いの環境でパスは変わってきますので、環境にあわせて修正してください。 下で、Xilinx

のsimprimesフォルダに入ってAddLibDirで設定されます。

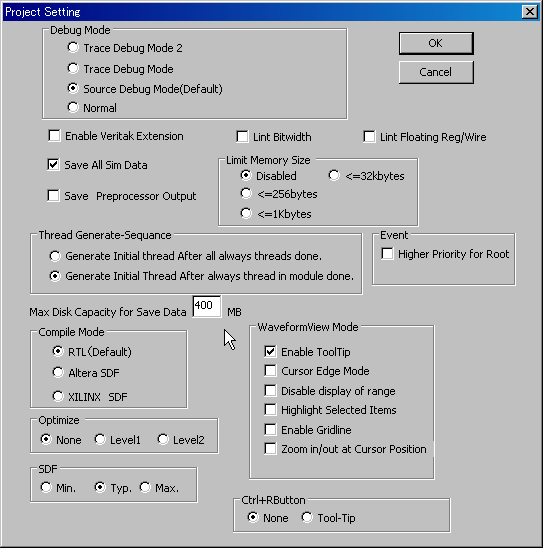

SDF ファイルでは、遅延値がMIN/TYP/MAXの3種類あります。XILINXとAlteraに関しては、今のところ、全て同じ値なので、どれを選んでも同じですが、プロジェクト設定ー>SDFで、TYP を選択しておきましょう。

また、コンパイルモードは、XILINXゲートシミューレーションではXilinx SDFを選択してください。

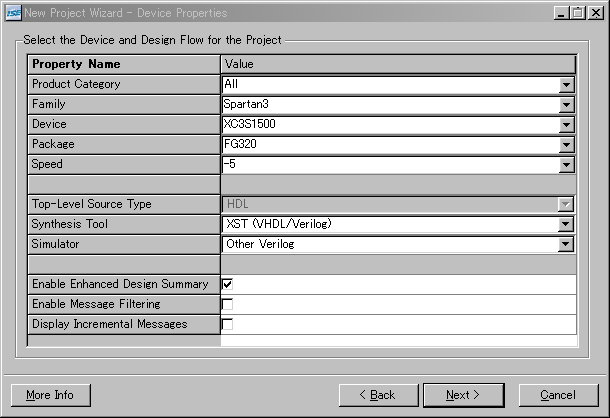

Simulator はOther Verilogにします。

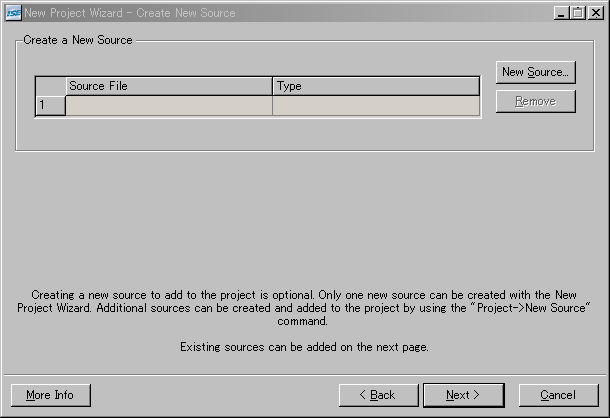

ここではなにも指定しません。

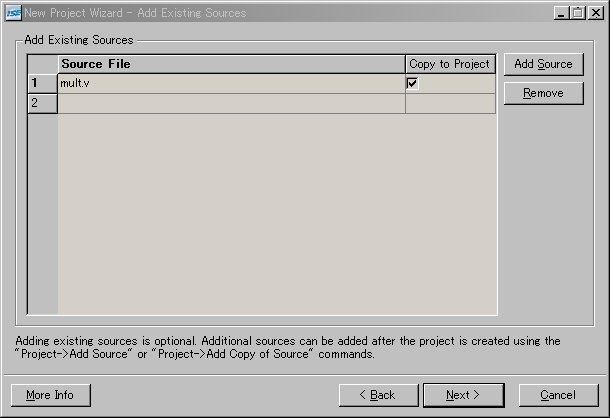

合成対象となるソースを指定して完了です。

Generate Post Place&Route Simulation Model..を右クリック,Runを押して、合成及び、ポストルート後のシミュレーションファイルを生成させます。

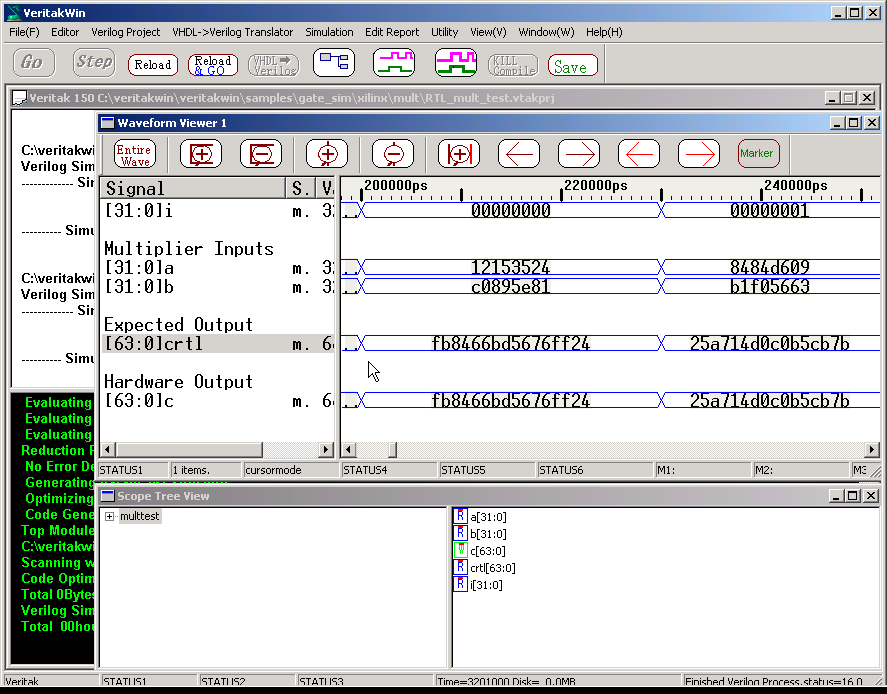

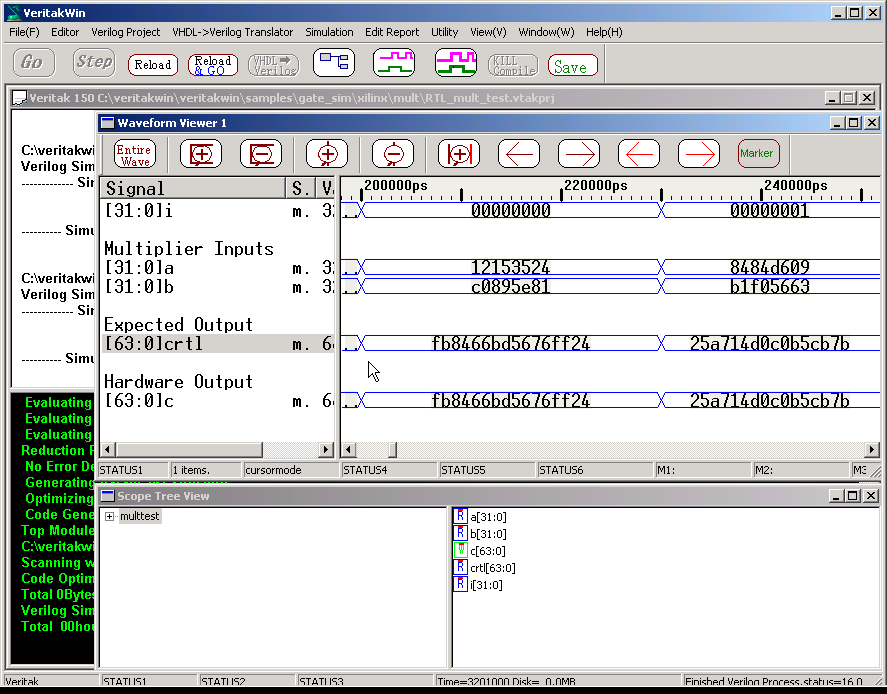

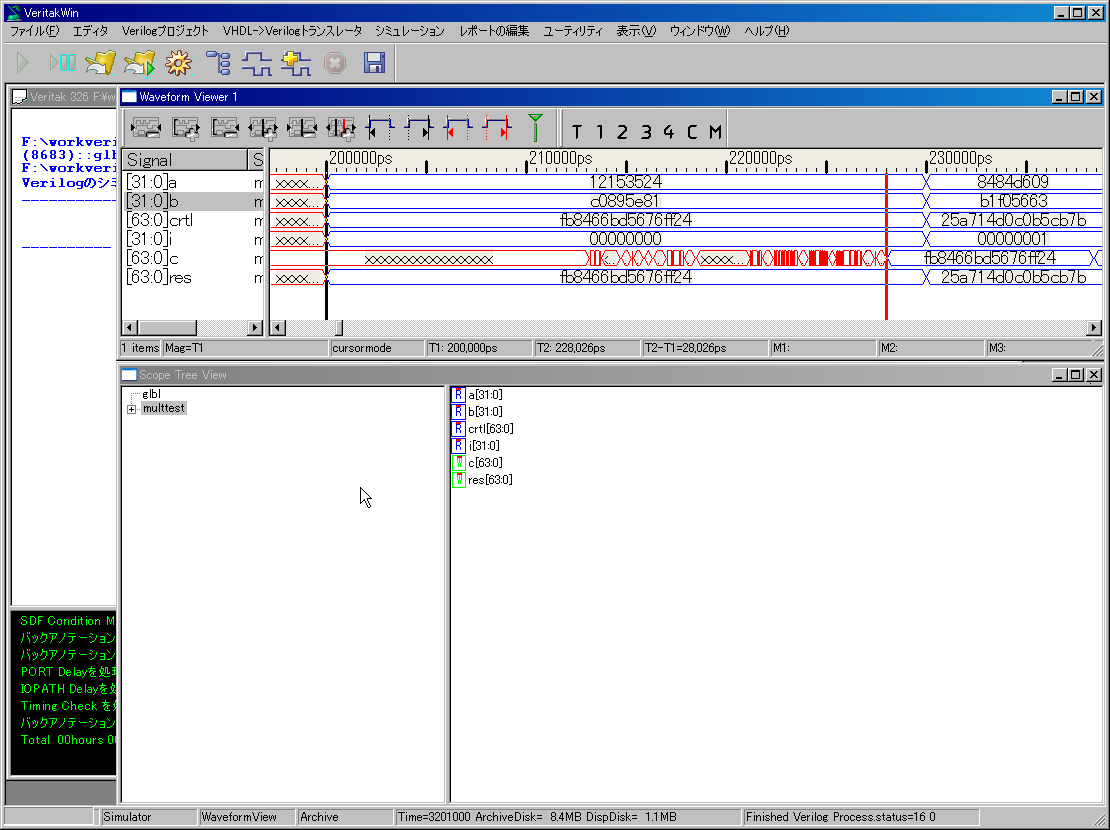

プロジェクトをLoad Verilog するとシミュレーションが走ります。下で28ns後に乗算結果がセトルしている様子が分かります。