2.4.1.2 複数のVCDのプロジェクト

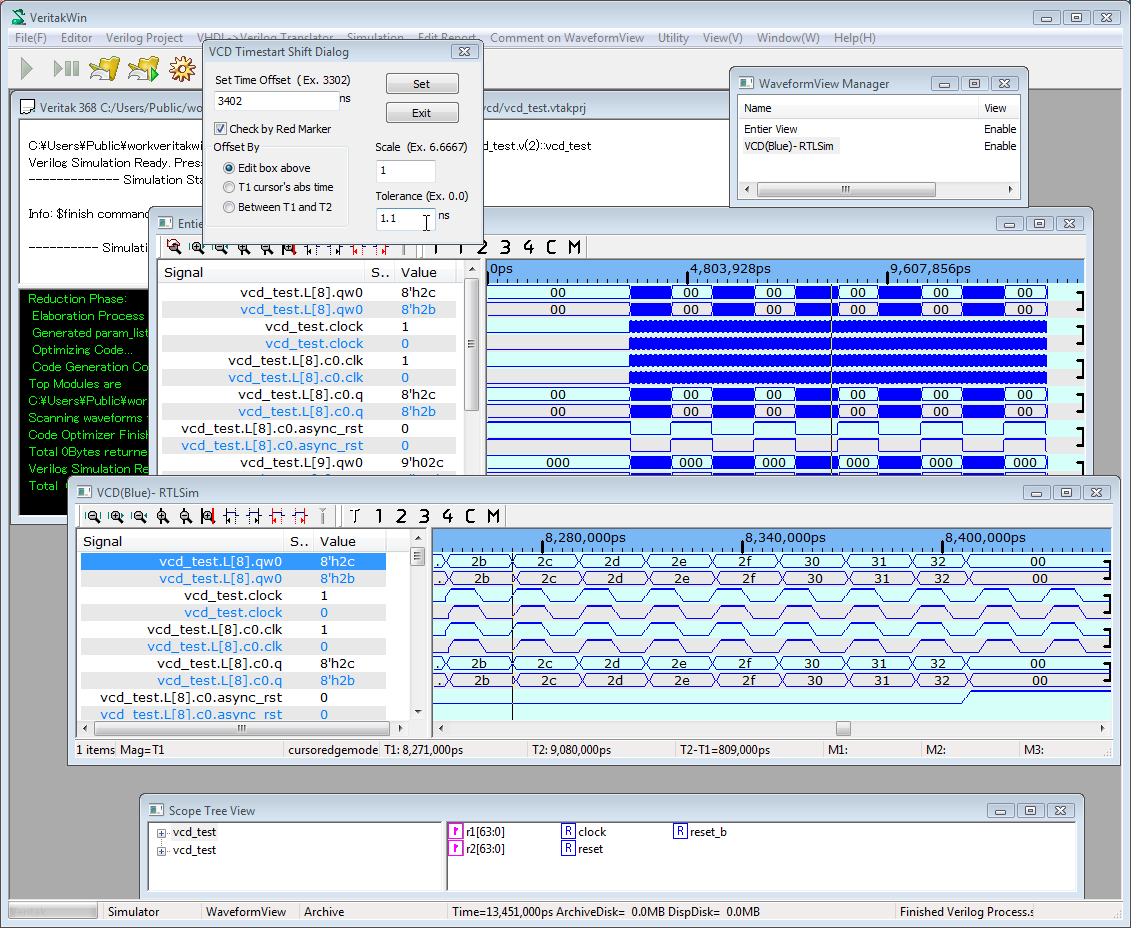

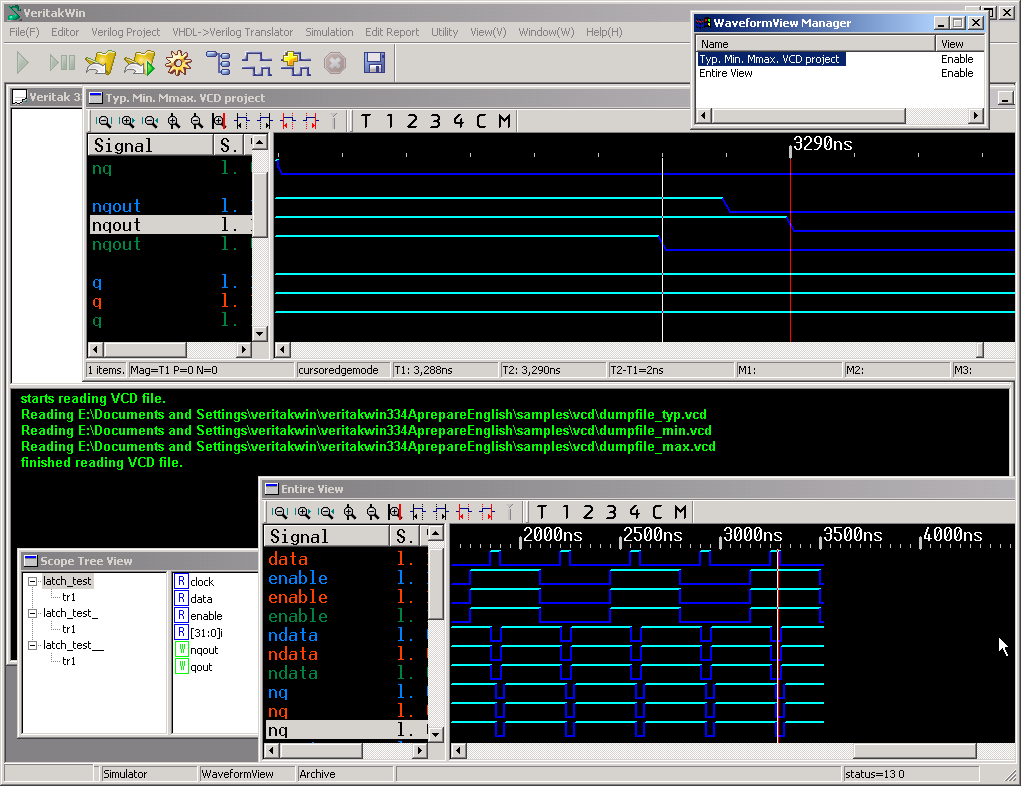

3つまでのVCDファイルをViewできます。例として、samples\vcdフォルダにあるvcd_only.vtakprjを開いてみてください。

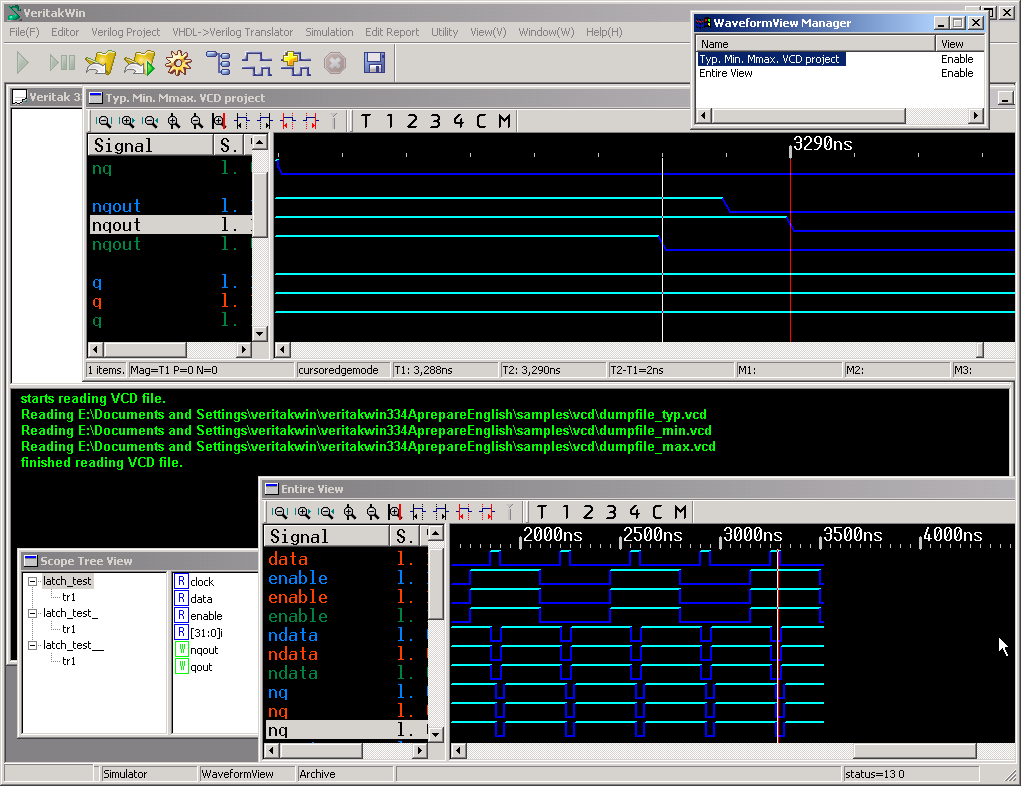

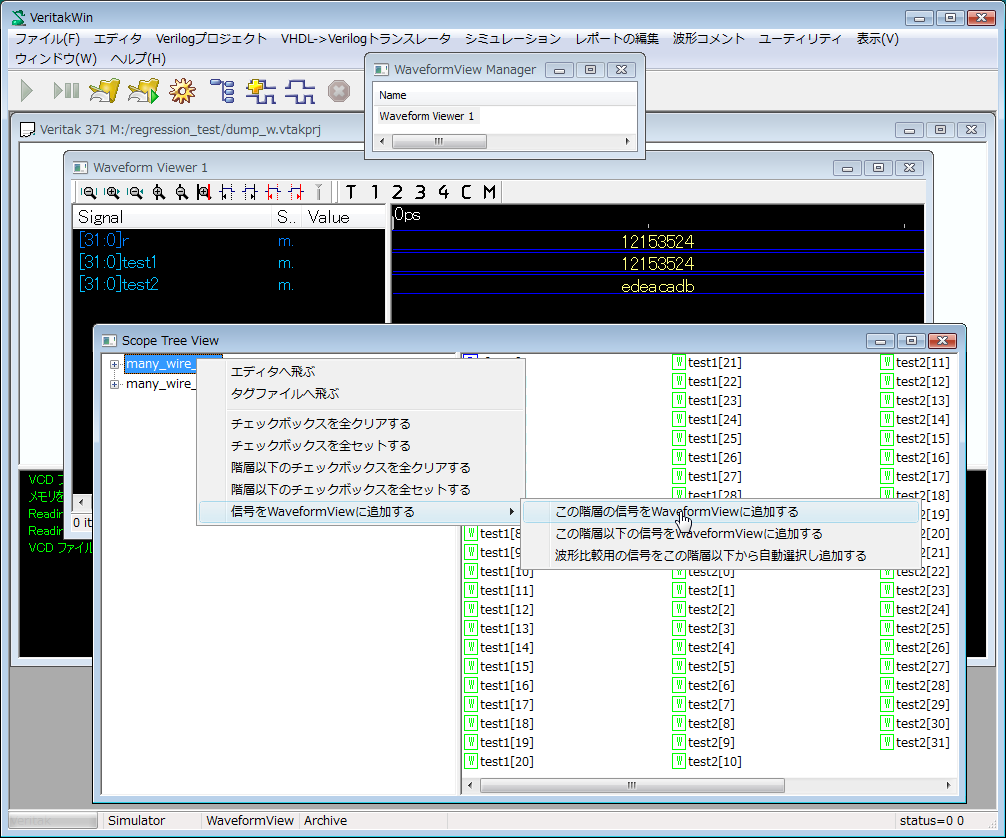

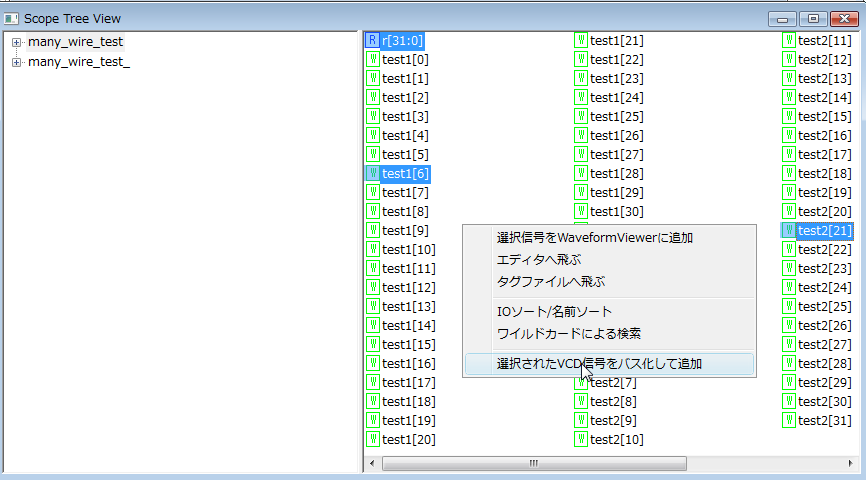

ScopeTreeViewで次のようになります。この例の場合、3つのファイルは、同一のソースから生成したもので、インスタンス名が同一です。そのため、内部的に区別するためにTopSopeに接尾辞’_’を付け加えています。

3つの信号は、ListView上の色で分けています。並び順のソートは、「信号名でソート」で行ってください。

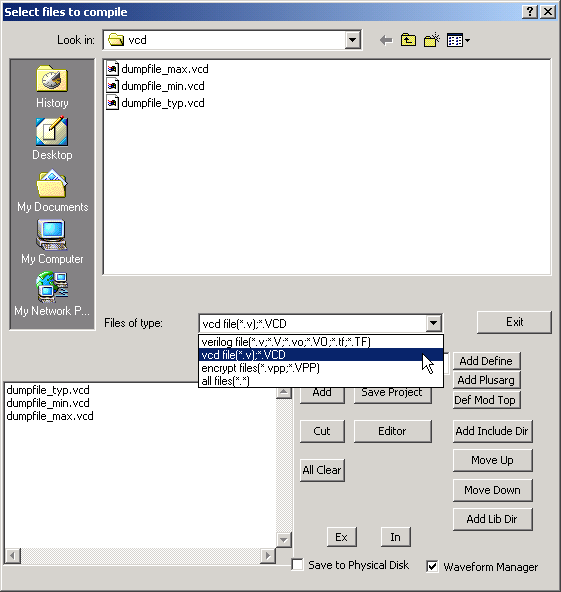

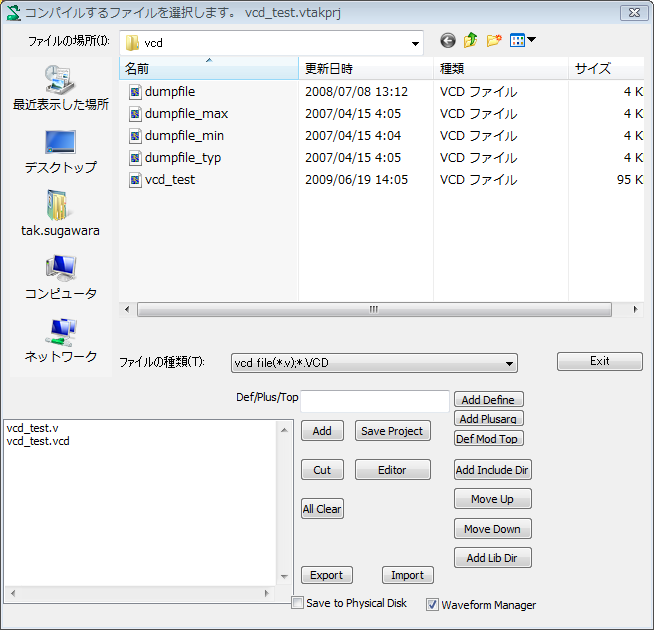

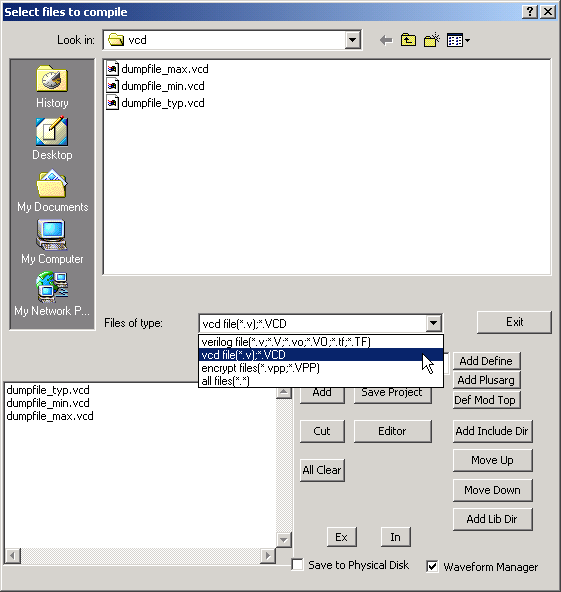

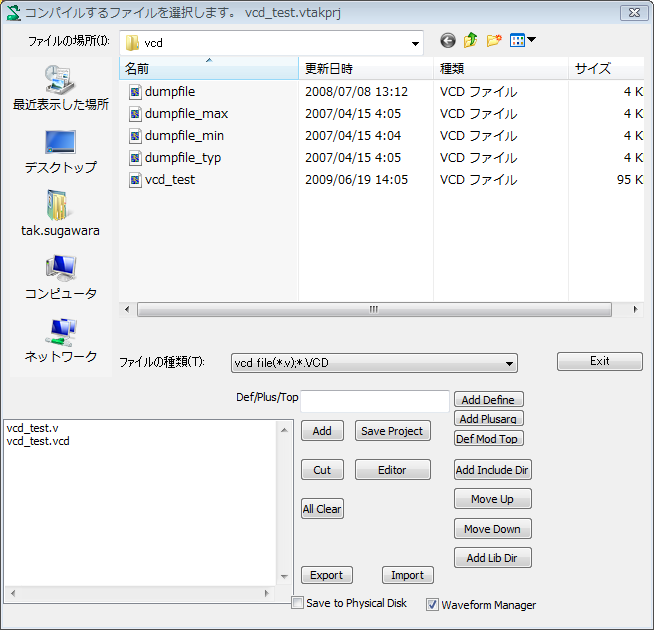

<プロジェクトの作成方法>

基本的に、通常のVerilogソースと同様です。

TIPS

- 容量の大きいVCDファイルについては、プロジェクト設定UseDiskをオンにしてください。(Pro-Version Only)

- VCDプロジェクトのSave/Restoreは、サポートしていません。

- 複数のVCDファイルまたは、Verilogソースでは、タイムスケールを同じにしてください。

- VCDファイル合計容量の7倍のDisk領域を確保していますので、それ以上のDisk残があることを御確認ください。(500MBのVCDファイルが3つですと500x3x7=10.5GBのDisk容量が必要です。

- コンパイル時間は、1GBのVCDファイルで10分位かかります。

- Re-Compileボタンで再コンパイルになります。VCDファイルのみのプロジェクトで、Reloadボタンを押してもなにも起こりません。

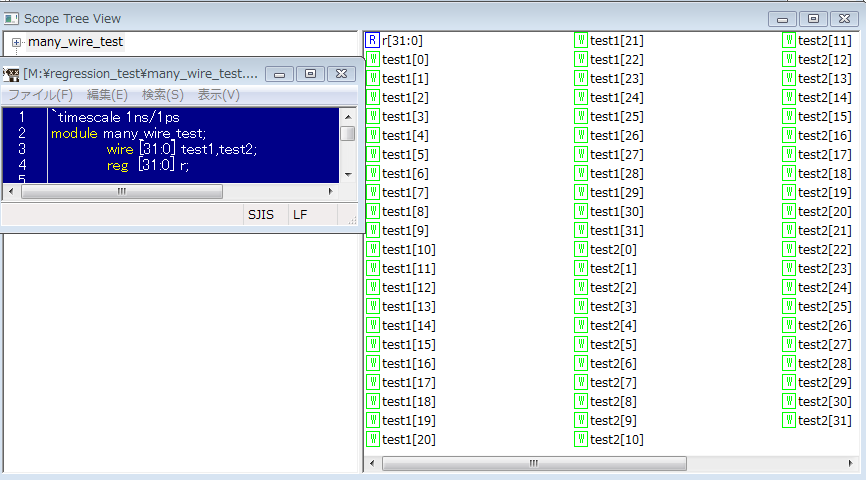

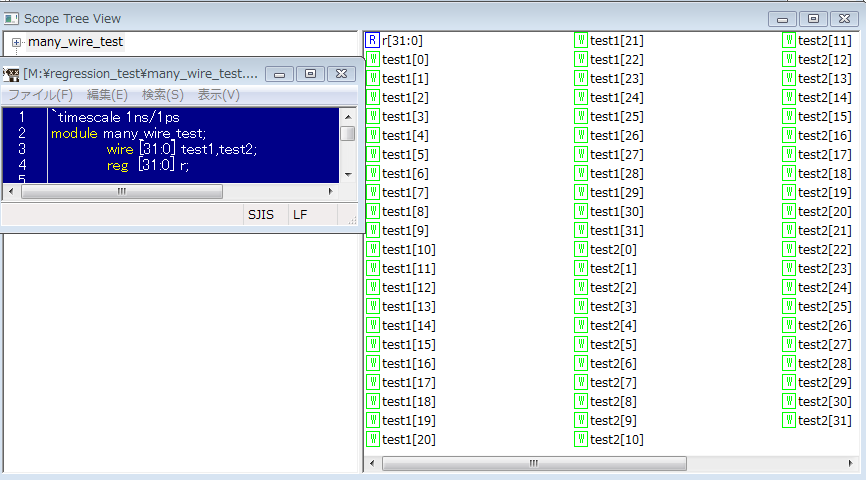

2.4.1.3自動グループ化機能

ModelSim(TM)生成のVCDは(Verilog/VHDL)、wireバス信号が個別の1ビット信号で出力されます。

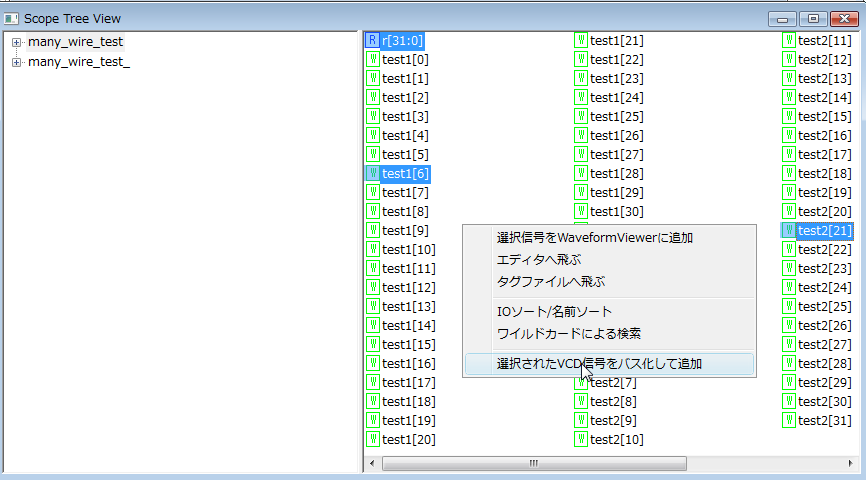

これを、バスとして観測したい場合は、信号を選択(Ctrl+左クリック/Shift+左クリック)して、下の右クリックでメニューをだし、選択されたVCD信号をバス化して追加 をクリックします. (このとき、ビット展開信号については、任意の1ビットの選択で十分です。)

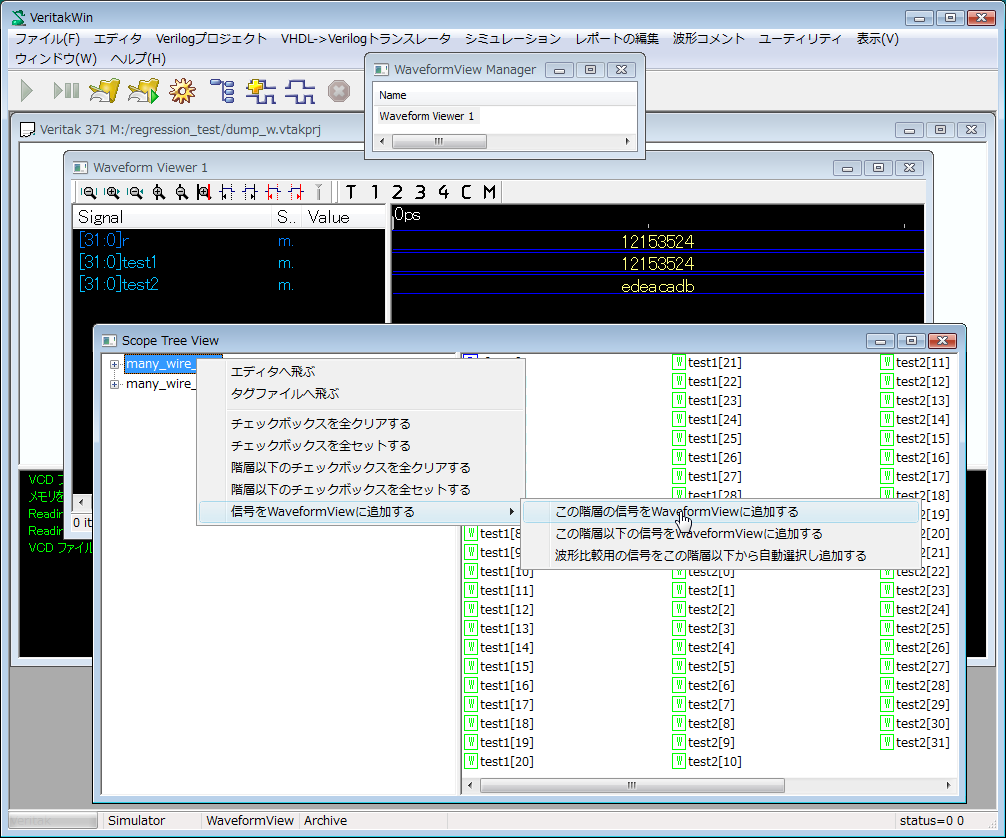

これで、test1/test2は、32ビットバスとしてWaveformViewerに追加されました。(下図)

なお、スコープ内の全信号を追加したい場合は、下のように左ペインのツリーを選択し、左クリックでメニューを出して追加するのが便利です。この場合も、バスとして、追加されます。

2.4.1.4 VCD波形とVeritak波形を一緒に表示する

通常のプロジェクトと同様に、VCDファイルをプロジェクト中に定義するだけでよいです。

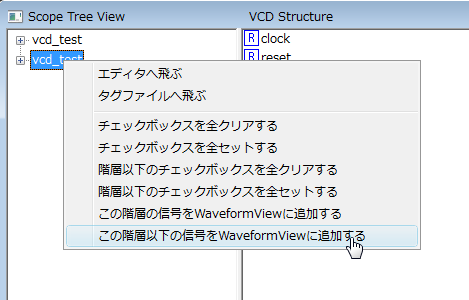

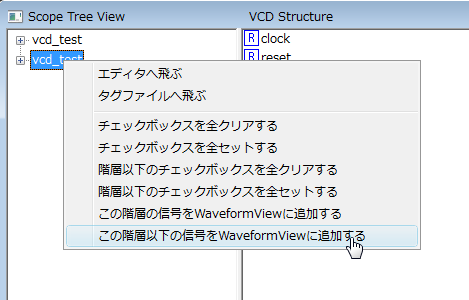

選択すると、タイトルバーにVCD structureと出る方がVCDの読み込んだスコープになります。

通常と同様にWaveformViewerに追加します。

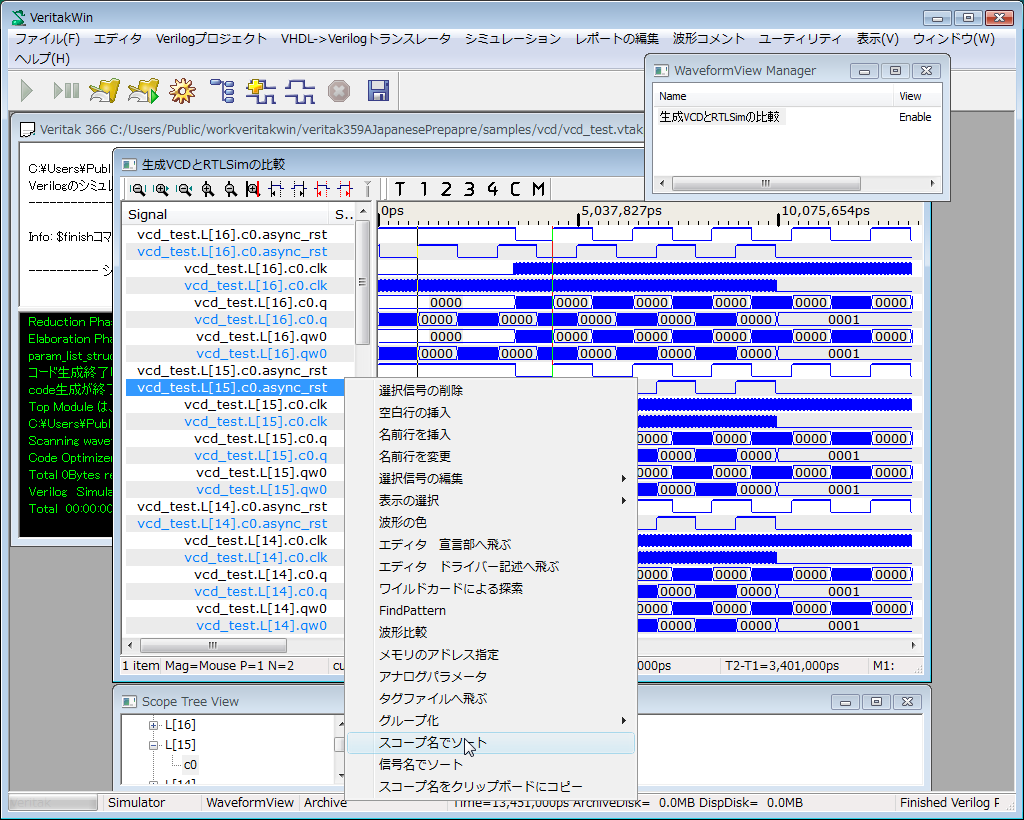

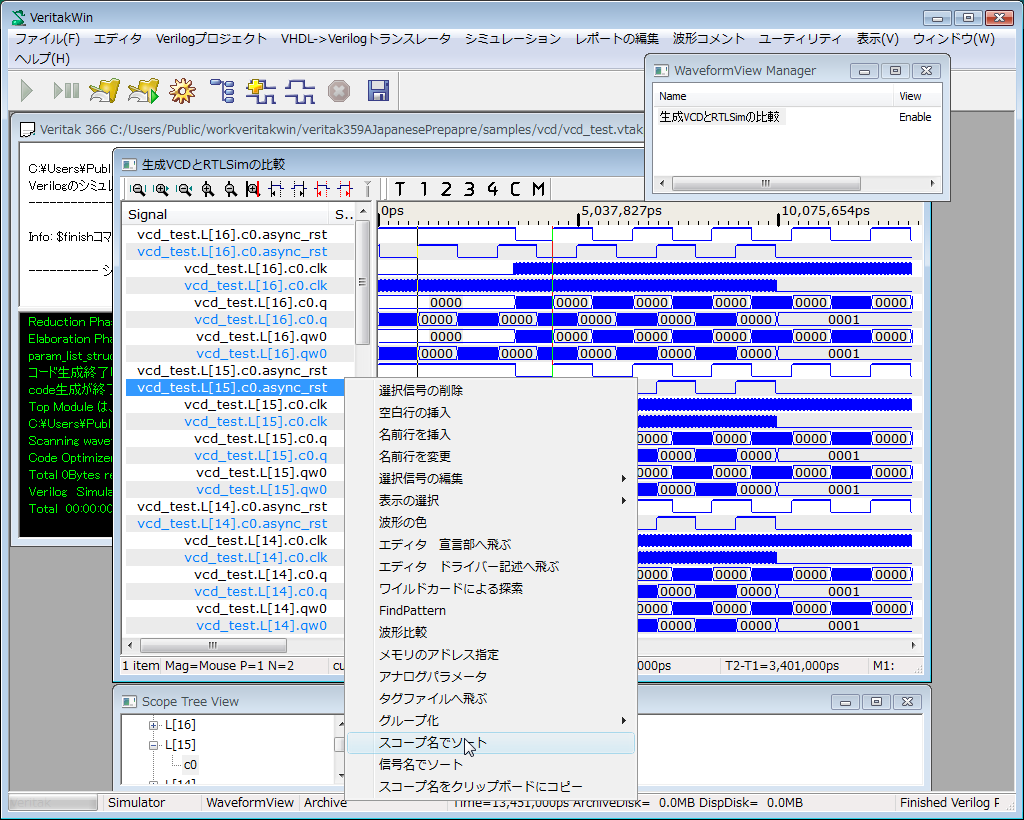

スコープ名でソートすると見易いでしょう。青色がVCD波形です。

TIPS

- ロードボタンでは、VCDは、キャッシュされたままで再読み込みしません。VCDの再読みこみするには、再コンパイルボタン(ギア形状)を押してください。

VCD波形のスタート時刻をシフトする

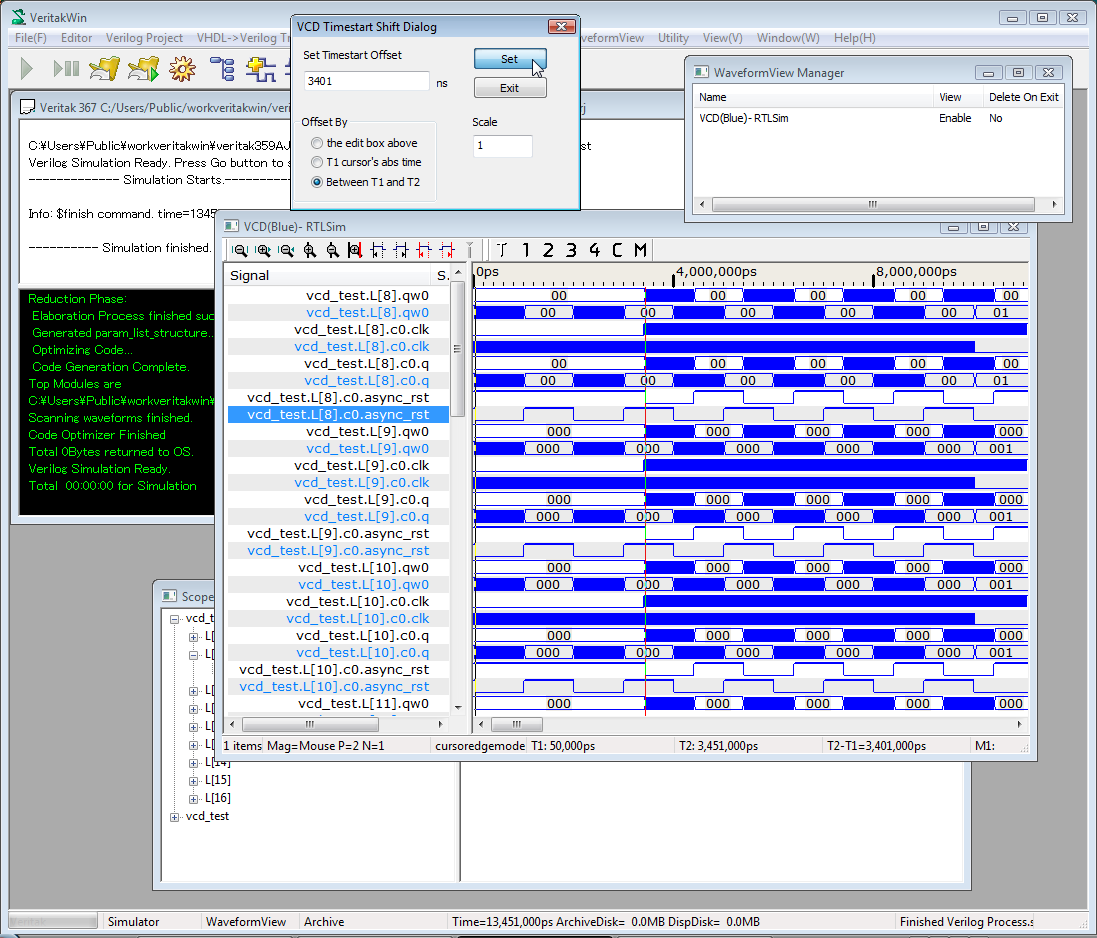

外部で生成したVCDをインポートするとテストベンチ上のRTL SIM波形とは、時間的なズレが生じる場合があります。そのような場合、VCDの波形に一定のシフト値をプラスするオプションです。(マイナスは出来ません)

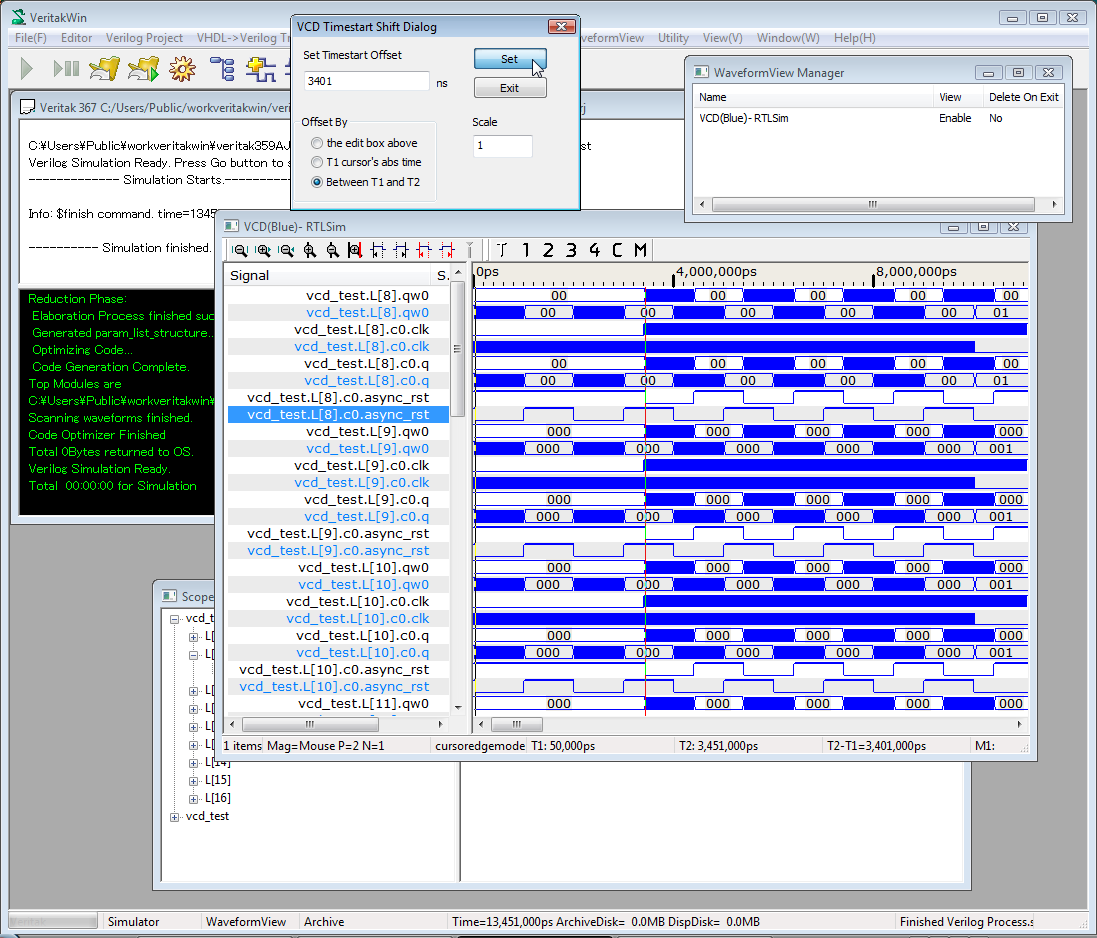

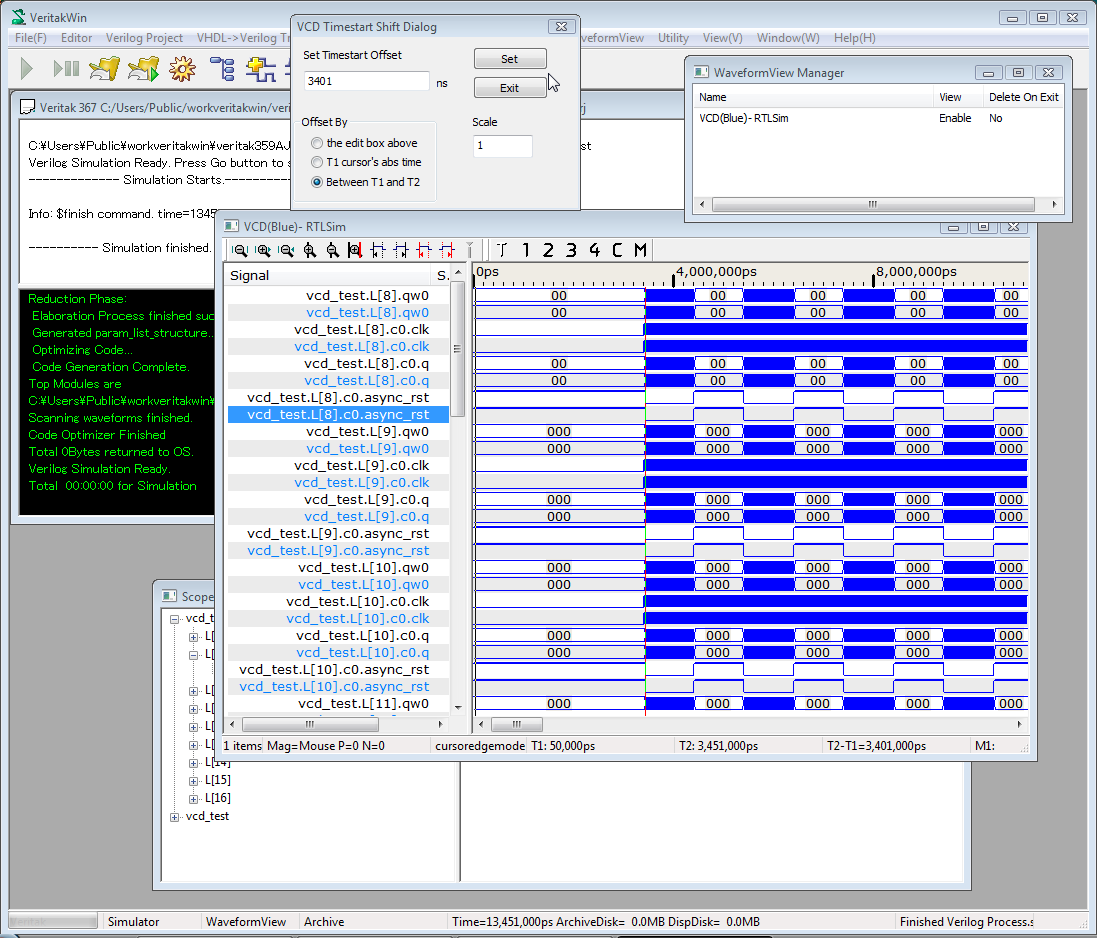

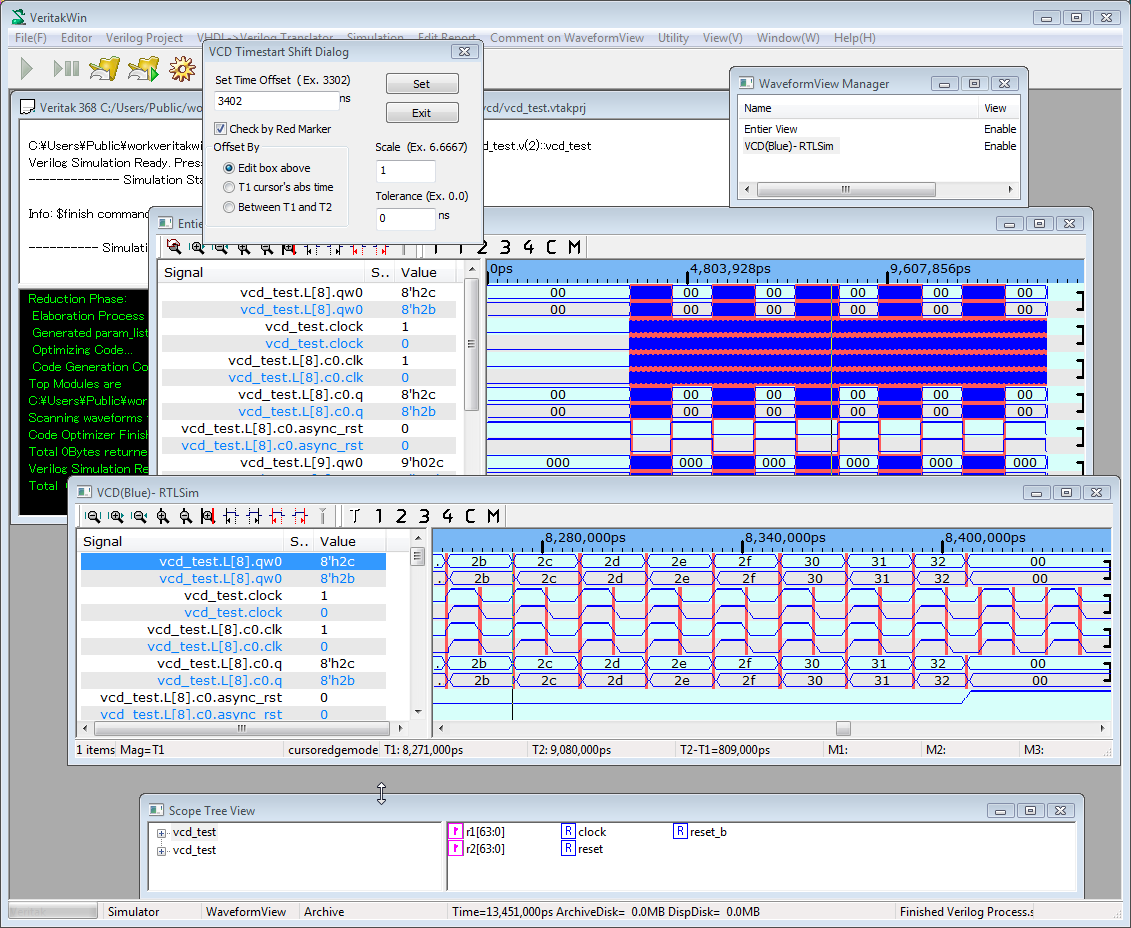

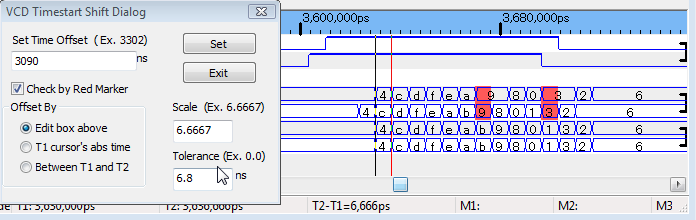

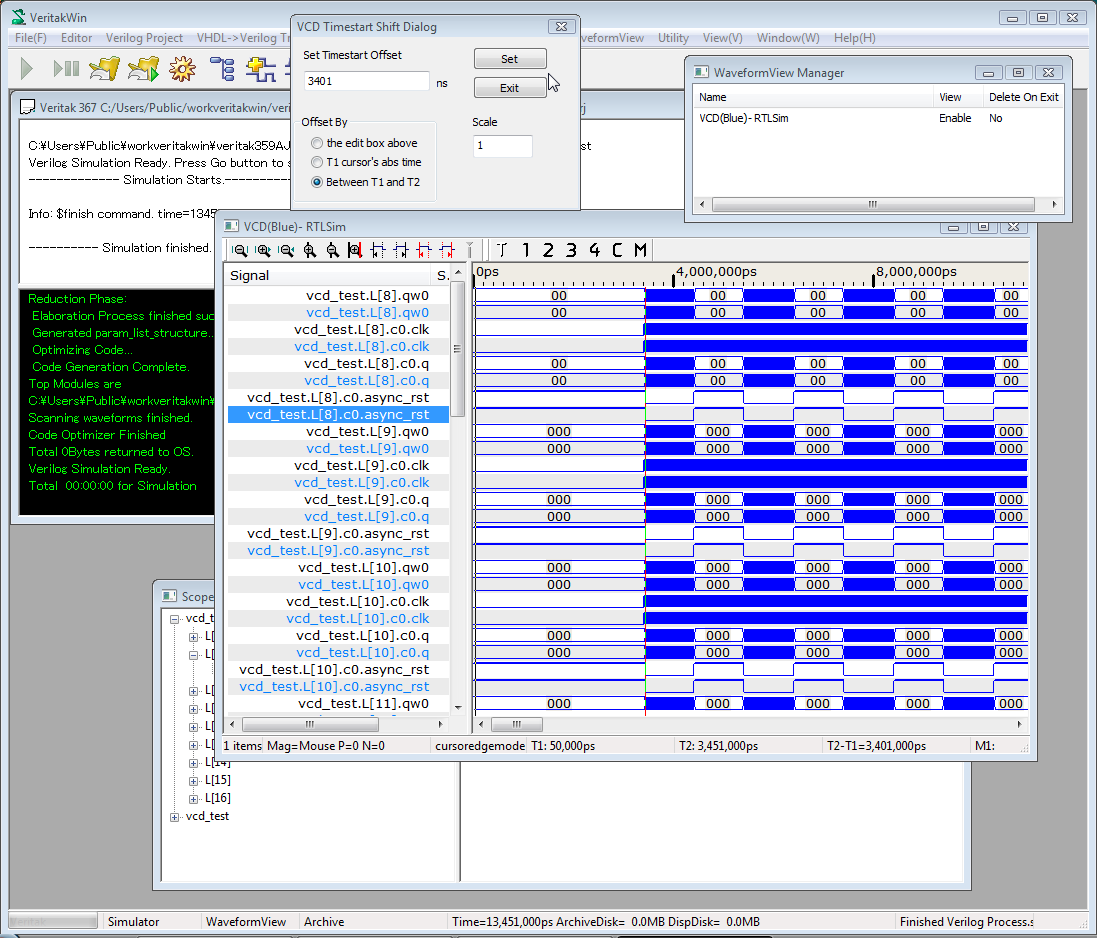

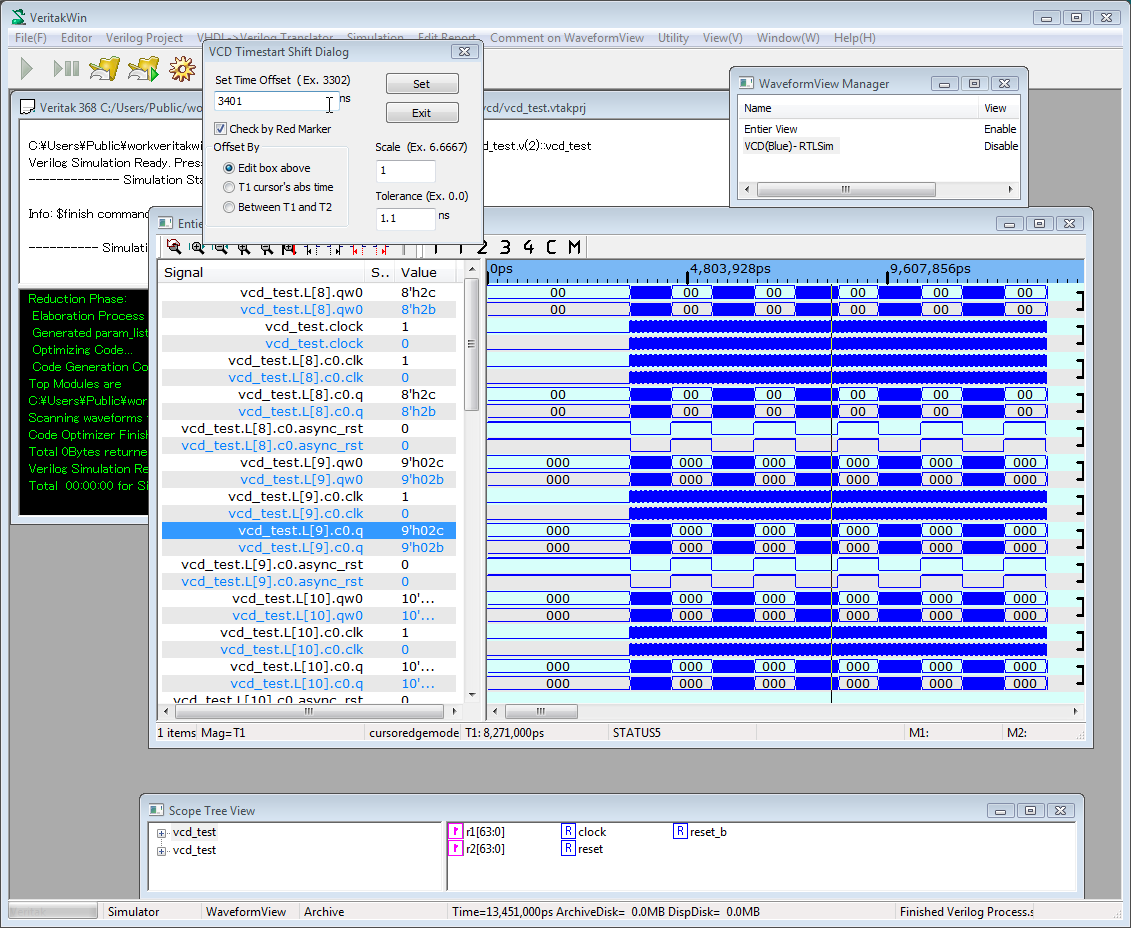

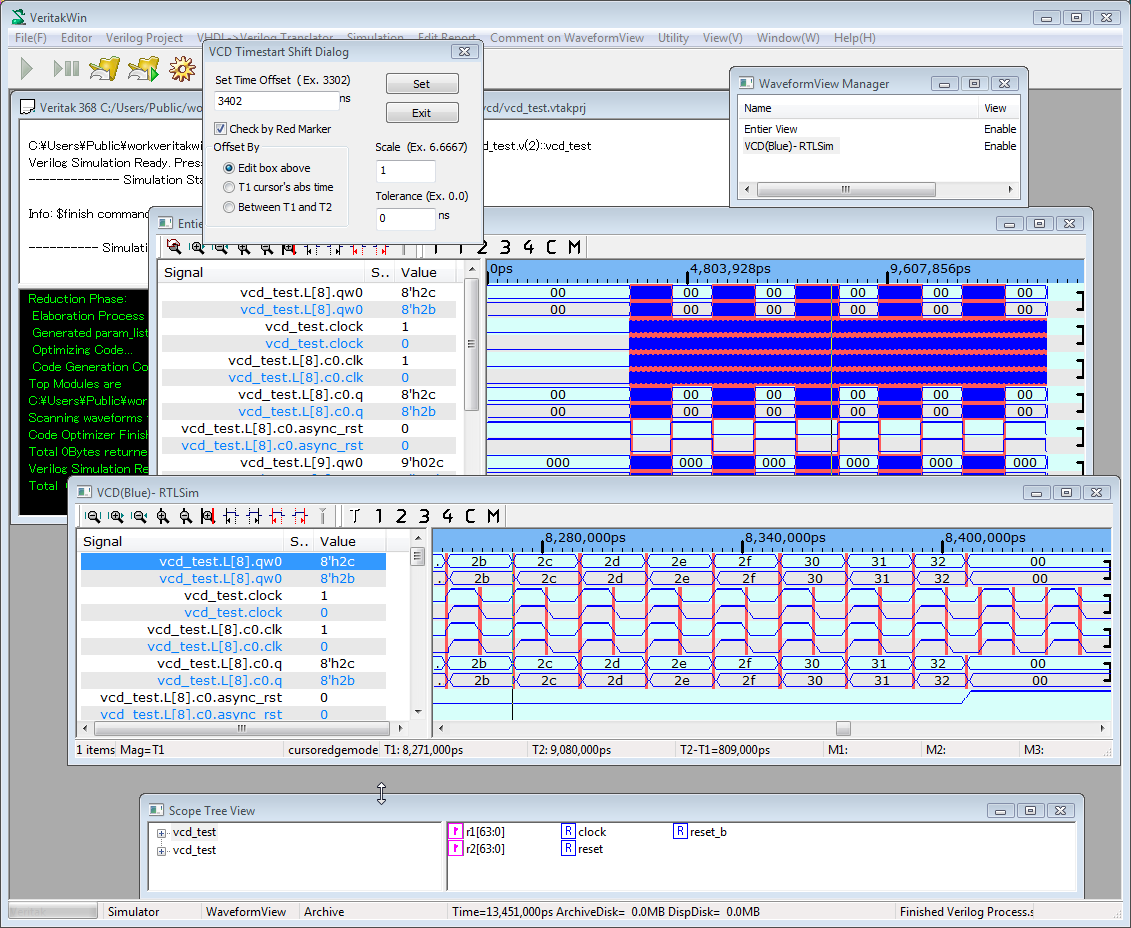

ユーティリティ->VCD波形の表示スタート時刻を変更する を押すと、次のようなダイアログが出ます。 シフト量を指定するには、3つの方法が可能ですが、この例では、T1カーソルーT2カーソルの差をシフト値としています。Setを押すと、差分がシフト値としてVCDに加えられます。

結果、下のように見易くなりました。

TIPS:

- VCDファイルが、ChipScope(TM)のようにサンプリング周波数で正規化されたようなVCDファイルになっている場合、RTL SIMとは、時間スケール倍する必要があります。scaleに入力して合わせこんでください。

- ChipScope(TM)の場合は、ソート->スコープ名でソート(末尾優先)でソートするとよいでしょう。

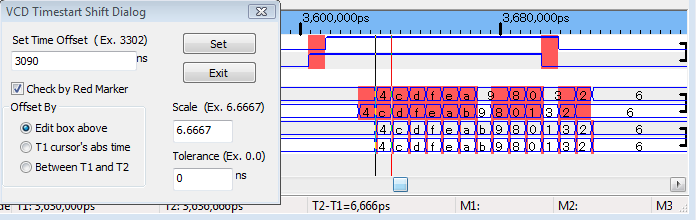

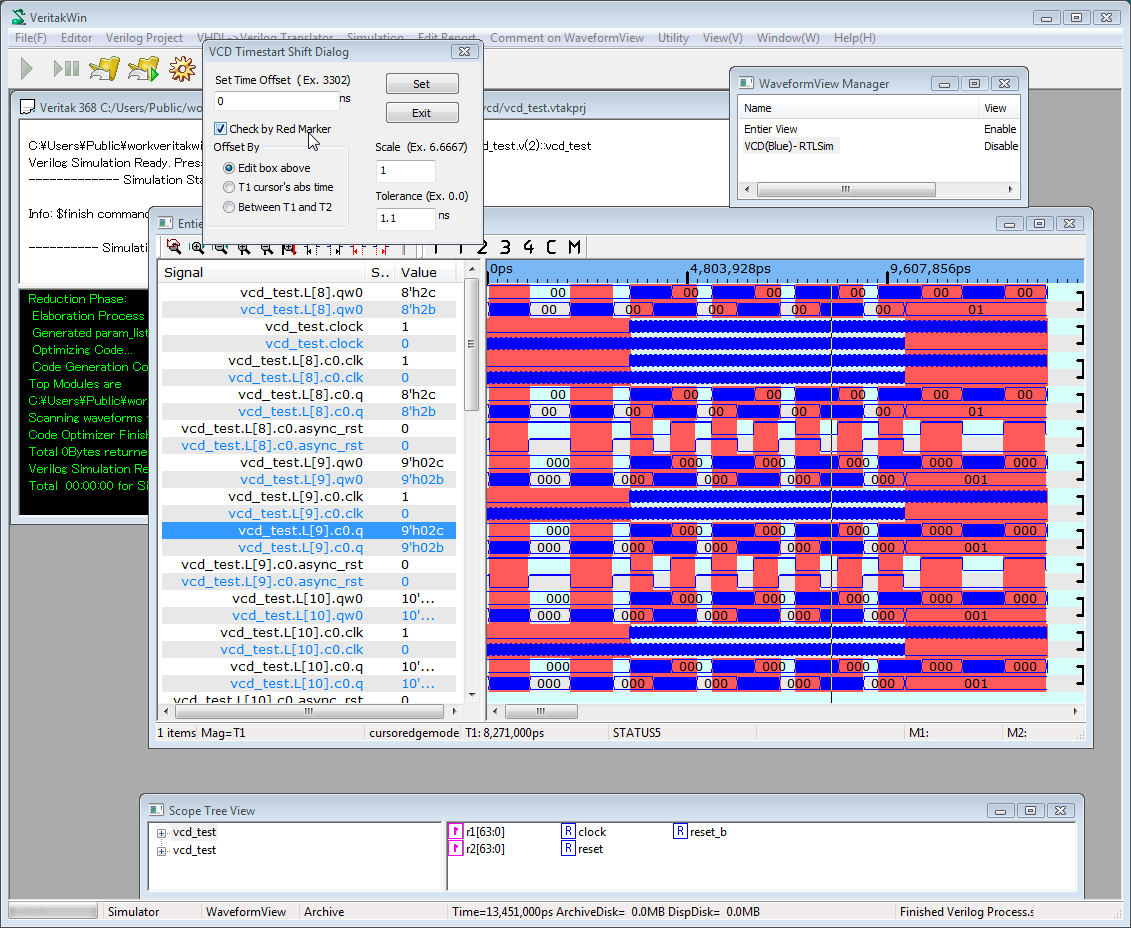

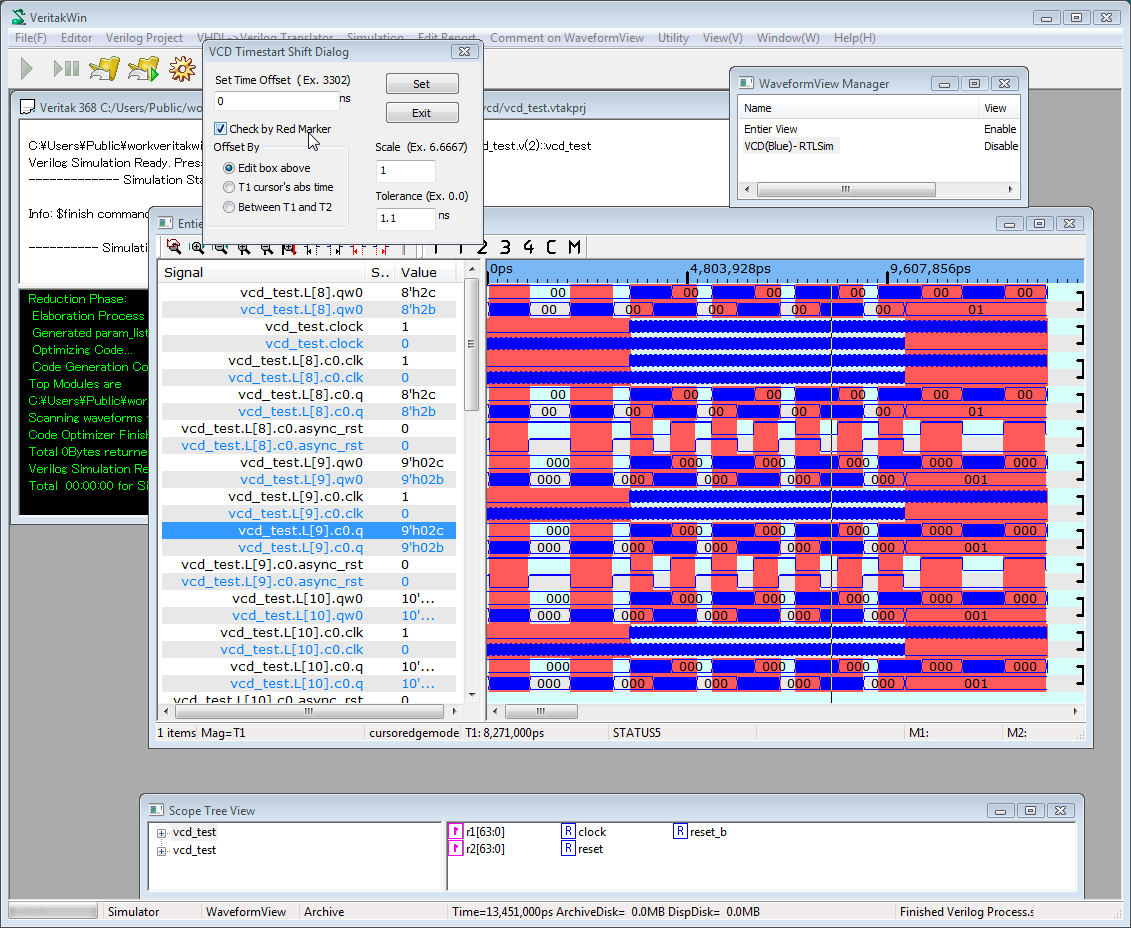

2.4.1.5 波形比較

下の Check by Red Markerを設定することで、 2つの波形のビジュアルに比較できます。違うところは、下図のように赤くなります。本機能は、VCDに限ったものではありません。.二つの連続した行のビット幅が同じときに自動的に行われます。

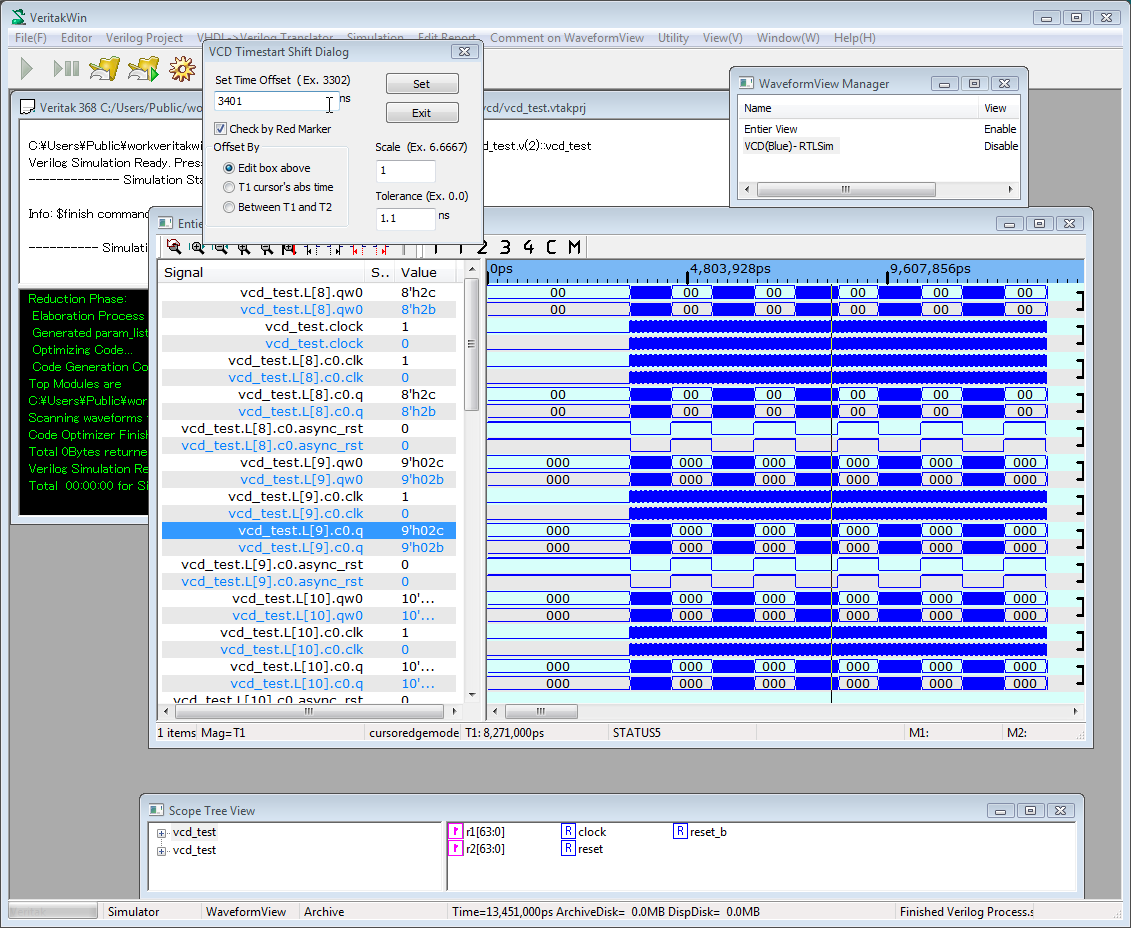

比較した結果相違がなければ、下図のように赤にはなりません。比較を行った箇所には、画面右端に"]"が表示されます。 "]" が表示されないときは、ビット幅が同じでないか、内部制限(浮動小数、ビット展開等)によるものです。

公差

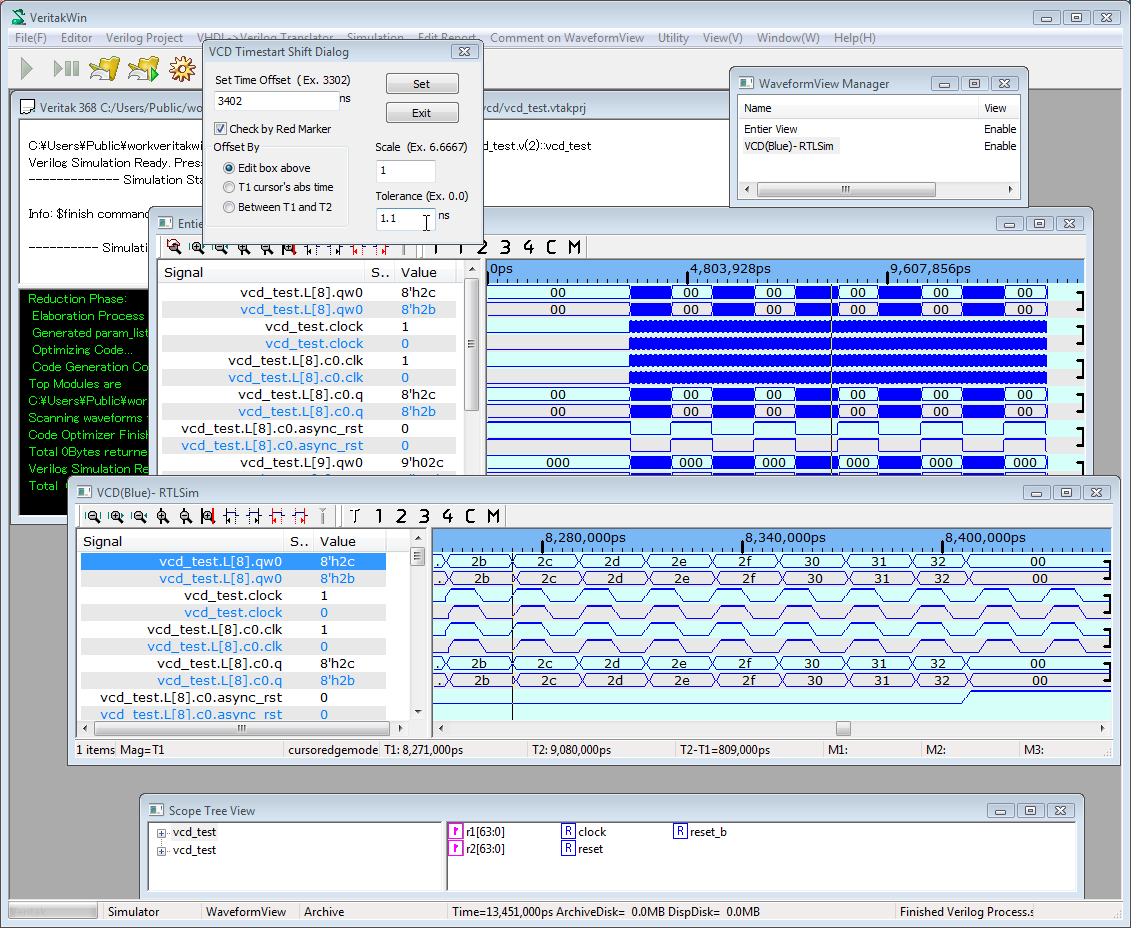

表示アルゴリズムは、1ドット以下のグリッチ的な相違でも見落とさずに表示します。このことは、逆に、煩わしい場合もあるでしょう。次は、そのような場合の例で、意図的にVCD波形を1ns(3401->3402)シフトさせています。

.

.

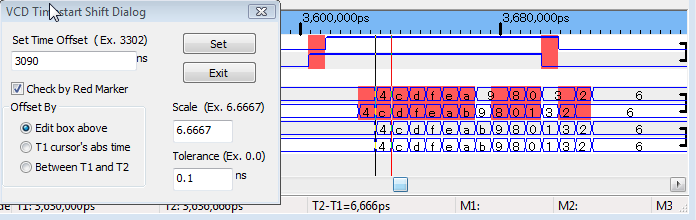

このような場合、公差をそれより大きく設定すれば,(この例では1.1ns)フィルタできます。

公差設定の例

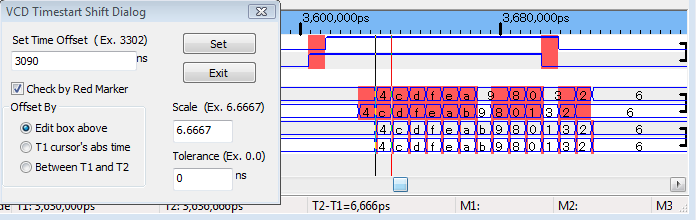

上では、ChipScope(TM) や、ロジアナ波形のVCD等、サンプリングしたVCDに対して、Scale倍して、波形を合わせましたが、この値が、整数でない場合は、意図せず微小な相違が入りこんでしまいます。

このような場合は、微小な相違だけフィルタすればよいので、たとえば、0.1nsを定義します。

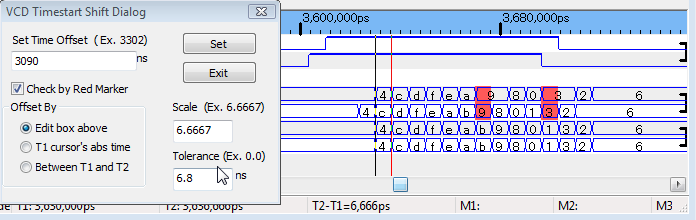

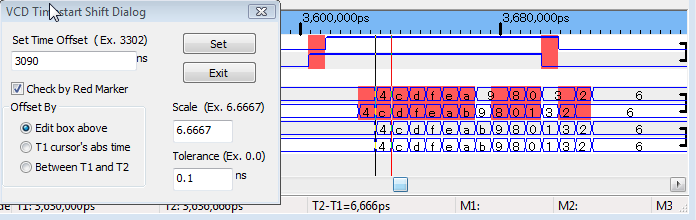

公差を大きくとれば、1CLK以上に大きく取れば、1CLKシフトも無視できるでしょうか?残念ながら、これは、できません。次のように表示されるのは、バグではなく仕様です。

TIPS

- 赤マークの色は、色設定ダイアログの Invalid colorで変えられます。

- 同様に "]" は、 Header Line color で変えられます。

- テキストと被っていて紛らわしいときは、色設定ダイアログの Force_textout_transparent で、プライオリティが変えられます。

.

.