この機能もVeritakユニークです。

Trace mode2 は、Traceモードに基本的には同じですが、タグファイルを生成するところが違います。タグファイルは、HDL全体の構造を記述したファイルです。人のソースはただでさえ理解しがたいものです。「この変数はどこで代入されているのだろう。。」、そんなとき、このツールはいくらか助けになるはずです。

例で見ていきましょう。

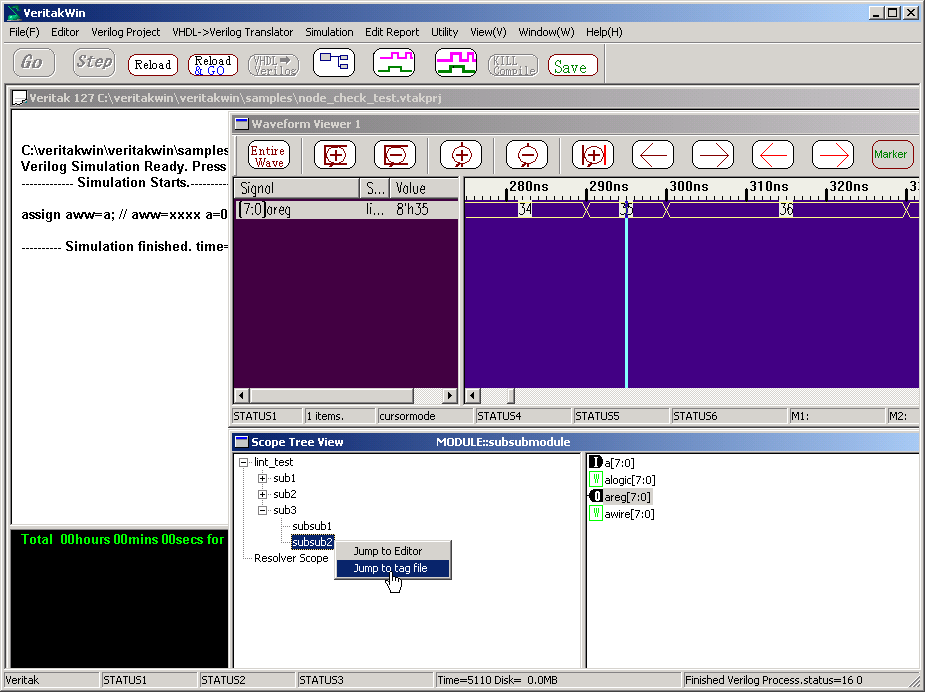

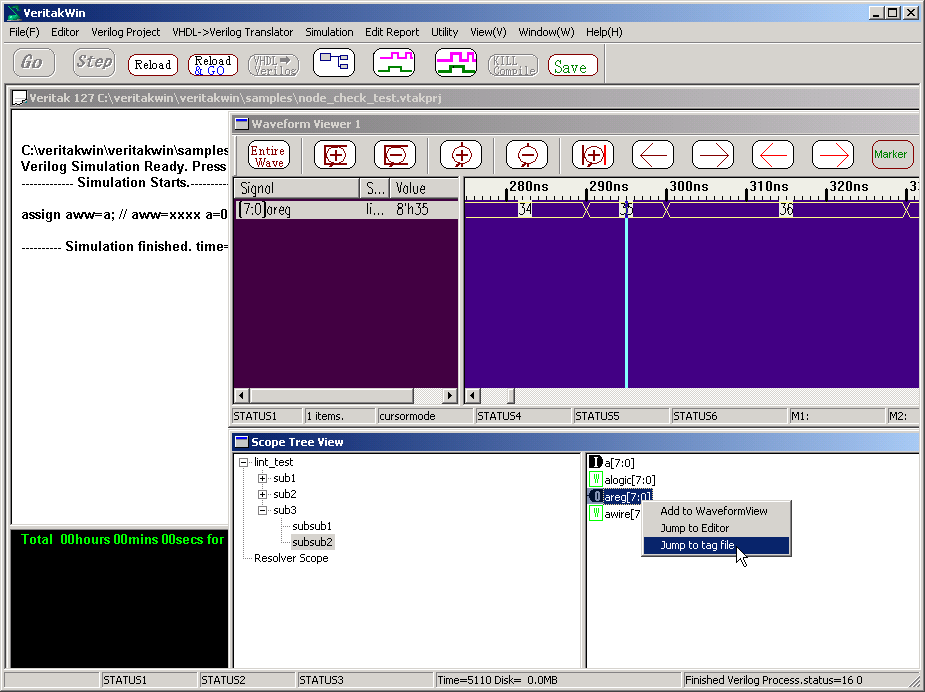

Load Project "node_check_test.vtakprj"

タグファイルへ飛ぶ

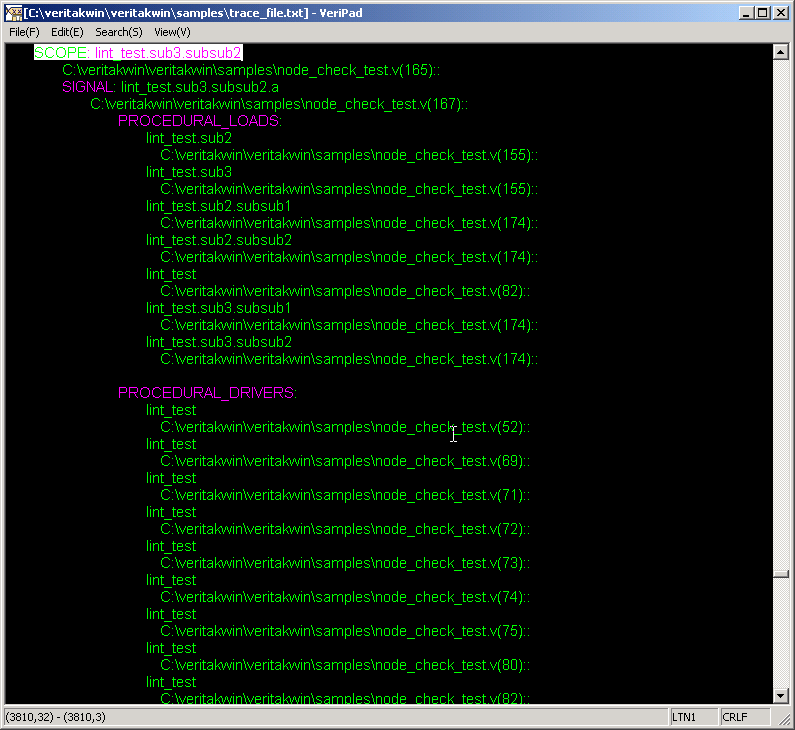

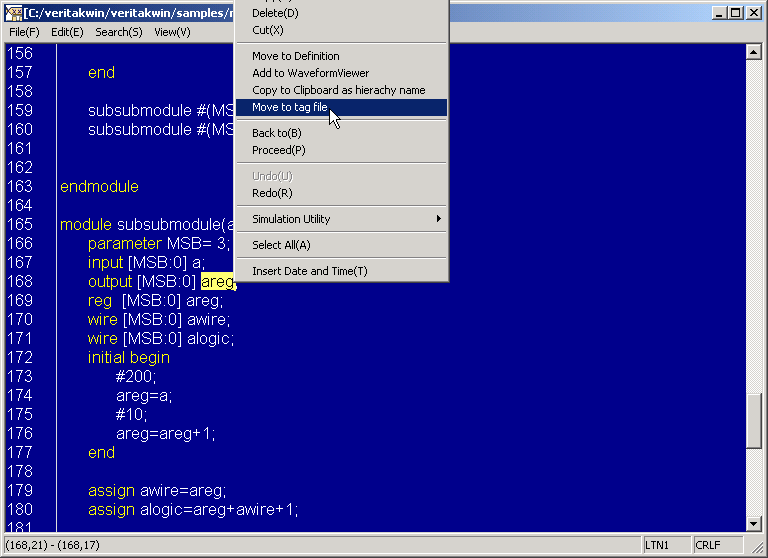

タグファイルへ飛んできました。.

タグファイルへは、LIST ViewまたはWaveformViewからも飛べます。.

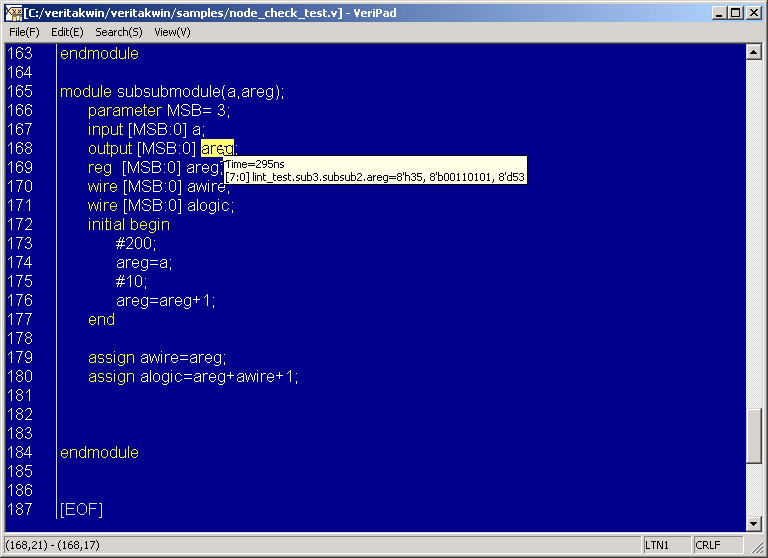

"lint_test.sub3.subsub2.areg" をダブルクリックすると

タグファイルから飛んできました。( line 168.)

タグファイルは、SCOPE情報と組になっているので、一意にツールチップすることができます。Time

295nsは、T1カーソルの値です。

インスタンス化したパラメータも分かります

Veripad からもタグファイルにジャンプできます。

タグファイル中のKeywordの意味

Keywordsとして、,SCOPE,SIGNAL,PROCEDURAL_LOADS,PROCEDURAL_DRIVERS,Aliases,SourceDriver,Drivers_FANOUTS,DECLARED,ASSIGNED

が登録されています。それらの意味は下表の通りです。.

| KEYWORD | Meaning | Example |

| SCOPE | Scope. の後に"SIGNAL:"が続きます。. | |

| SIGNAL | 信号です。memory とlong vectorはサポートしていません。 | |

| PROCEDURAL_LOADS | 手続き構文中のRHSです。. | initial a=b;// if(b);//** a<=b; a<=b[i]; bの PROCEDURAL_LOADS は上全部です。. |

| PROCEDURAL_DRIVERS | 手続き構文中のLHSです。 | aの PROCEDURAL_DRIVER は** を除く上全部です。. |

| Aliases | 別名です。 | たとえば、 sub dut(.clock(CLOCK),.. clock and CLOCK です。 |

| SourceDriver | ドライバの宣言箇所です。 | reg a;//ここ wire c;//ここ assign c=a ^ b;// cここ |

| Drivers_FANOUTS | NET構造のRHSです。 | a とbについて assign c=a ^ b |

| DECLARED | 宣言箇所 | cについて、 wire c; |

| ASSIGNED | アサインされている箇所です。 | cについて, assign c=a ^ b; |

| ResolverInputs | Resolver's inputs |