A/B/C/D 行列は、ファイルとして与えます。 4次のrungekuttaで計算しています。呼び出し手順は、

| $runge_kutta("File Name",mode,Input_RealArray,Output_RealArray,[X]); |

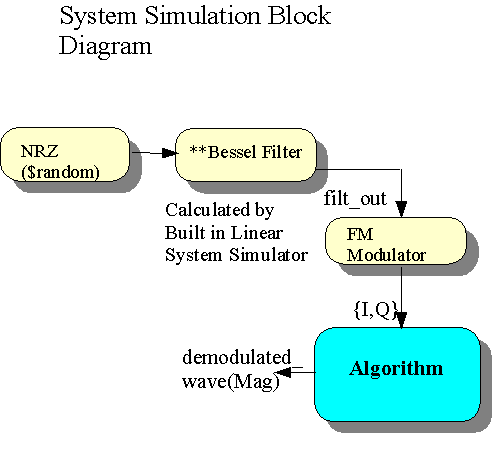

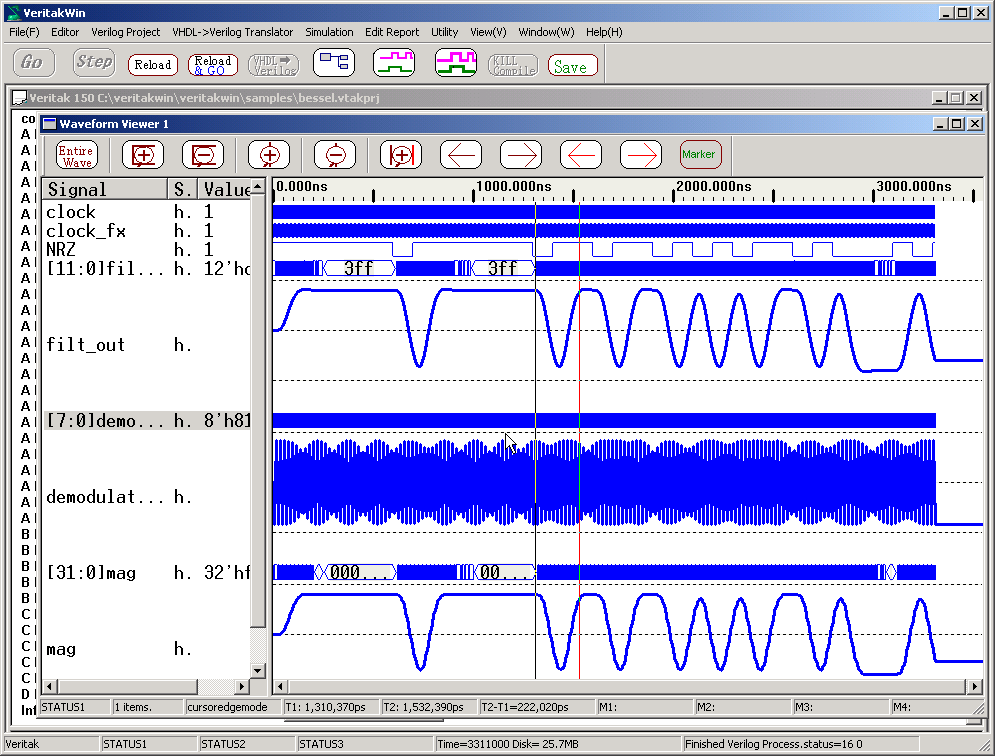

例として "bessel.vtakprj" をご参照ください。NRZからベッセルフィルタを通した波形が得られています。.

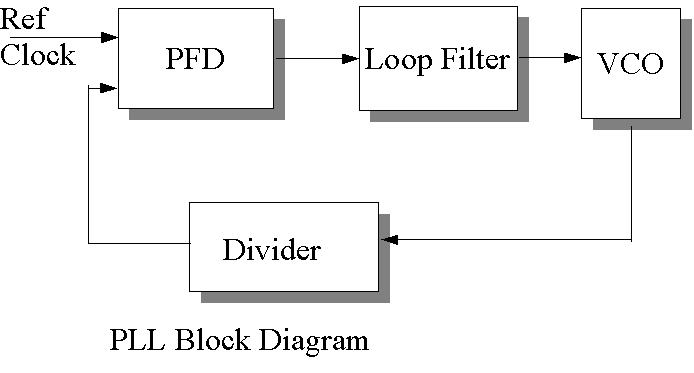

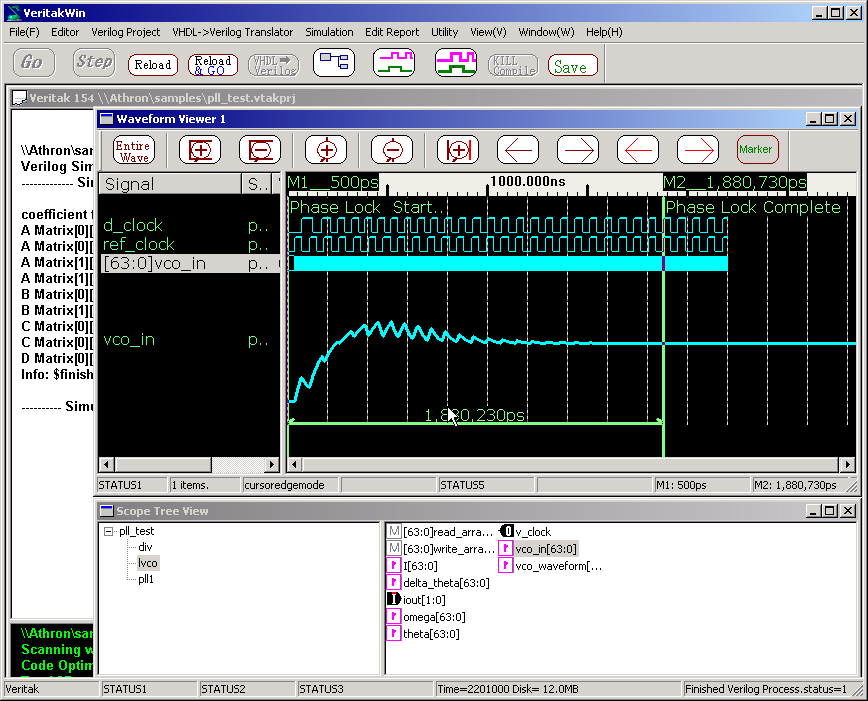

Analog PLLのシミュレーション

Analog PLLにおいては、下図のループフィルタが安定の鍵になります。

この伝達関数は、下式によります。

Veritakのアナログシミュレータは伝達関数を状態空間表現にする必要があります。手計算でもできますが、MatlabやScilabのtf2ss コマンドで簡単に変換できます。たとえば、次のようなスクリプトを書いて変換します。

これで、Veritakの行列読み込みファイル"loop_filter.txt"ができました。"pll_test.vtakprj"

をLoadしてみます。

PLLがロックする様子が分かります。

| C2=14e-12 C1=100e-12 R1=4.7e3 R1C1=R1*C1; C1_C2=C1+C2; C1C2R1=C1*C2*R1; b=[R1C1 1]; a=[C1C2R1 C1_C2 0]; [A,B,C,D] = tf2ss(b,a) freqs(b,a) save 'F:\samples\loop_filter.txt' A B C D -ascii -double |

TIPS

古典制御理論によるPLLの設計例が、下記にあります。

http://www.sugawara-systems.com/opencores/pll/pll.htm