RTL プロジェクト

"RTL_counter.vtakprj" (/samples/altera/counter/)

を開いてみてください。

RTL プロジェクト

"RTL_counter.vtakprj" (/samples/altera/counter/)

を開いてみてください。

RTL ソースは、8ビットカウンタです。

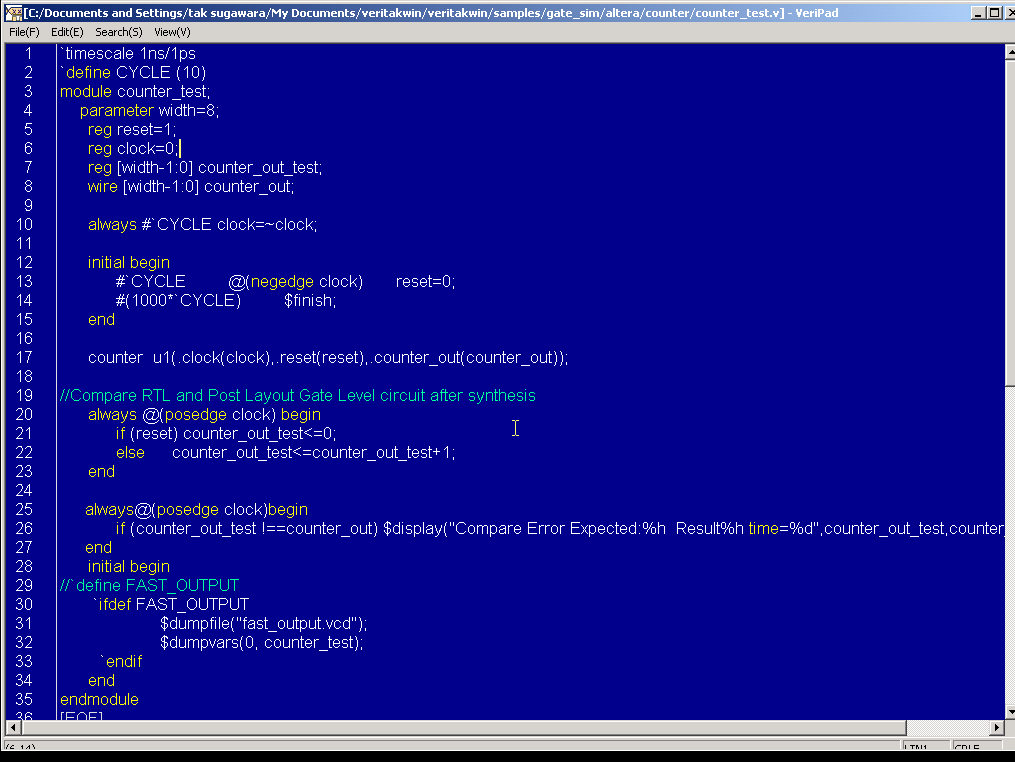

テストベンチは、以下です。

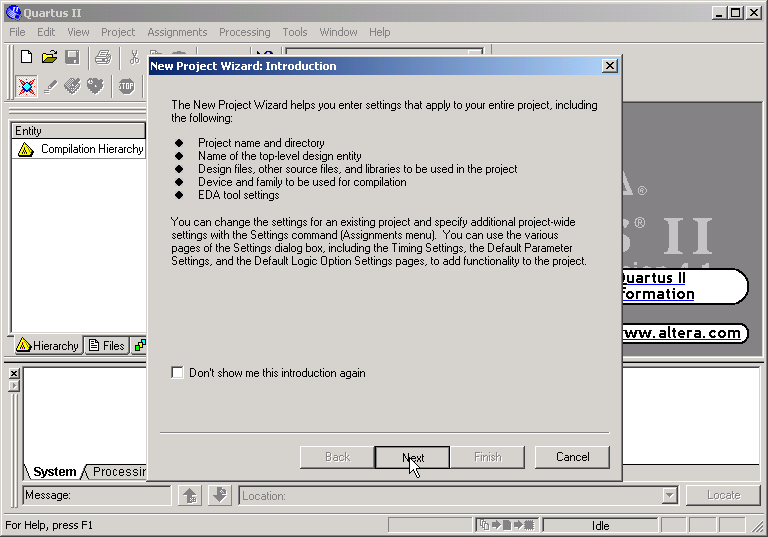

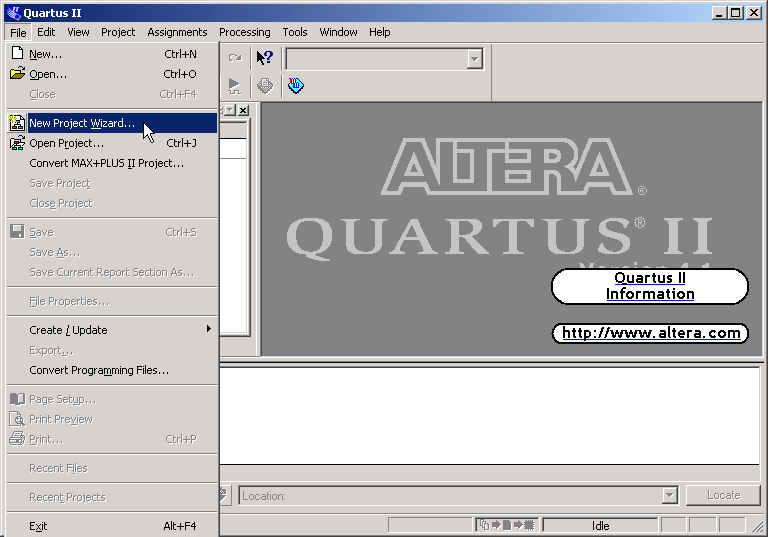

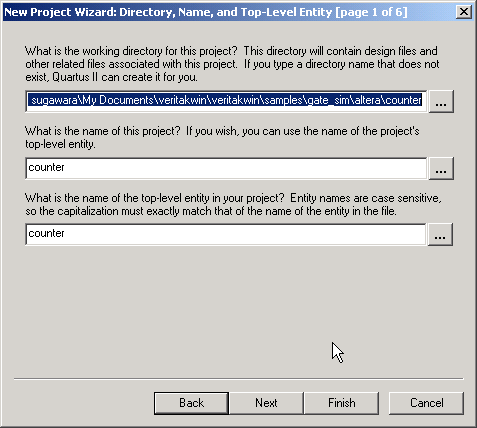

Quartus の設定

New Project with Quartusで作成します。

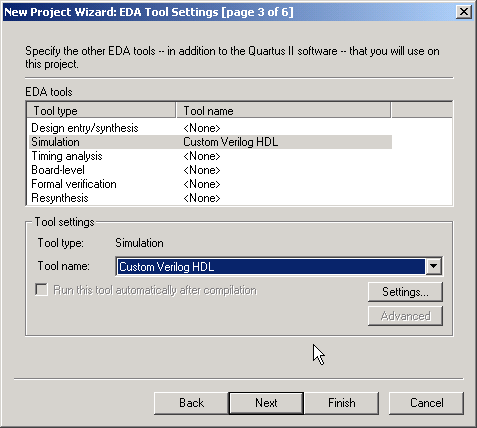

Simulation は、カスタムVerilogを選択します。

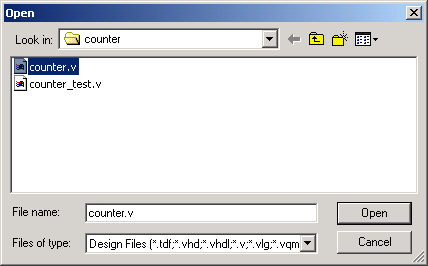

合成対象の "counter.v" を選択します。

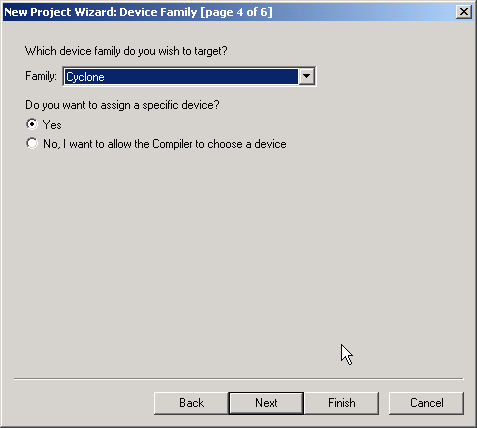

デバイスの選択は自由です。.(Cyclone,Stratix, Stratix2,Cyclone2)

最終的に次のようになります。.

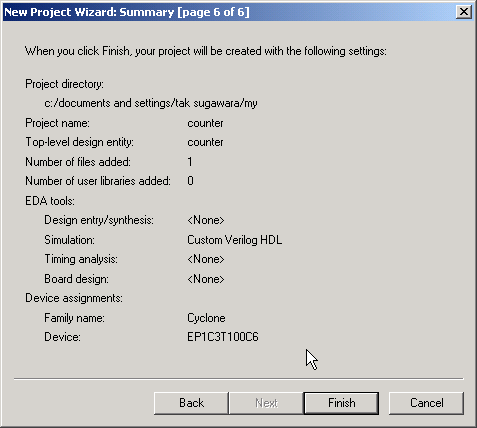

設定が終わったので、合成です。

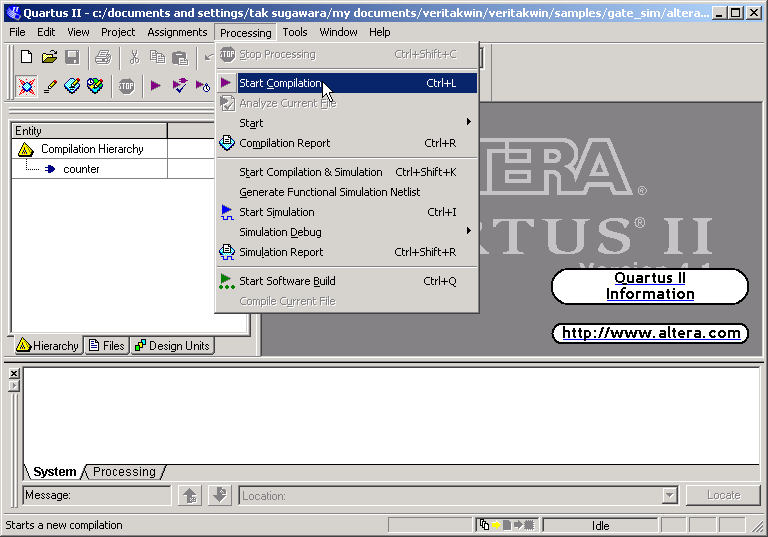

コンパイル完了後、次のようなファイルが生成されているはずです。

*.vo は、ゲートシミュレーション用のファイルです。

*.sdo は、遅延時間のファイルで、" $sdf_annotate(... )" で*.vo

ファイルが読み込みます。

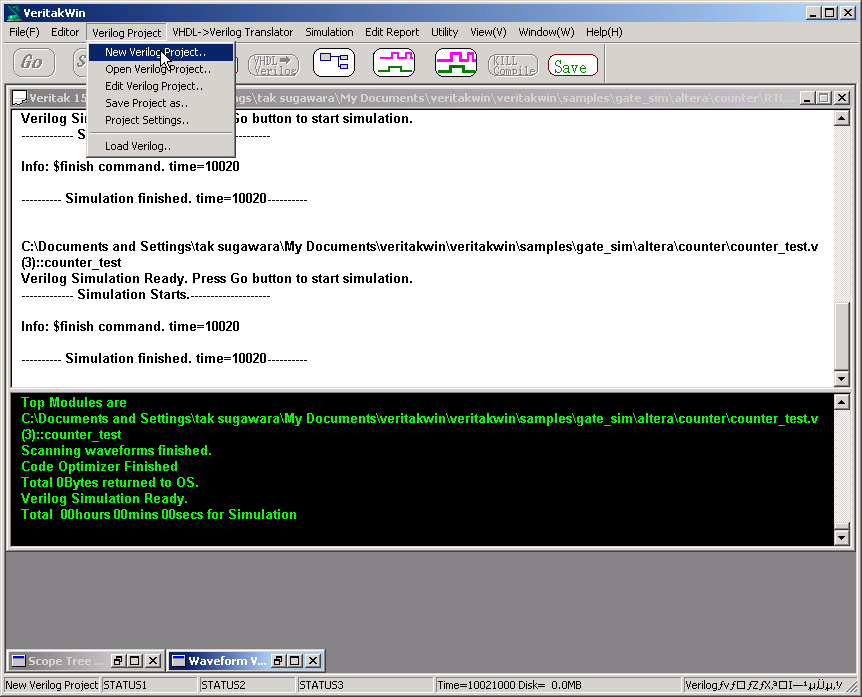

合成が完了したので、ゲートシミュレーション用のプロジェクトを作成します。

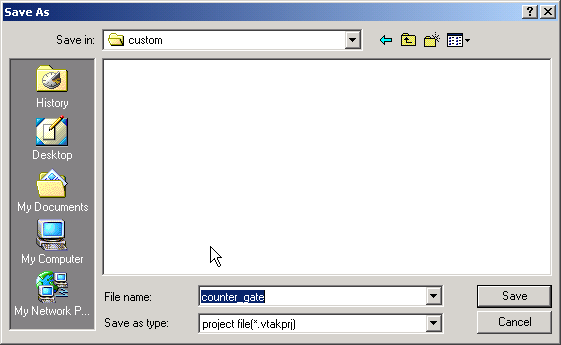

ゲートシミュレーションプロジェクトは、SDFを読み込む関係で、*.vo ファイルの位置に作ります。.

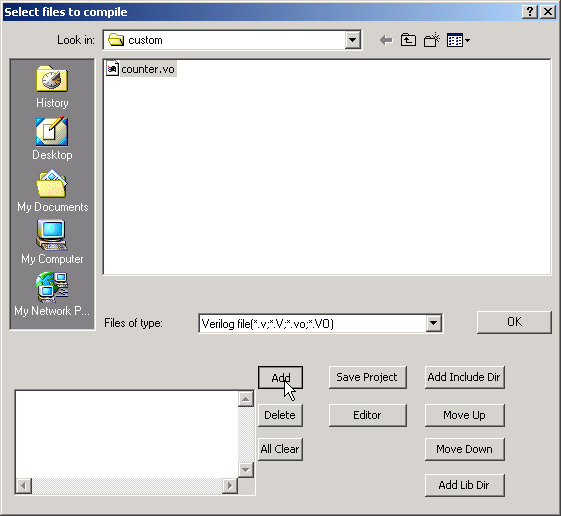

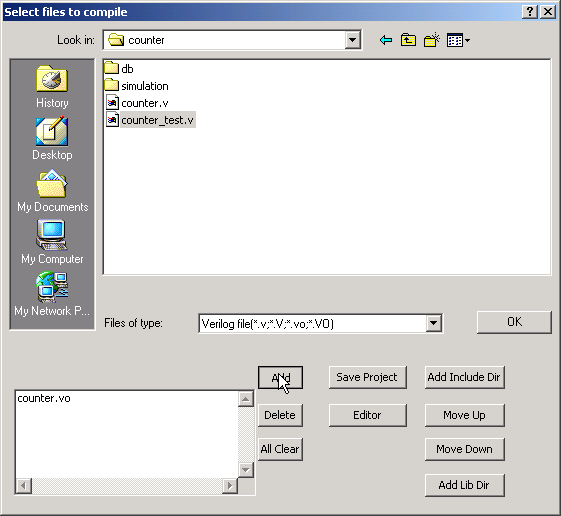

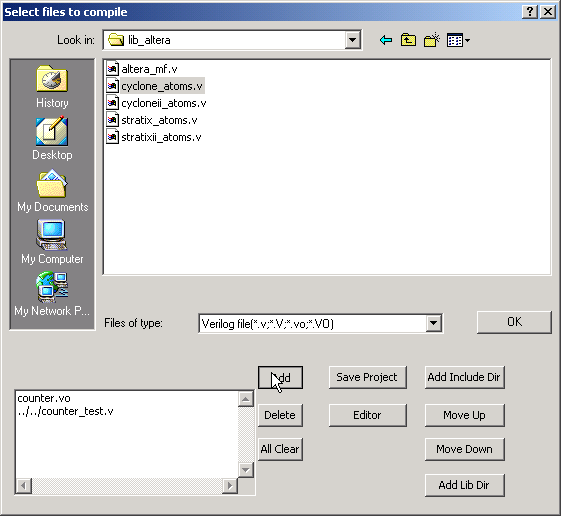

合成したファイルをAddします。.

テストベンチをaddします。

プリミティブライブラリファイルをAddします。(ここでは、Cycloneです。.)

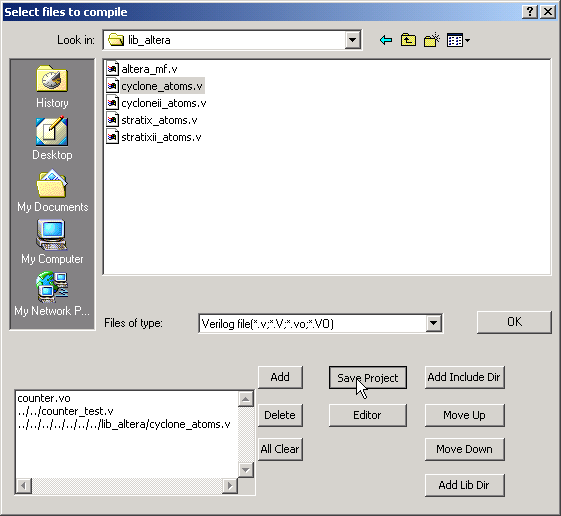

最終的にプロジェクトは、次のようになります。Save Projectするのを忘れないでください。

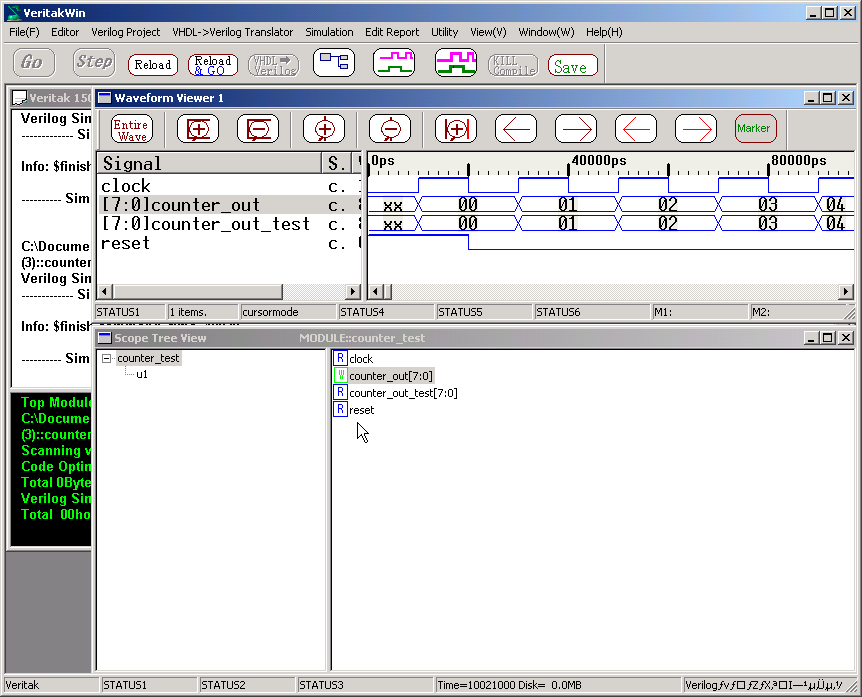

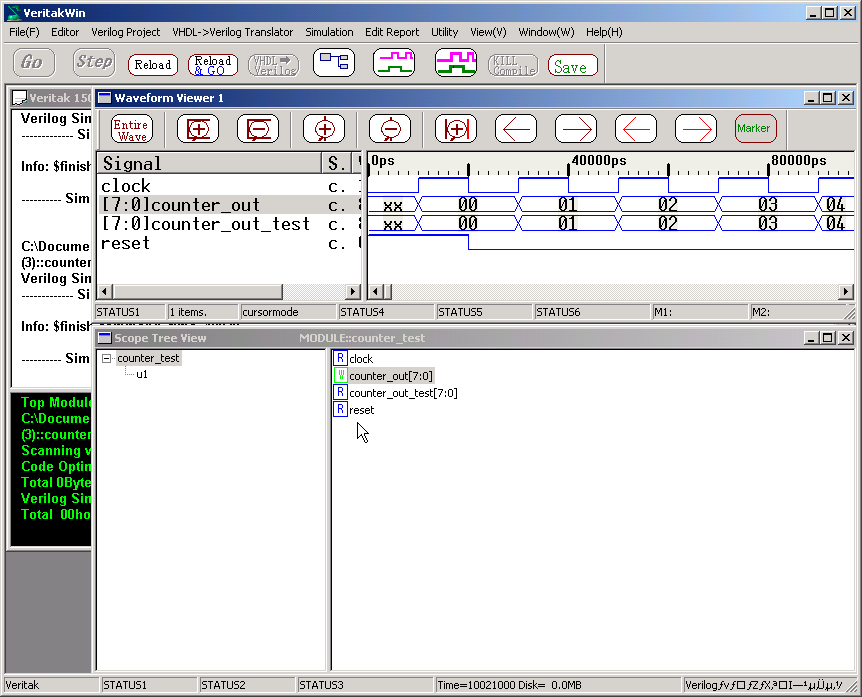

ゲートシミュレーション

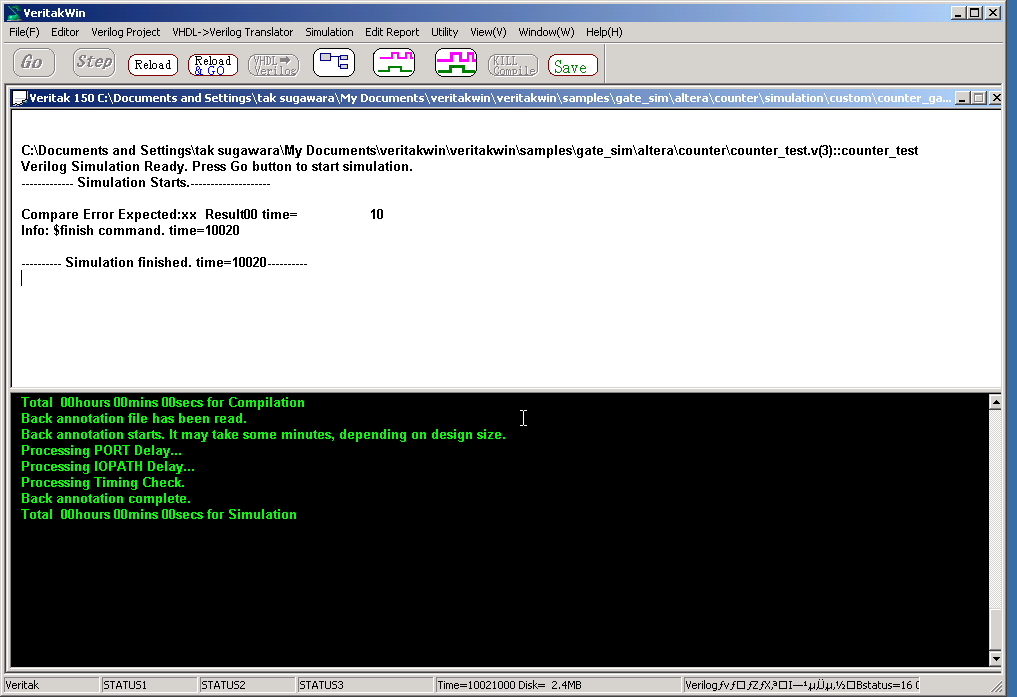

Load Verilog Project "couter_gateprj", Go.

次のようなエラーが出ます。Power On時にFFは、0に初期化されるということでしょう。.

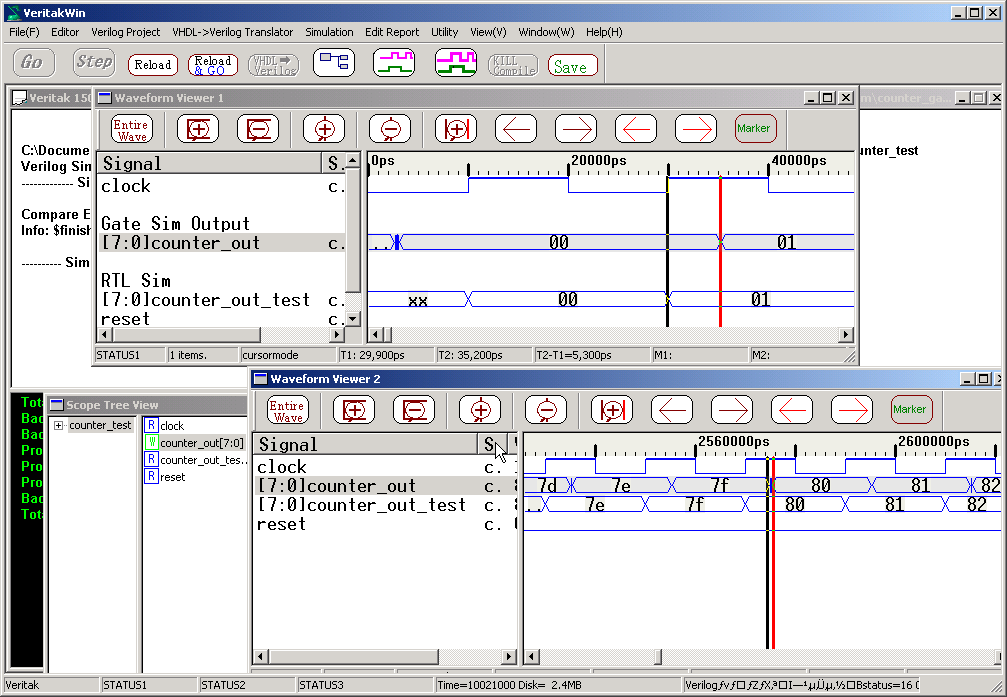

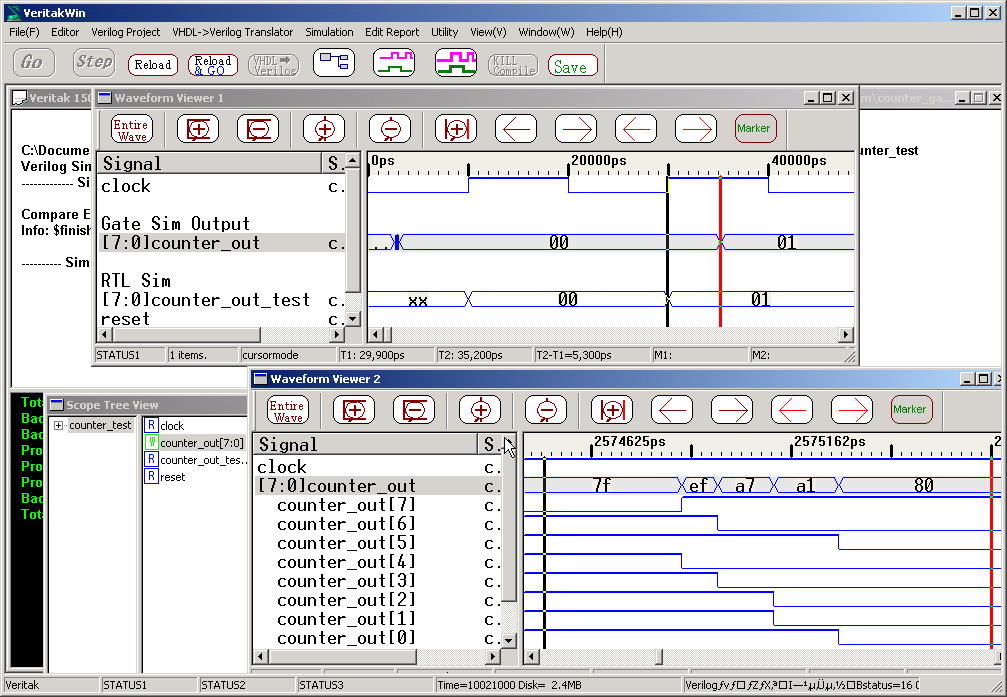

ゲートシミュレーションでは、遅延している様子がわかります。下図の場合、RTLでは、0nsだった遅延が5.3nsになっているということです。ただし、この遅延は、パターンによって変わることに注意してください。

ビットごとに見ると遅延がビットで違う様子が分かります。

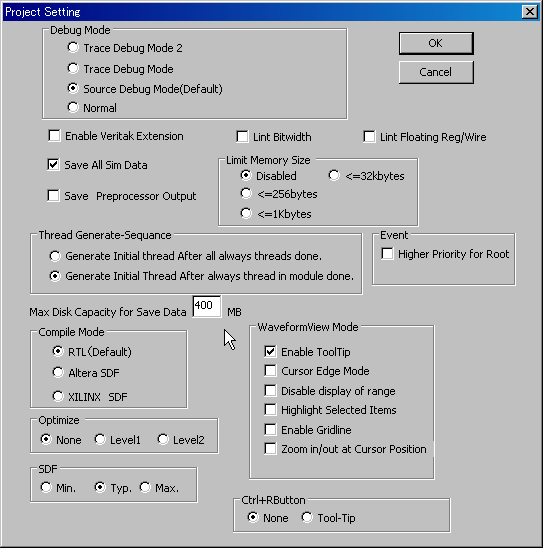

SDF ファイルでは、遅延値がMIN/TYP/MAXの3種類あります。XILINXとAlteraに関しては、今のところ、全て同じ値なので、どれを選んでも同じですが、プロジェクト設定ー>SDFで、TYP を選択しておきましょう。。