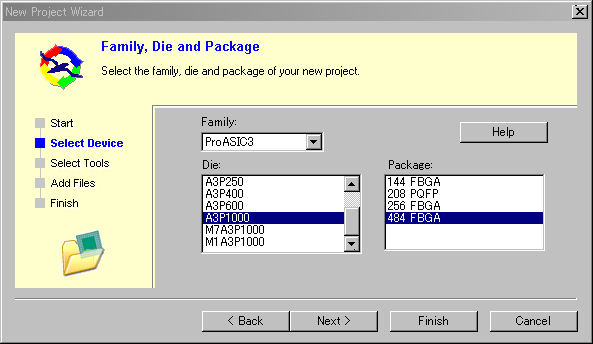

例としてProASIC3を選択しています。

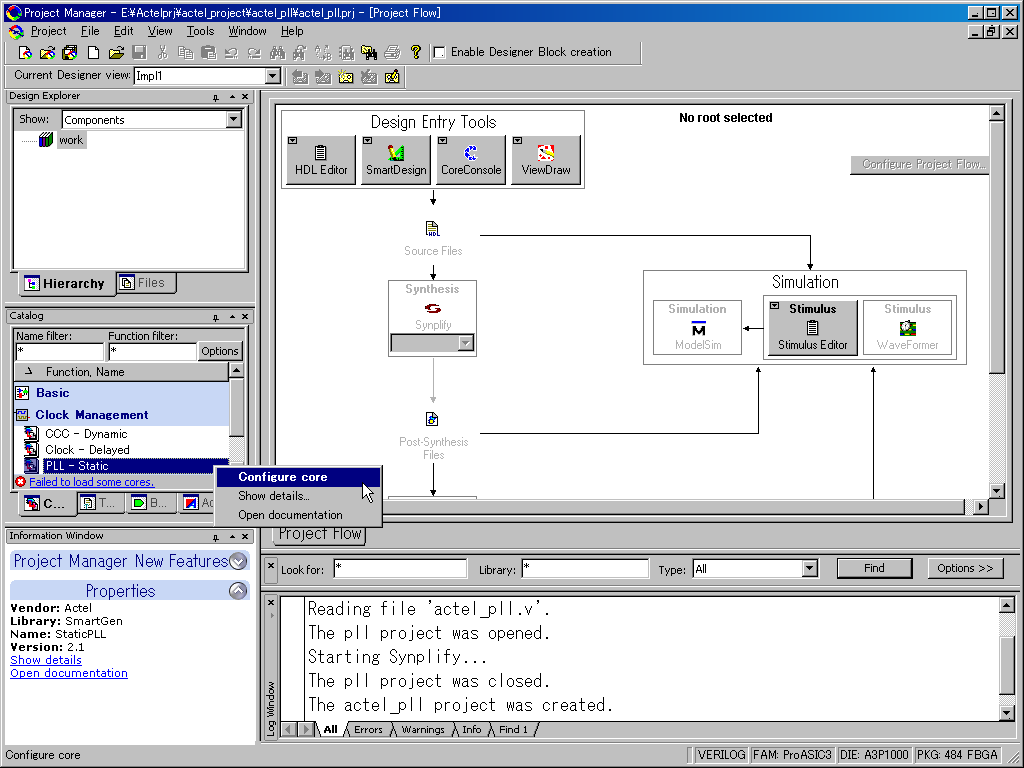

PLL coreを作成します。

5.3.Actel

5.3.1 Actel PLL

5.3.1.1 Actel Project

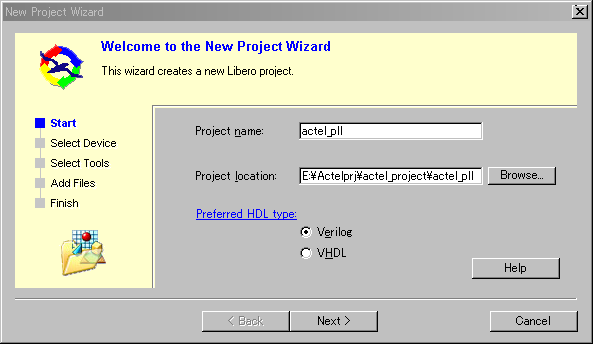

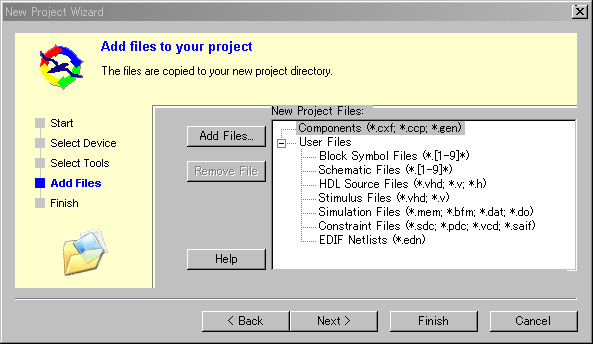

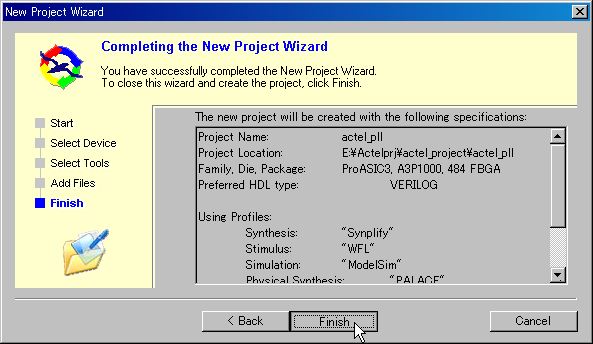

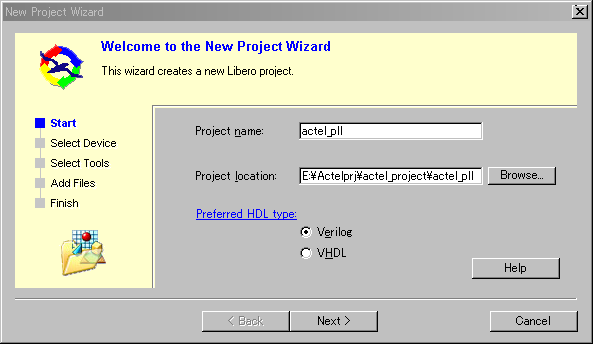

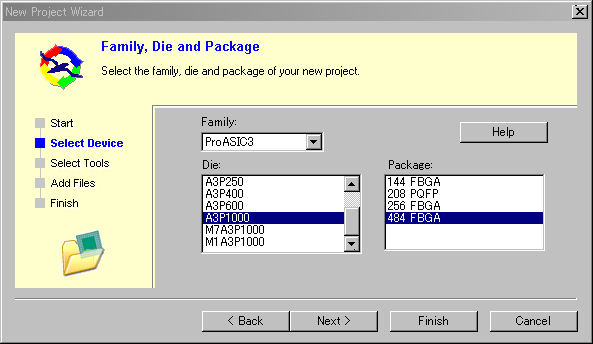

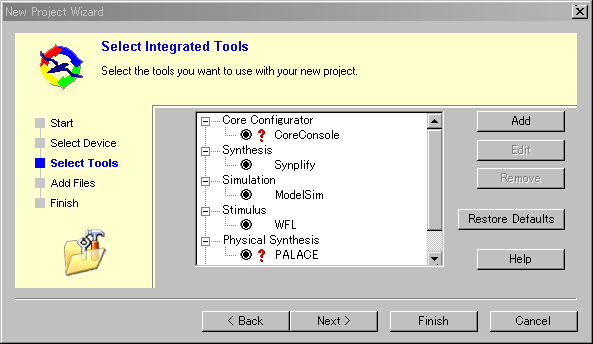

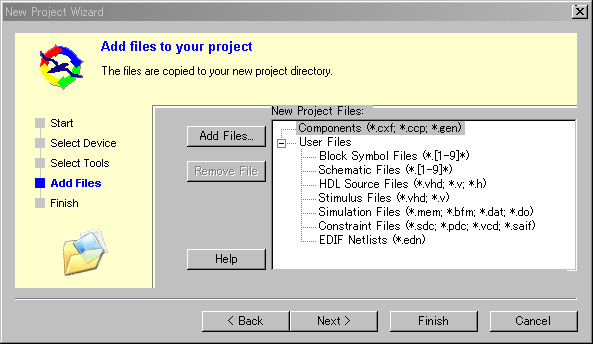

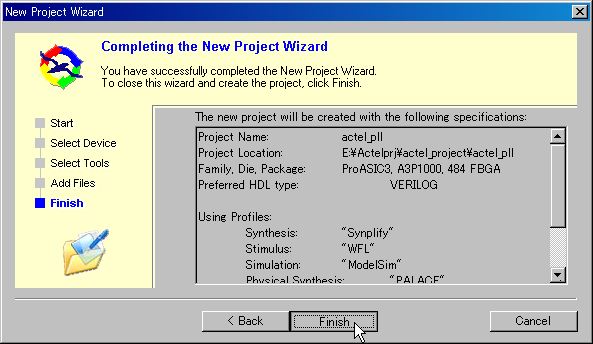

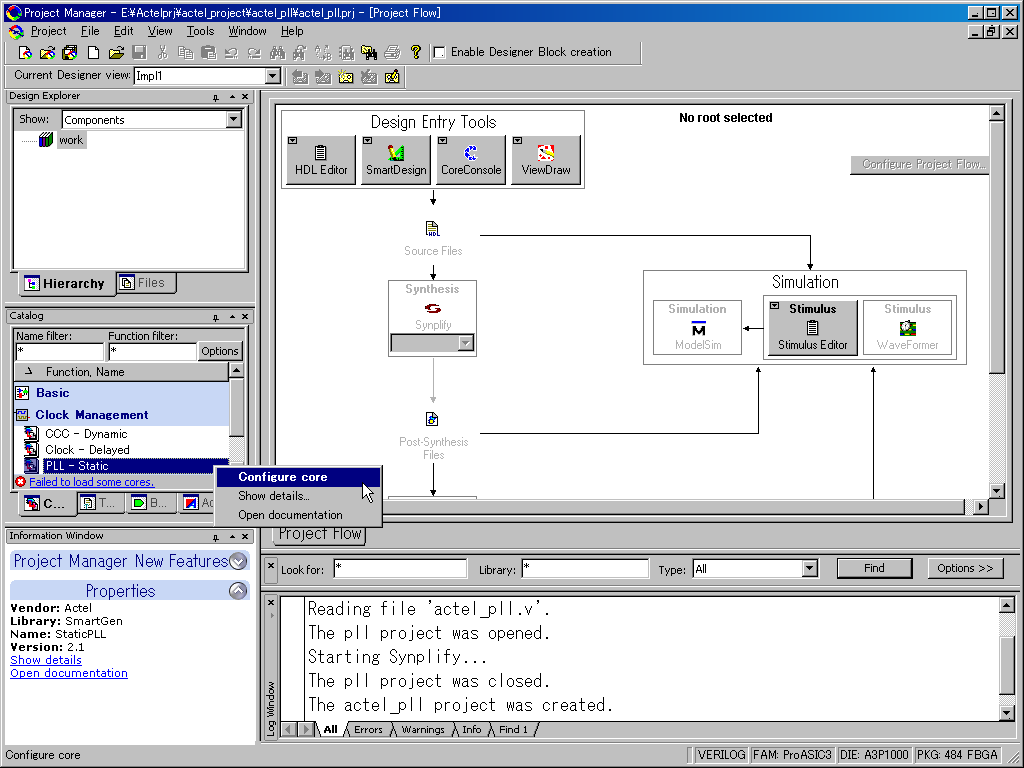

Actelでのプロジェクトを作成します。

例としてProASIC3を選択しています。

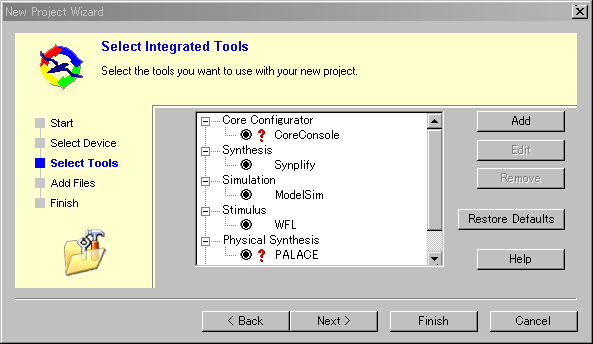

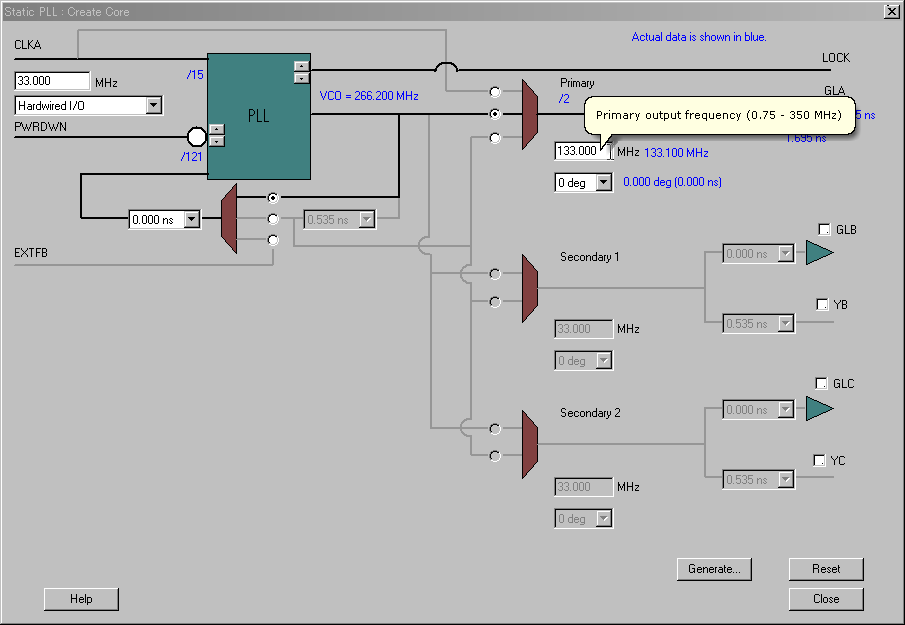

PLL coreを作成します。

出力を133MHzにしてみましょう。

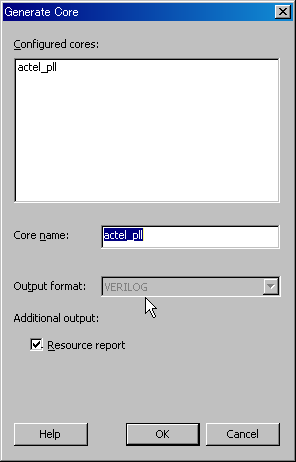

actel_pllと名前をつけました。. (actel_pll.vになります)

5.3.1.2 Veritak プロジェクト

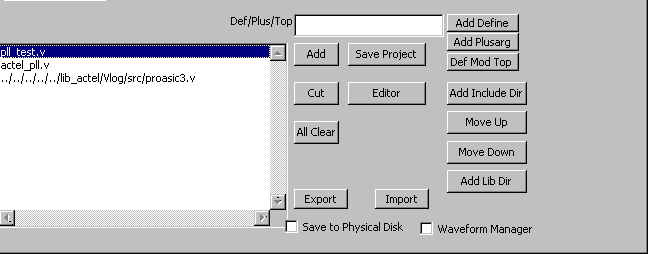

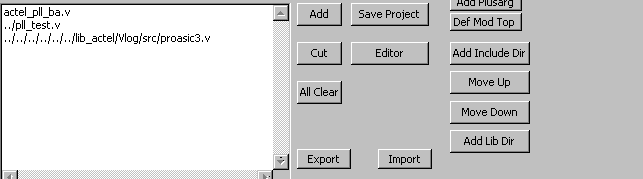

生成されたファイルは "actel_pll\smartgen\actel_pll"下に actel_pll.vとしてあります。

ProASiC3ライブラリファイルproasic3.vとテストベンチでプロジェクトを構成します。

"proasic3.vは、 "Libero\Model\actel\Vlog\src"にあります。

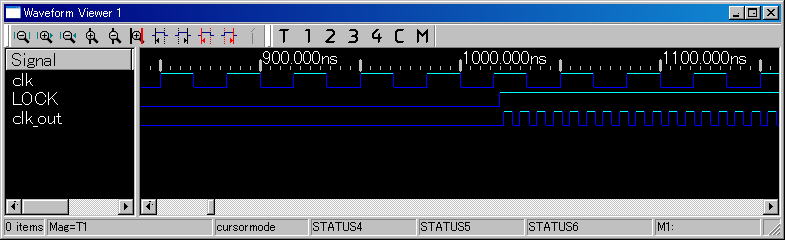

RTLシミュレーション波形です。

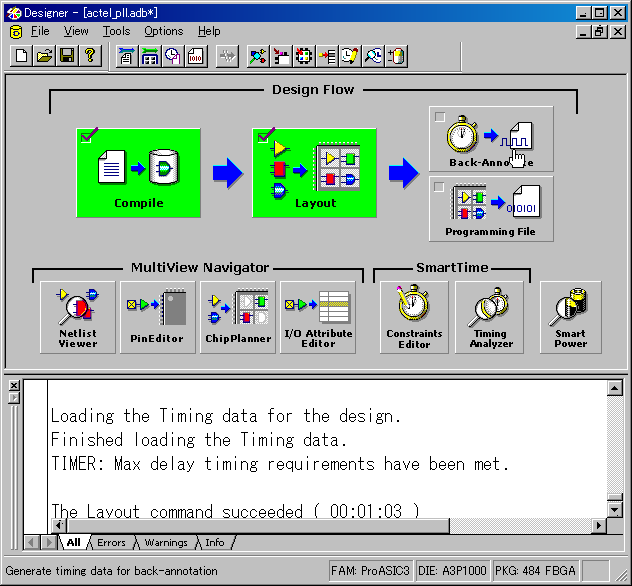

5.3.1.3 合成/レイアウト/バックアノテーション

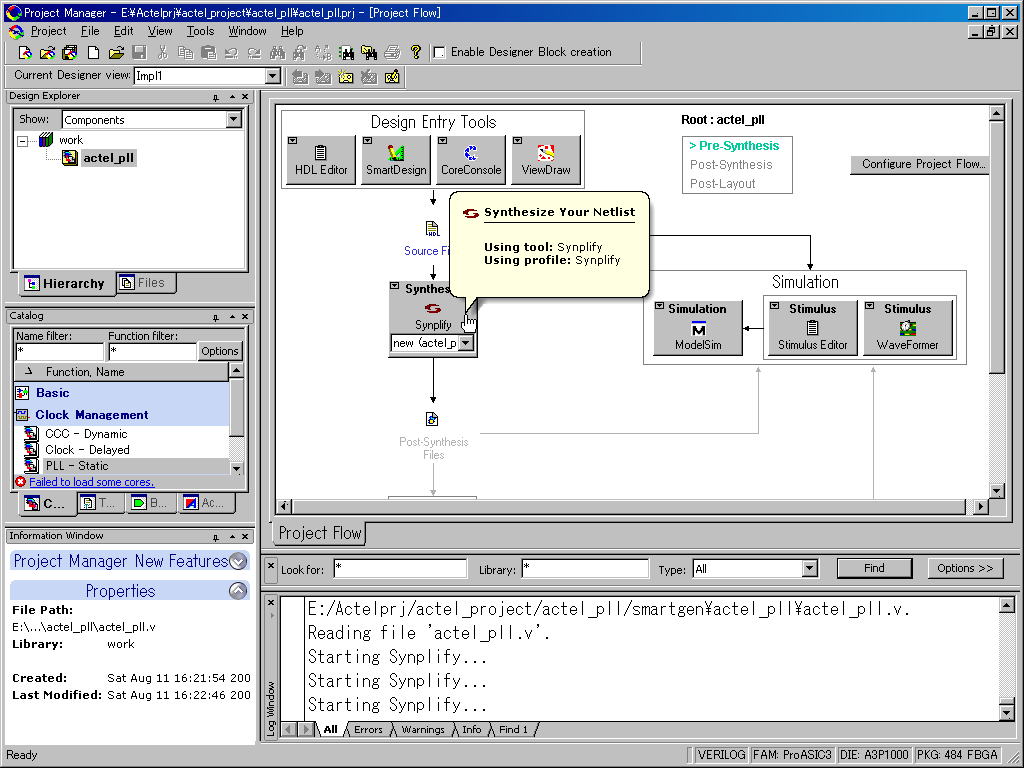

Synthesizeボタンを押します。.

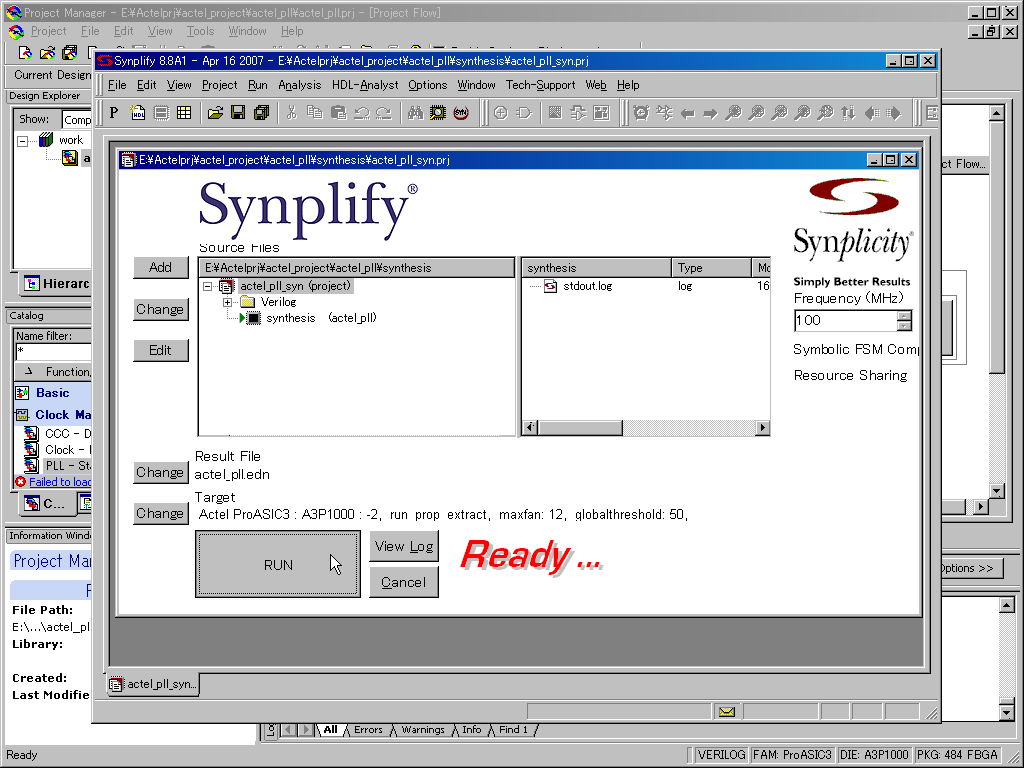

Synplify(R)が起動するのでRunを押します。

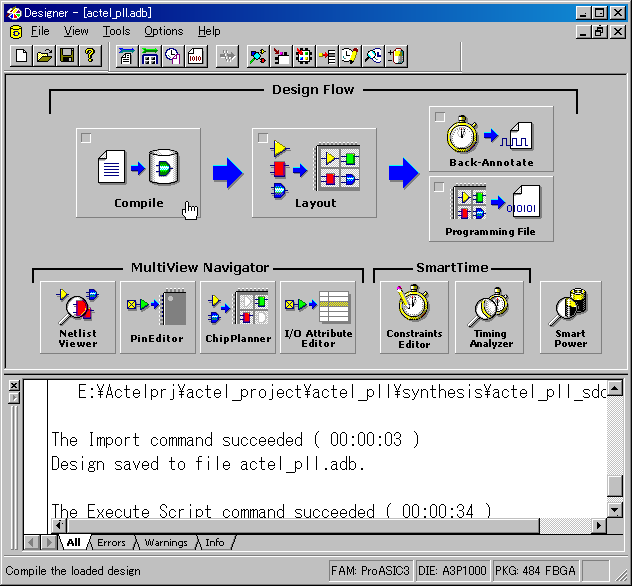

コンパイル ボタンを押します。

続いてイ、Layout と Back-Annotateボタンを押します。

5.3.1.4 SDF Delay Simulation.

合成と配置配線した結果として (actel_pll_ba.v) と SDF file (actel_pll_ba.sdf)

が "\actel_pll\designer\impl1"下にあります。.

合成結果のファイルにSDFファイルを呼び出す記述を下記のようにマニュアルで追加します。

プロジェクトは以下のようになります。Actelのライブラリファイルは、RTLのそれと同一です。

コンパイルモードは、 Xilinx/Actel としてください。

SDF warningが大量に出る場合は、 Suppress R.T. Warningをチェックしてみてください。

SDFディレイシミュレーション結果です。