6.2 インストール

インストール先は、QuartusⅡをインストールしたドライブとしてください。

<アドミニストレータ権限>

アドミニストレータ権限がないとインストールできません。以下の手順は、アドミニストレータ権限でインストールしてください。

<インストールEXE>

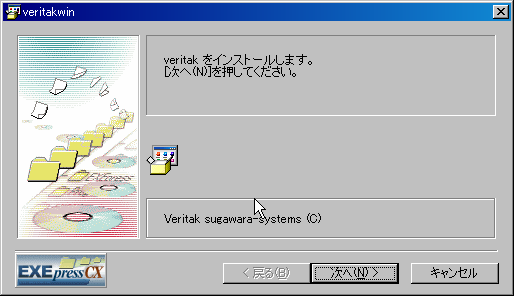

veritakwinL205A.exe をダブルクリックします。

セキュリティの警告(発行元が確認できない..)が出ることがありますが、構わず進みます。

すると下の画面となりますので、「次へ」を押してください。

6.0 VeritakーBasic(シェアウェア版)/Lite CQ版(フリー版)

トランジスタ技術2006年4月号付録にALTERA MAXⅡデバイス、EPM240T100C5 が搭載されています。このデバイスを例にシミュレーションする方法を説明します。

6.1 VeritakPro版との違い

殆どの機能は、そのまま利用可能です。行数制限、規模制限、期間制限 デバイス制限、等は入っておりませんが、以下の制限が入っています。

さらにLite CQ版では、パターン数制限が入っており、既定のパターン数に達すると、シミュレーションが中断されます。シェアウェアのBasic版では、パターン数制限は入っておりません。

なお、環境条件は、以下の通りです。

6.2 インストール

インストール先は、QuartusⅡをインストールしたドライブとしてください。

<アドミニストレータ権限>

アドミニストレータ権限がないとインストールできません。以下の手順は、アドミニストレータ権限でインストールしてください。

<インストールEXE>

veritakwinL205A.exe をダブルクリックします。

セキュリティの警告(発行元が確認できない..)が出ることがありますが、構わず進みます。

すると下の画面となりますので、「次へ」を押してください。

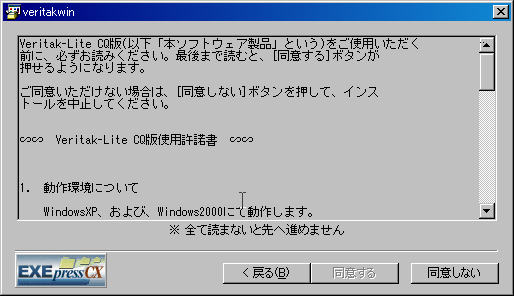

次の使用許諾書をよく読んでご同意いただける場合のみ、インストールを続けてくてください。

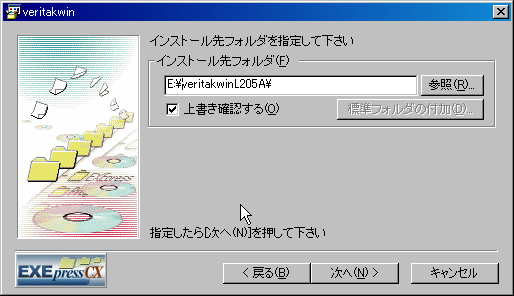

次の画面となります。筆者の場合は、”E:\altera\quartus51”がQuartusⅡのインストールフォルダでしたので、

同じE:ドライブとしました。

「次へ」を押してください。

「はい」を押します。

「次へ」を押すとインストールが開始されます。

6.3 ハローVerilog HDL World!

簡単なプログラムで動作を確認しておきましょう。

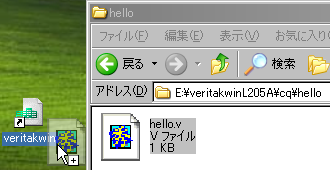

Veritakをインストールしたフォルダの下に"cq\hello"フォルダがあります。そのなかの

"hello.v"をveritakwinアイコンにドラッグ&ドロップします。

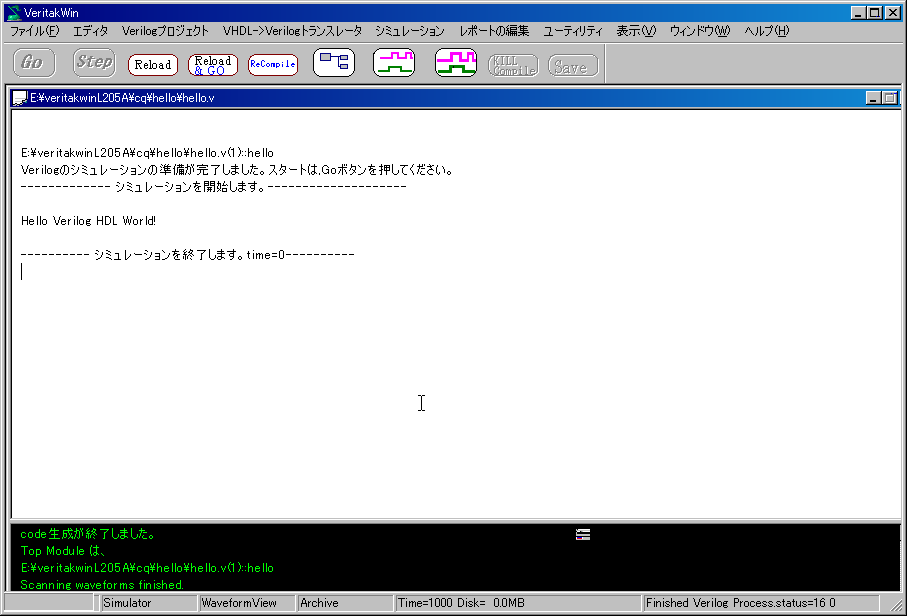

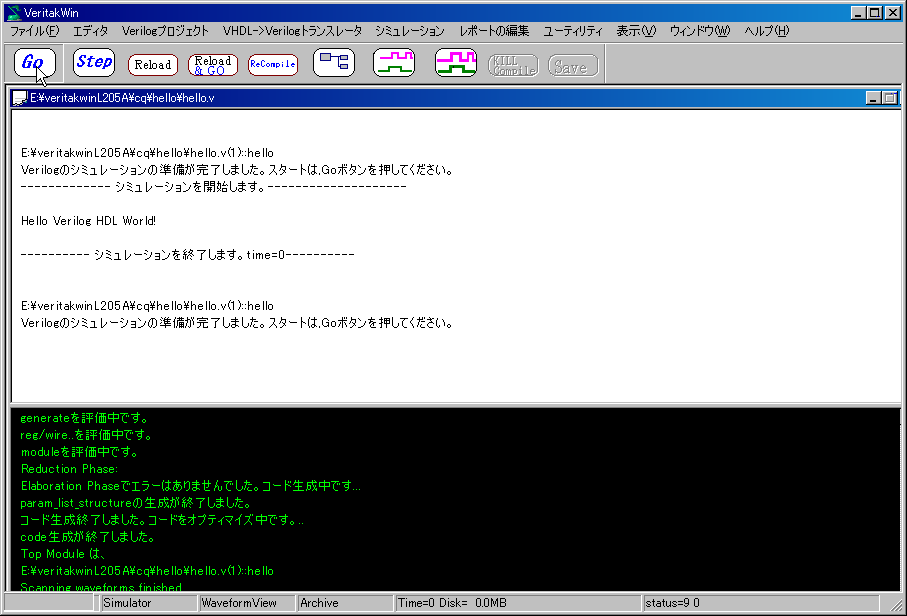

するとシミュレータのコンパイルが始まり、シミュレーションが実行され次の画面となります。

ソースファイルを見るには、下のペインで

E:\veritakwinL205A\cq\hello\hello.v(1)::hello

または、上のペイン

E:\veritakwinL205A\cq\hello\hello.v(1)::hello

の行をダブルクリックします。

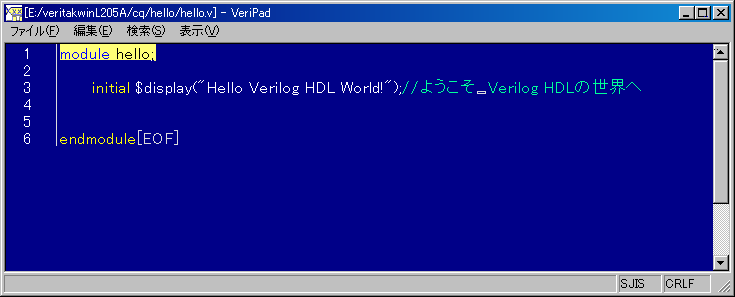

すると付属のエディタVeriPadが開きます。

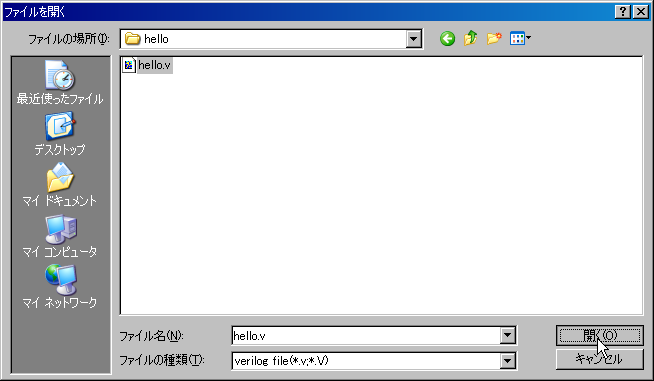

別なファイルの開き方

ファイルー>開くで同じファイルを開いてみましょう。

するとコンパイル後にユーザ入力待ちになりますので、Goボタンを押すことで実行します。以上でインストールの確認は終了しました。

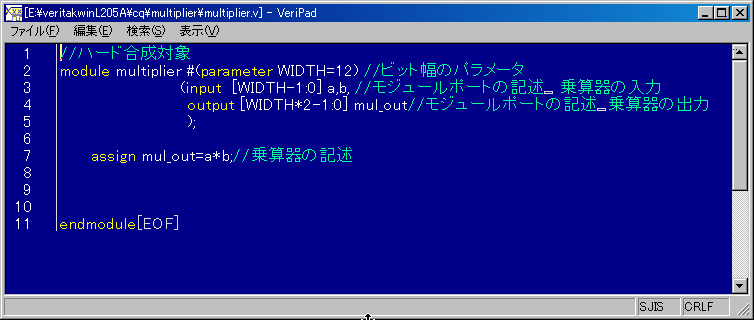

6.4 乗算器の記述

次に簡単な乗算器のを記述してみましょう。

以下は、12ビットx12ビット=24ビット符号なし、乗算器のハードウェア記述です。

たったこれだけのソースですが、しっかり論理合成可能です。

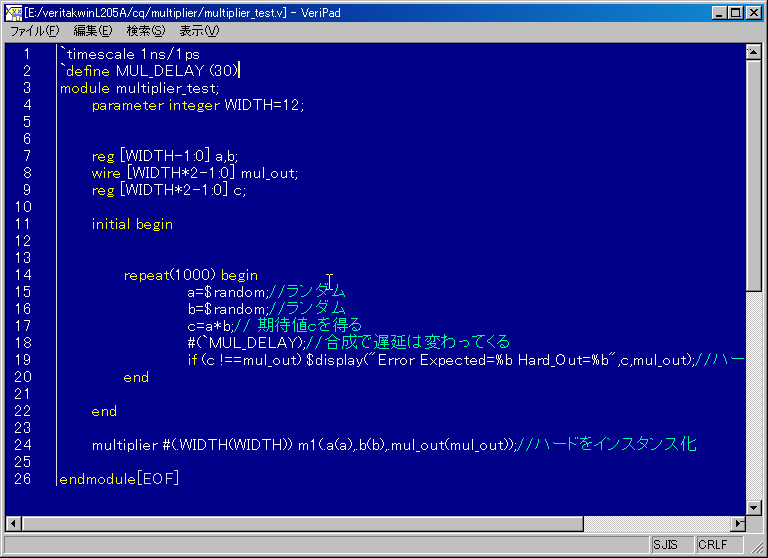

さて、この回路をテストする記述が必要です。

以下のようにテストベンチを記述してみました。

二つのソースができました。一つは、論理合成用ハードの記述、もう一つは、それをテストする記述です。

これら二つのソースをシミュレータ上で動かすために、Veritakのプロジェクトを作成します。

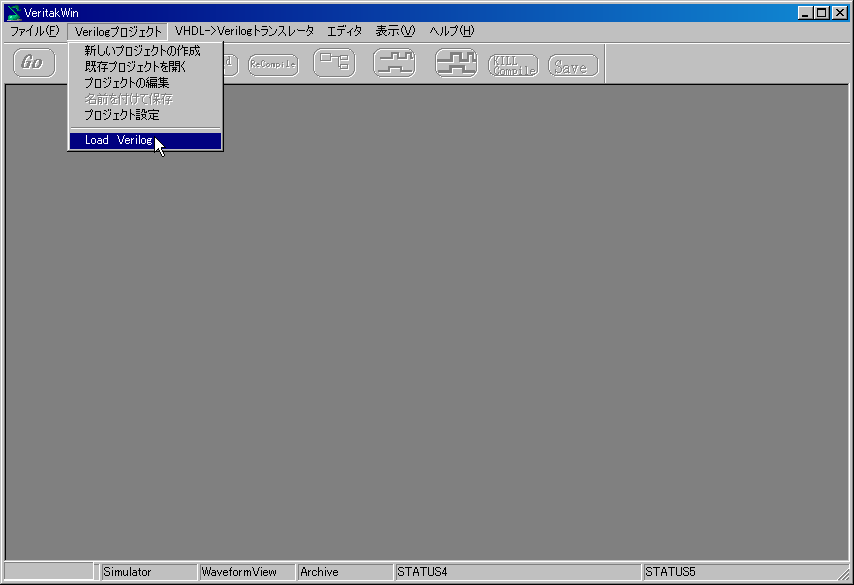

まずは、すでに作成してあるプロジェクトをロードして動作を見てみましょう。

プロジェクトファイル、cq\multiplier\multiplier_RTL.vtakprj を次の手順でロードします。

ファイルを開くダイアログが出現しますので、以下のプロジェクトファイルを選択します。

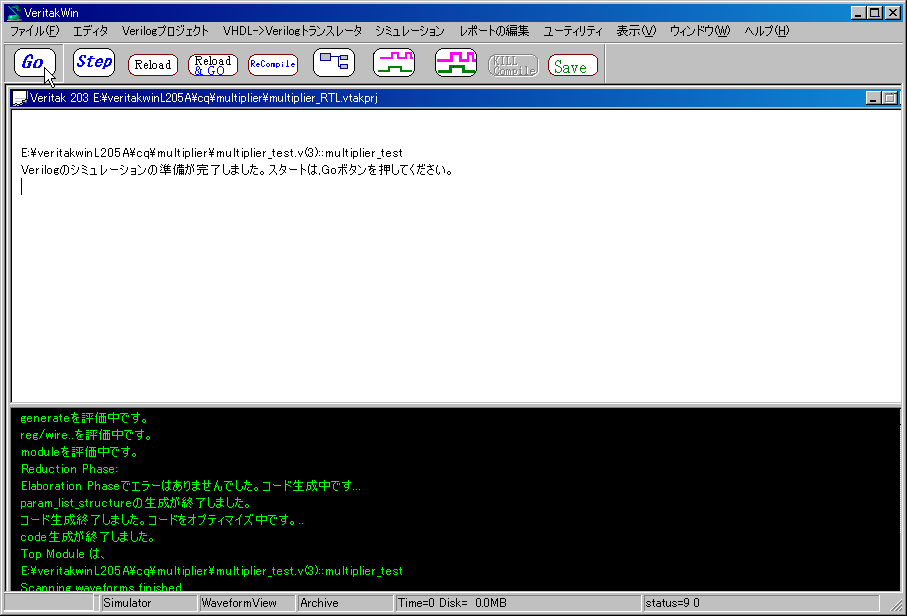

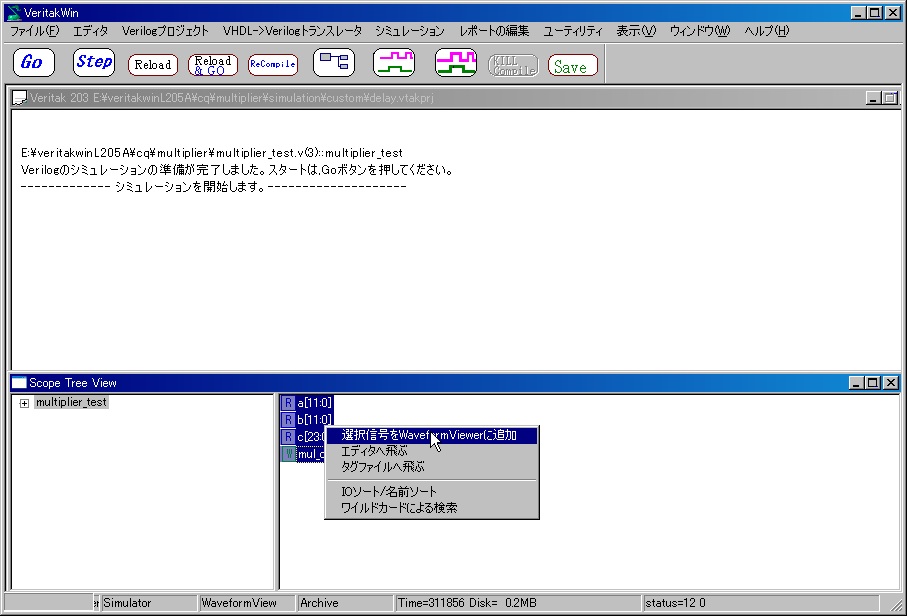

すると、コンパイルが始まり、次の画面となります。Goボタンを押し、シミュレーションを実行します。

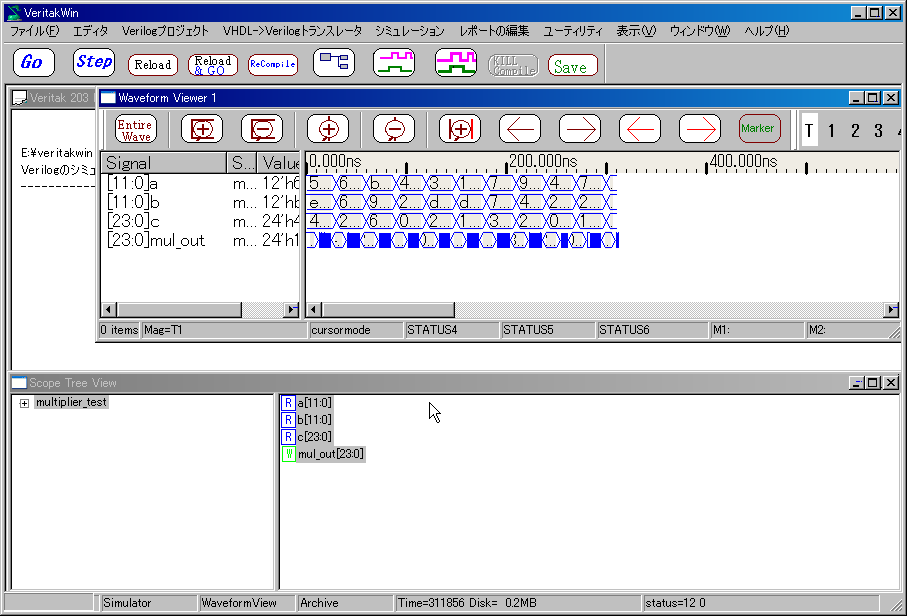

すると次の画面になります。

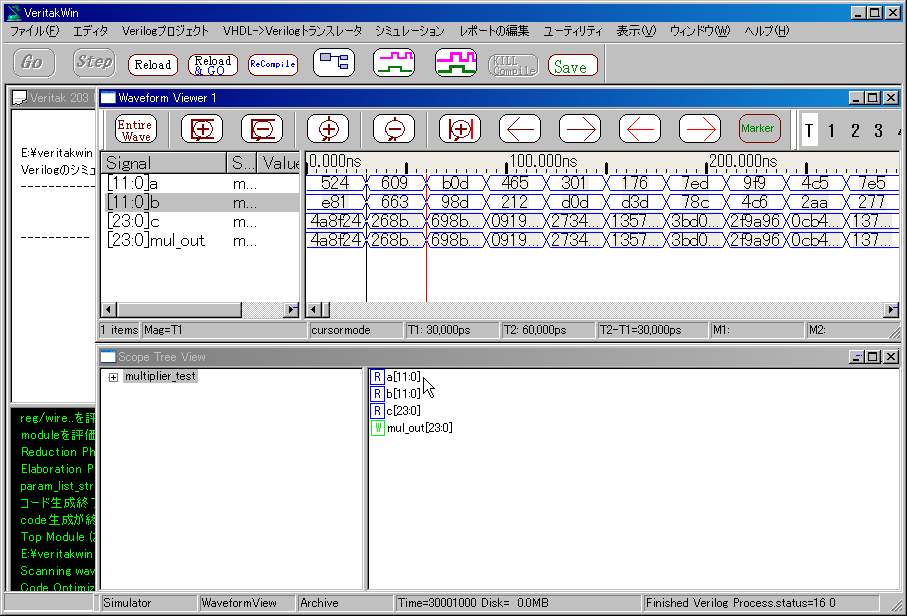

a、bのランダム入力に対し、テストベンチの期待値cとハードの記述mul_outの乗算器出力が一致していることが分かります。

また、データの間隔は、テストベンチで記述した30 (T2-T1=30.000ps) nsになっていることも分かります。

この回路は、フリップフロップがありません。記憶のない組み合わせ回路のみからできています。つまり、a,bの入力が変化すると出力mu_outは、ただちに変化するということです。a,b

の値が決まれば、cの値は一意に決まります。

ここでは、仮想的に遅延0と考えてシミュレーションしています。RTLシミュレーションでは、ロジックの遅延0と考えたいわば理想状態をモデル化していることになります。

6.5 カウンタの記述

乗算器は、フリップフロップがありませんでしたが、0の次は、1、1の次は、2...という具合に前の状態に対して、次の状態が決まっていきますので、何らかの状態を覚えておく記憶が必要になります。前の状態に応じて、次の状態が決まる回路をステートマシンと呼んでいます。カウンタもステートマシンの一種です。

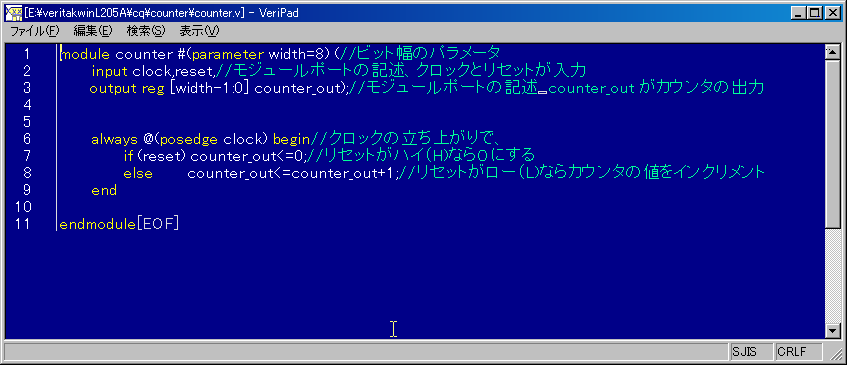

それでは、カウンタ ハードの記述です。

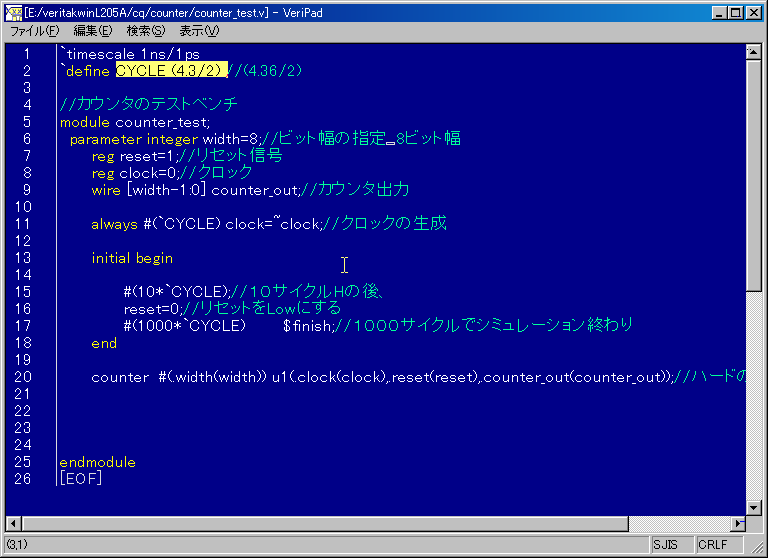

カウンタのテストベンチの記述です。

以上のソースは、cq\counter\ に入っています。この二つのソースをシミュレーションするために、Veritak プロジェクトを作成してみましょう。

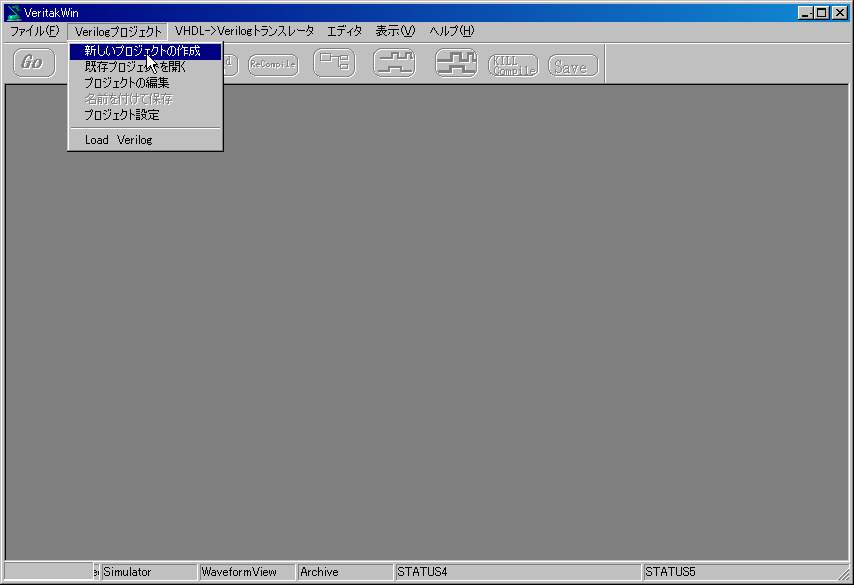

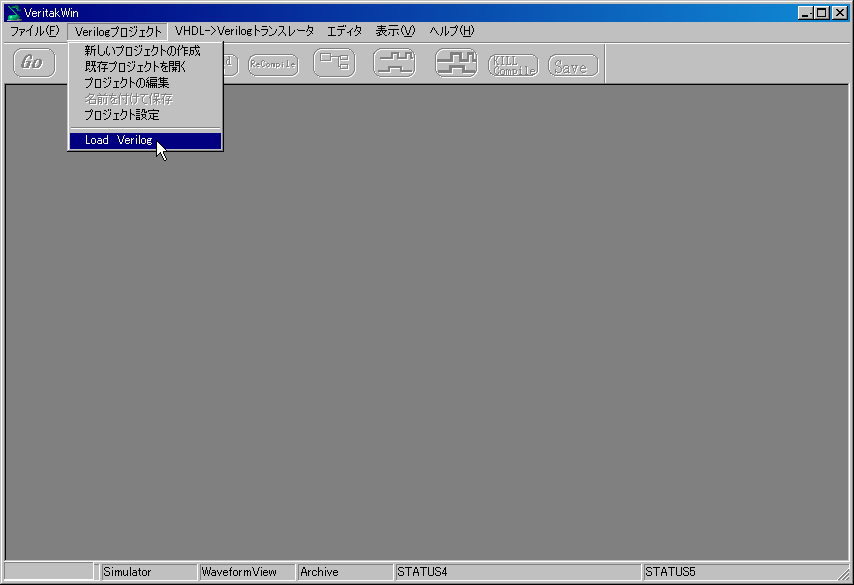

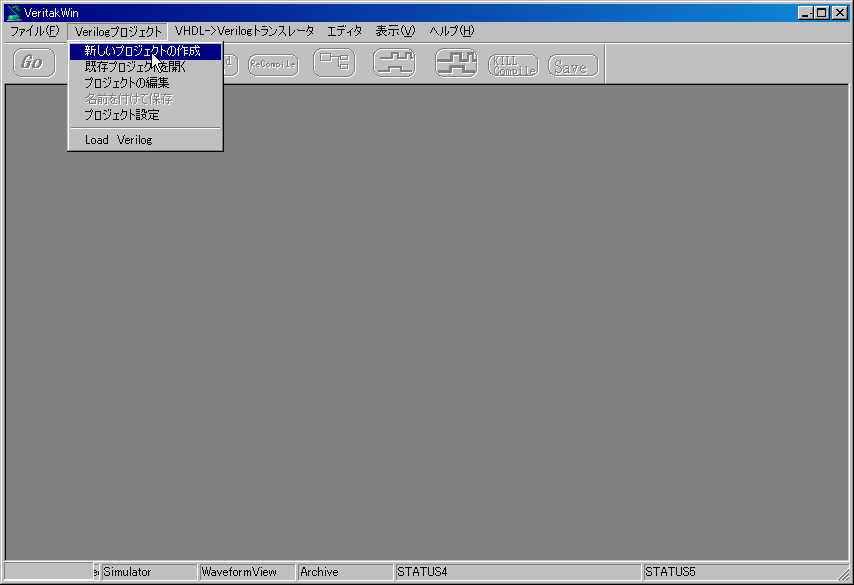

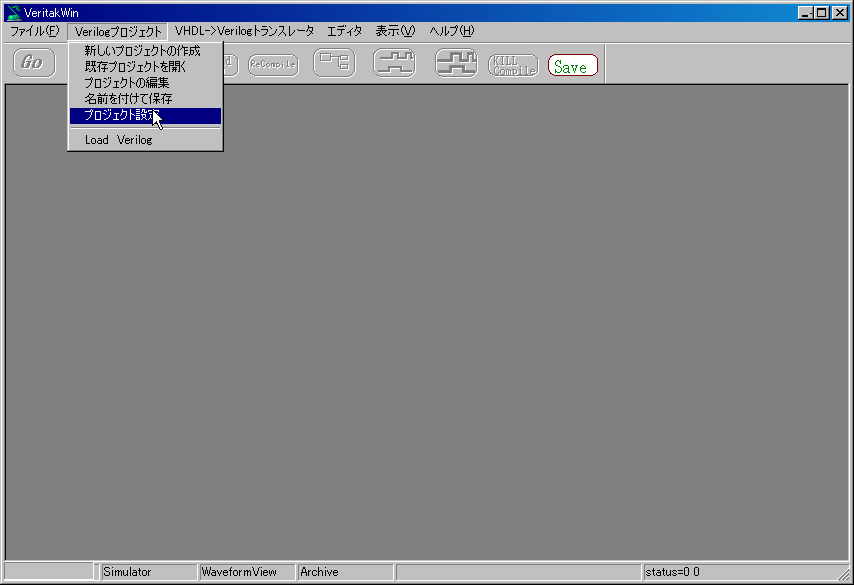

Veritakを起動後、[新しいプロジェクトの作成」をクリックします。

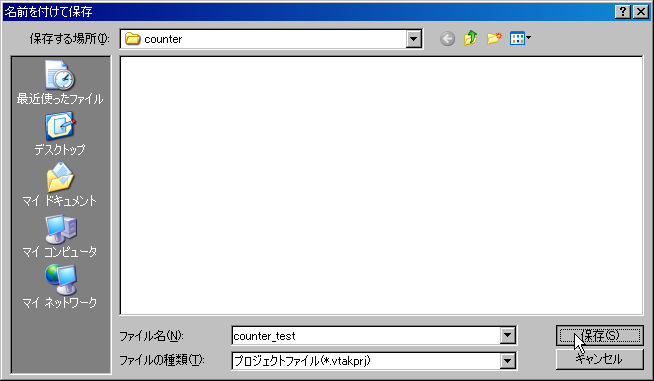

名前をcounter_testにして、プロジェクトを作成します。

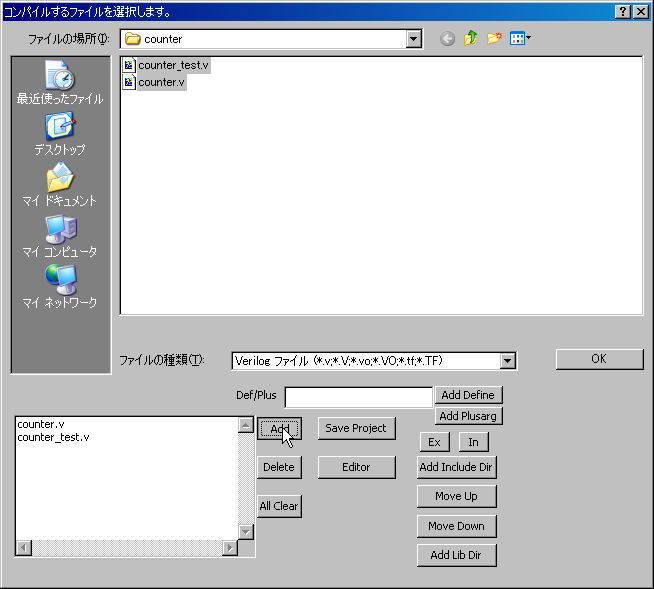

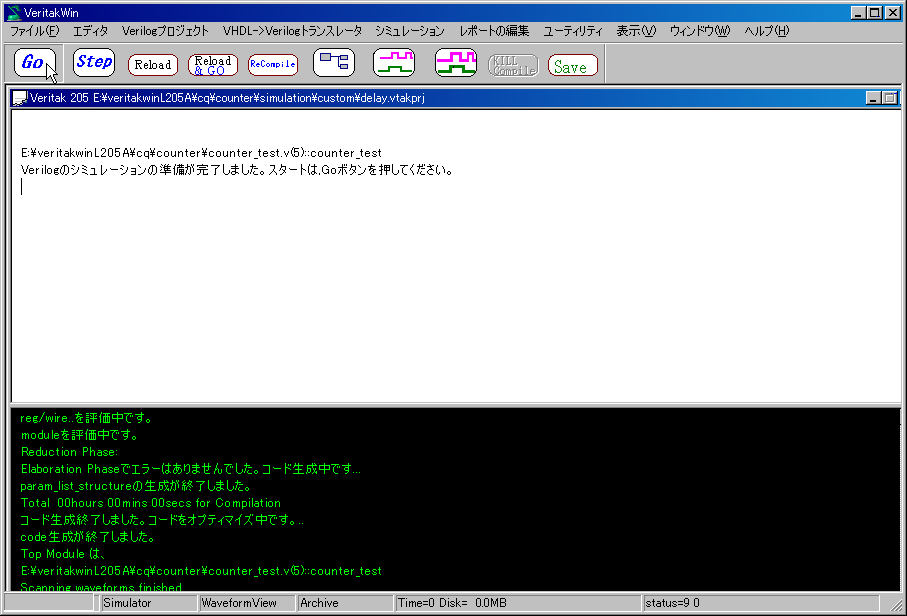

すると、次の画面となるので、二つのファイルを選択し、Add をクリックします。

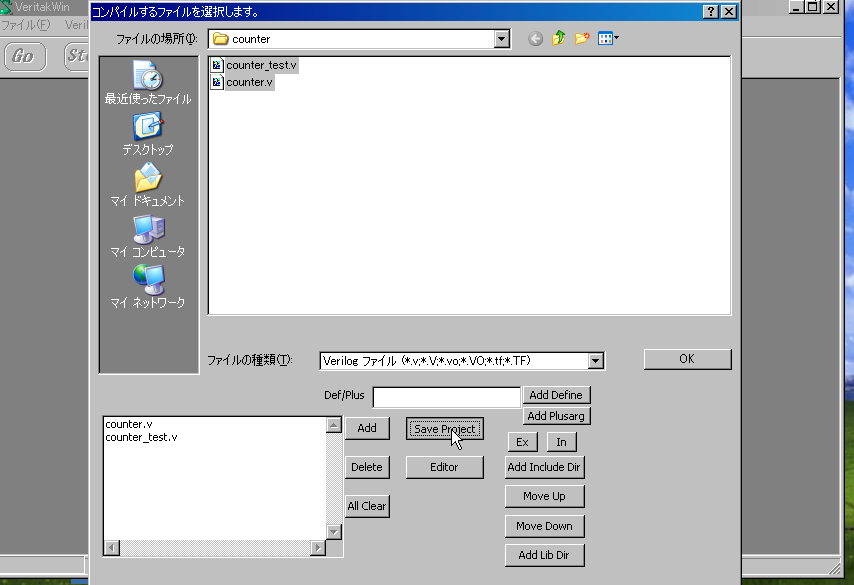

Save Projectを押すと、プロジェクトの内容がディスクに書き込まれます。

OKボタンを押し、今作ったプロジェクトをロードしてみます。

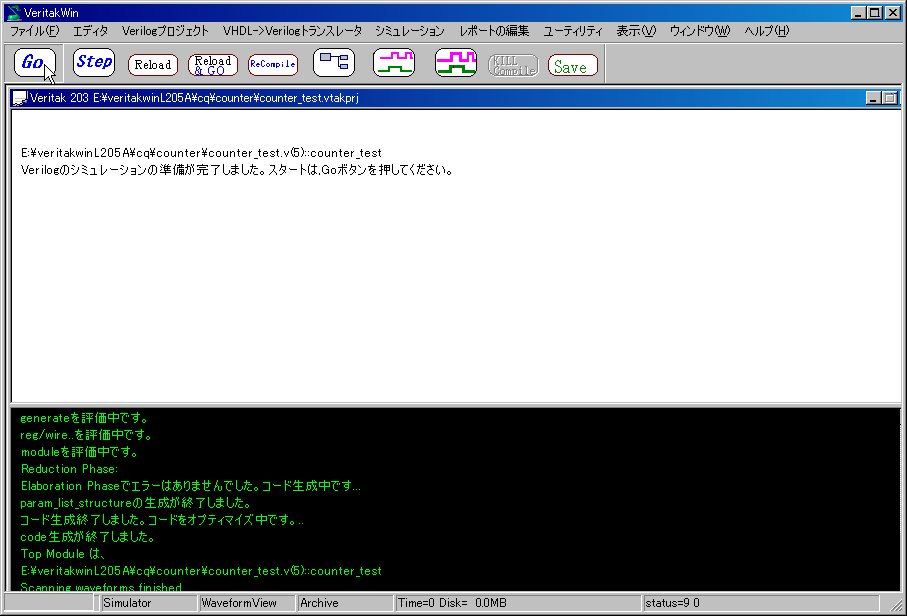

するとコンパイルが始まり、ユーザ入力待ちになりますので、Goボタンを押します。

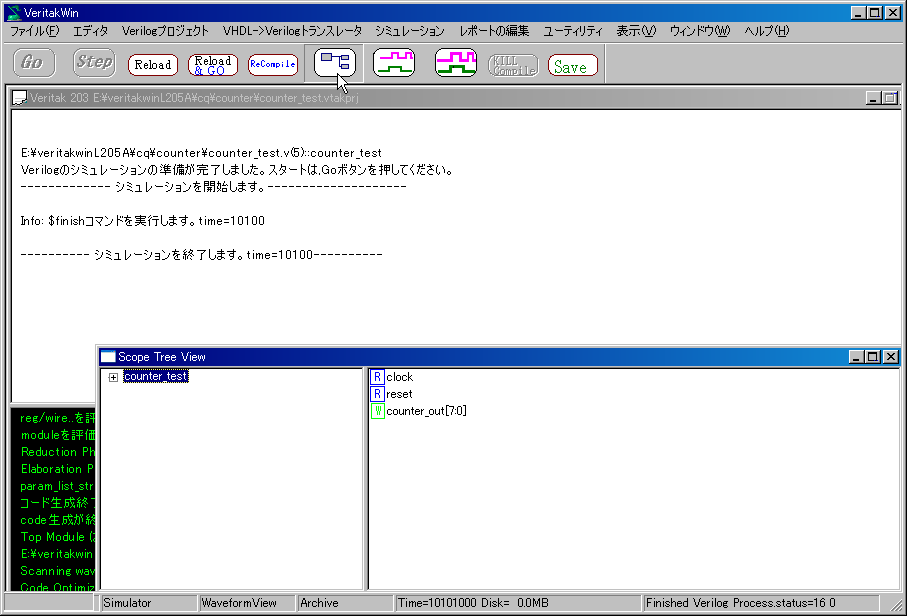

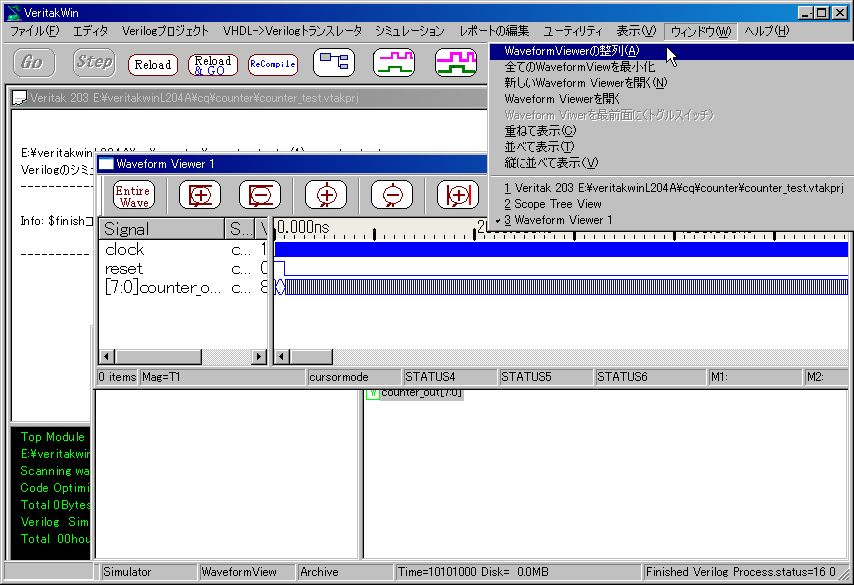

シミュレーションはすぐ終わります。下のように、階層ビューアを出してみます。

波形を出すには、下のように信号を選択して、右クリック、選択信号をWaveformViewに追加をクリックします。

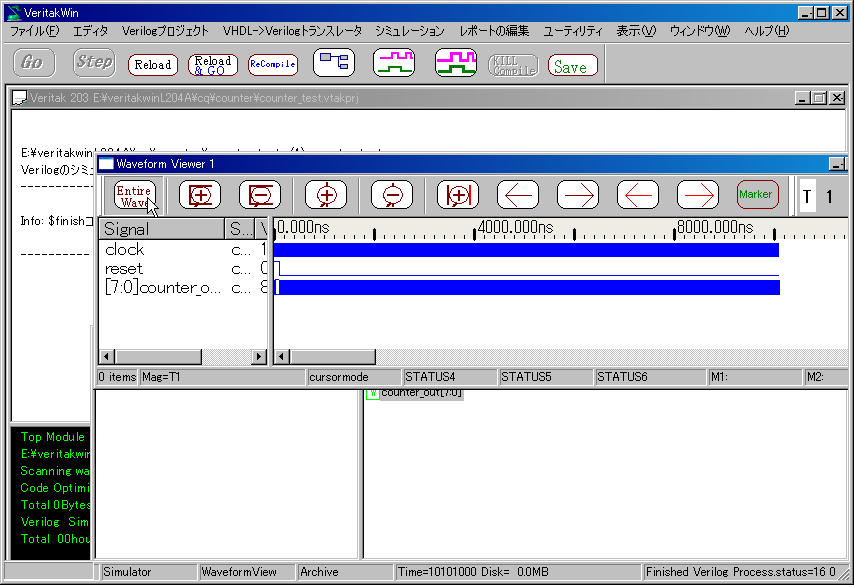

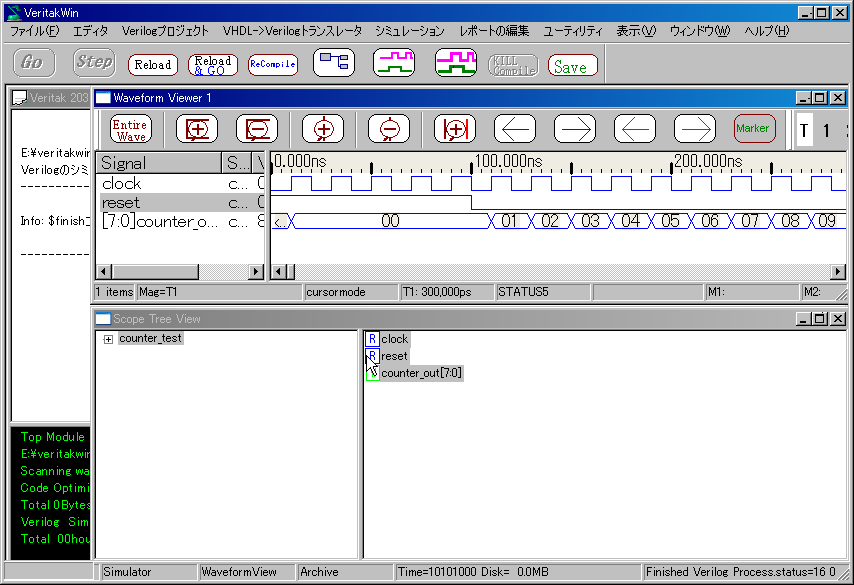

Entireボタンを押すと波形全体が見れます。

ビューを整列させたいときは、下のようにします。

+-ボタンで波形の拡大縮小は自由です。

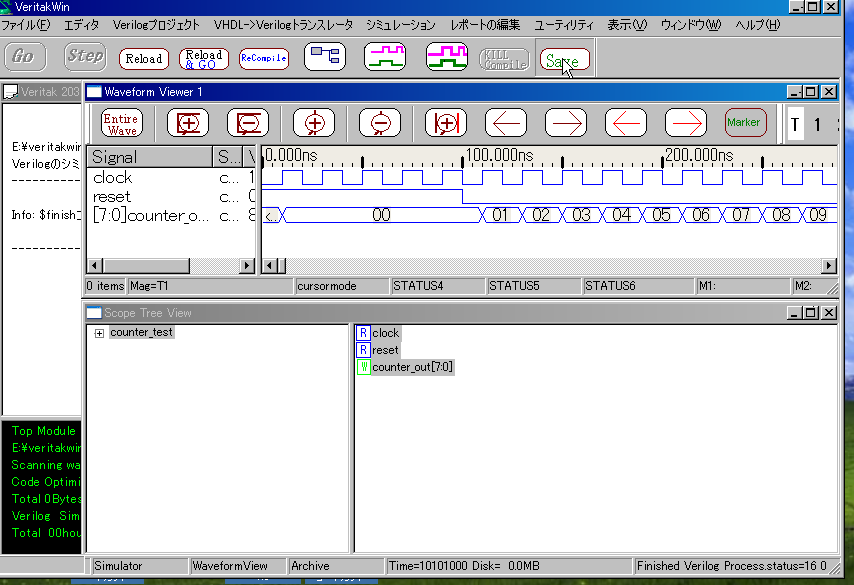

波形の並びのフォーマットは、Saveボタンでプロジェクトファイルに保存されます。

次回プロジェクトをロードするとき、再び波形を追加する必要はありません。

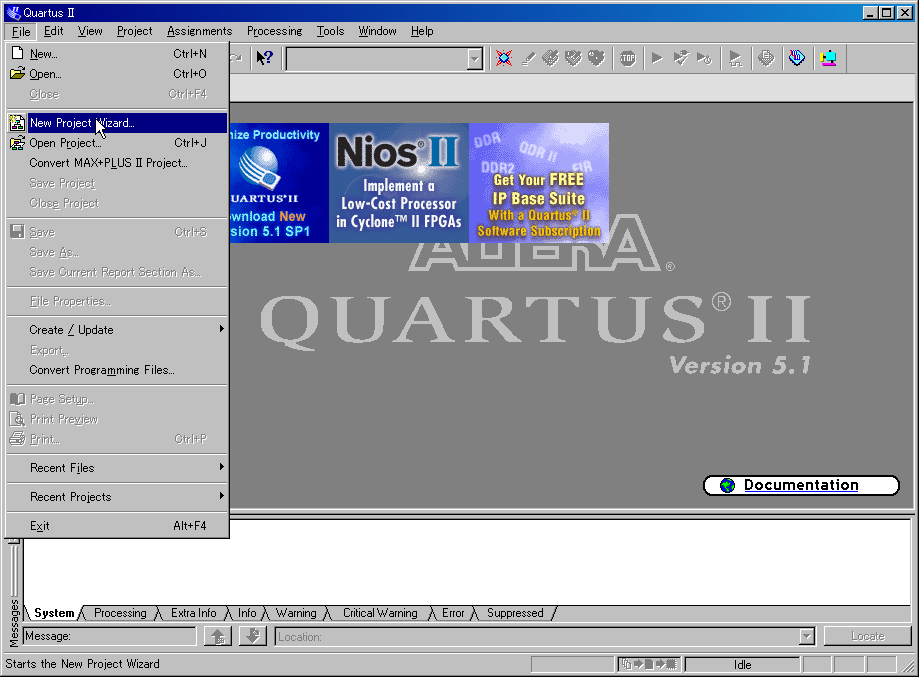

6.6 論理合成

それでは、Quartusで論理合成してみましょう。そのためには、Quartusのプロジェクトを作成する必要があります。

次の手順で作成します。

New Project Wizard を押します。

すると次の画面になるので、「Next>」を押します。

プロジェクトの作業フォルダを指定します。

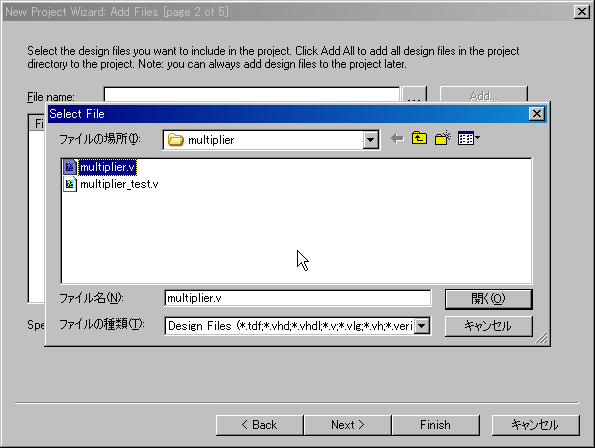

ハード合成対象のmultiplier.v を開きます。

次の画面となります。「Next>」を押します。

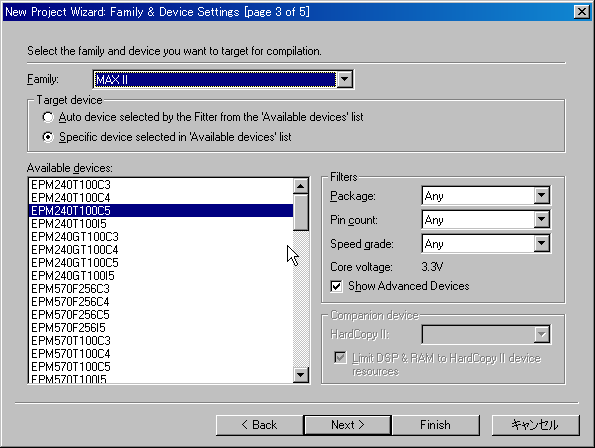

次にデバイスを選択します。「Next>」を押します。

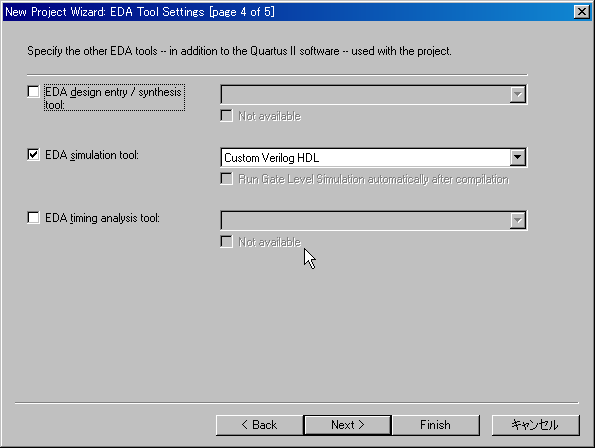

EDA simulation tool は、Custom Verilog HDLを選択します。

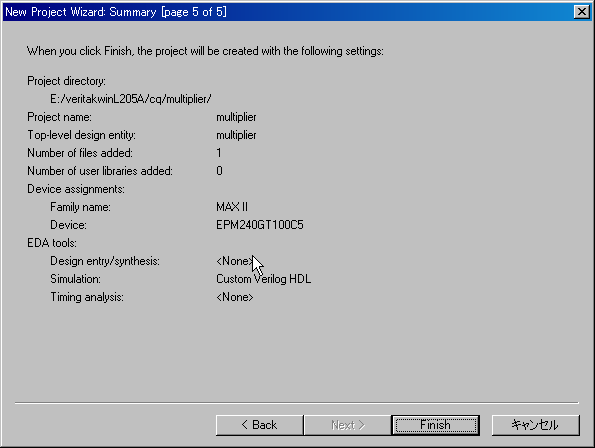

「Finish]を押します。これでQuartus上のプロジェクトが完成です。

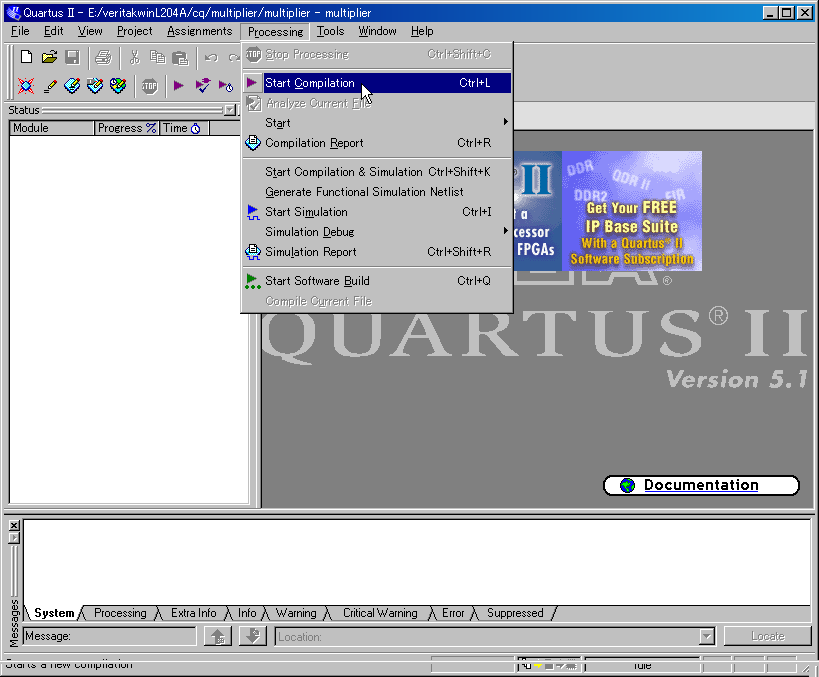

Start Compilationで論理合成を開始します。

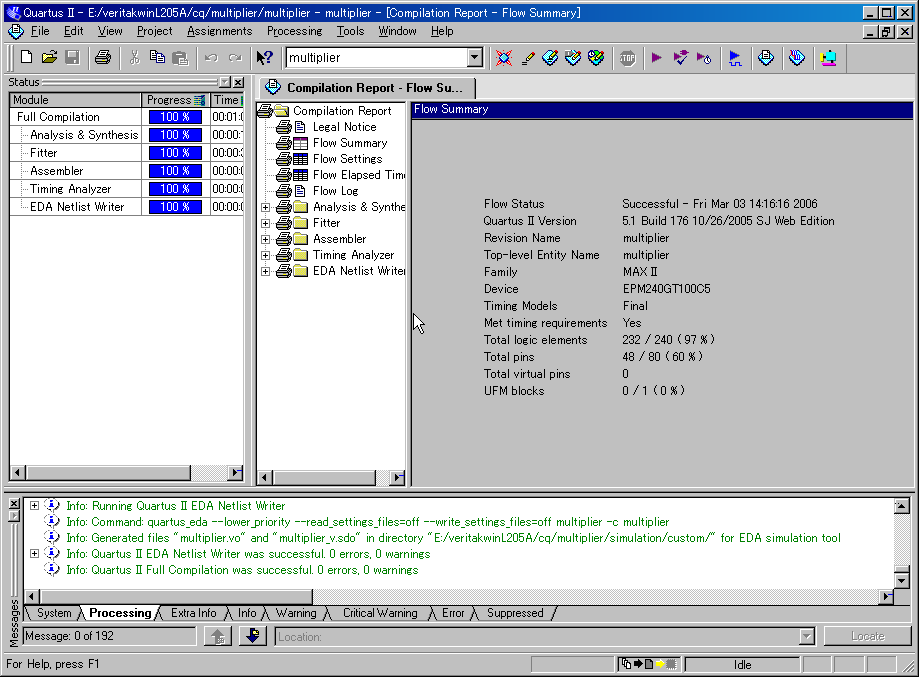

コンパイルに数分かかります。全部終わった後、Fitter Summaryを見ると どれくらいのリソースを消費しているのか分かります。

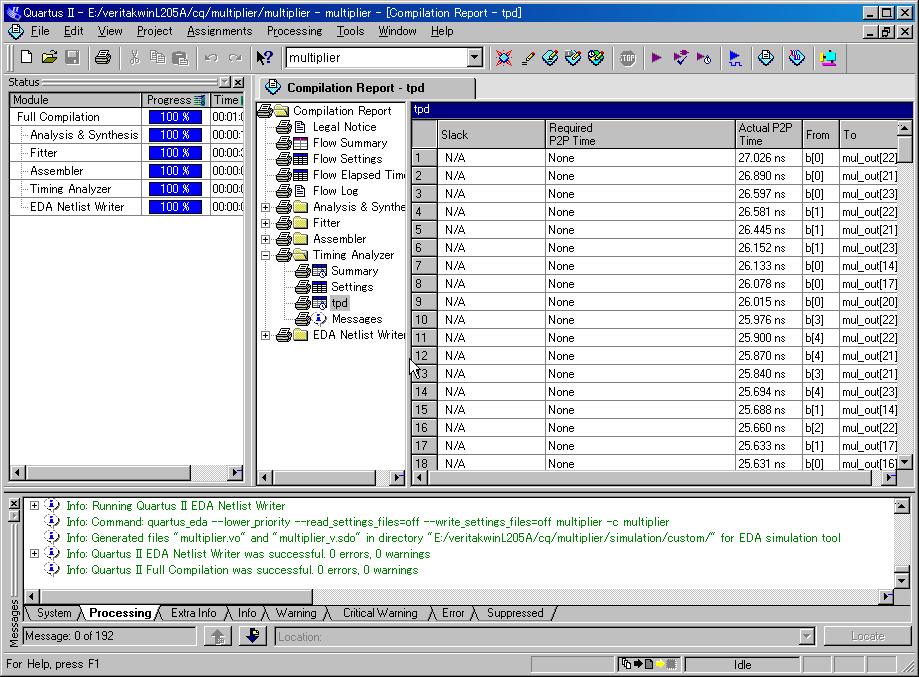

Timing Analyzer->Tpdでみると遅延の様子が分かります。 最大遅延は、27.025nsでそのパスは、b[0]->mul_out[22]であることが分かります。論理合成と配線が行われ、配線後の配線遅延も含めた結果になっています。

6.7 遅延シミュレーション

6.7.1 乗算器

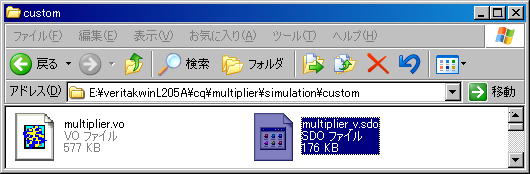

Quartusの論理合成で論理合成したネットリストと遅延値のファイルが出来ています。以下のフォルダに入っているので、

テキストエディタでどんなものができているか眺めてみるとよいでしょう。

以下のフォルダに出来上がっています

multiplier.vo が論理合成したネットりストで、RTLで記述したmulitiplier.v

がMAXⅡ上のゲートレベル回路に

置き換わったものです。しかし、この回路は、ゲート内の遅延や、配線遅延などの遅延情報はありません。

遅延情報は、SDF(Standard Delay Format)によるファイルが別になっていてそれが、multiplier.vo

です。

数行のハードウェア記述が、一万行を超えるゲートレベル記述と約5000行の遅延値ファイルになりました。

同様にして、モジュールトップのパラメータ数文字を書き換えるだけで任意ビット数の乗算器ができます。

合成の確認として、このファイルを読み込んでVeritakでシミュレーションしてみましょう。

そのために遅延シミュレーション用のVeritakプロジェクトを別に作ります。

Veritakプロジェクトは、上のフォルダ上に作ります。

Veritak起動後、新しいプロジェクトの作成をクリックします。

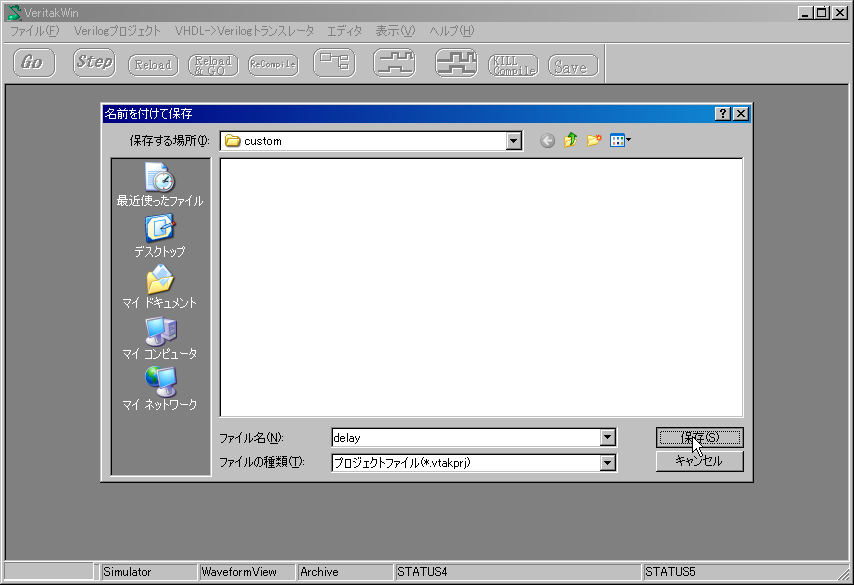

multiplier\simulation\custom のフォルダに行って、delay という名前のプロジェクトを作成します。

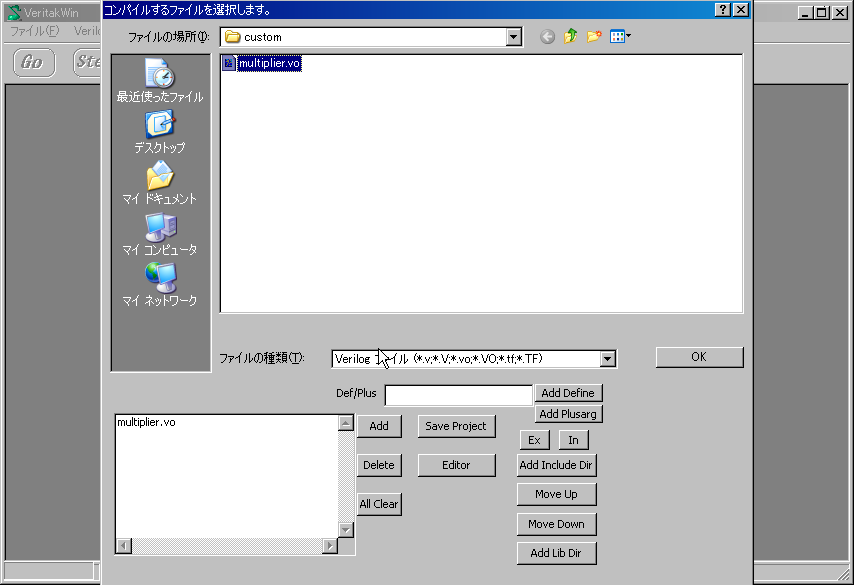

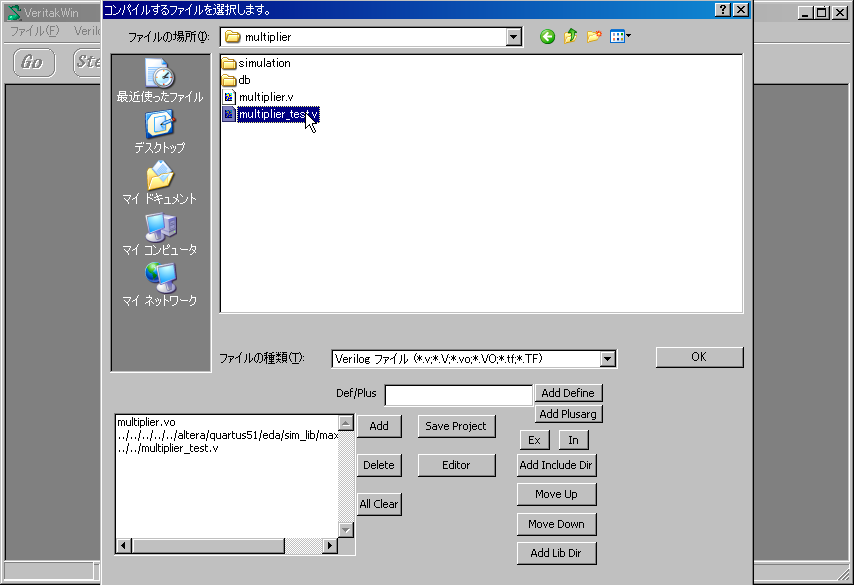

すると次の画面となりますので、ネットリストmultiplier.vo を選択します。

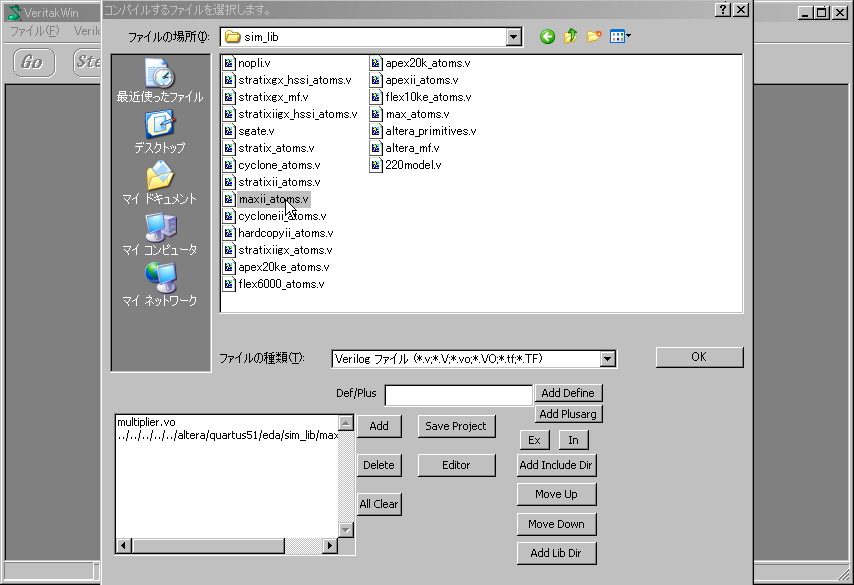

次にquartusをインストールしたファルダ\eda\sim_lib に行って、デバイスのゲートレベルのライブラリファイルをプロジェクトに加えます。

今回は、MAXⅡデバイスですので、maxii_atoms.v です。

最後にRTLシミュレーションで作成したベンチをプロジェクトに加えます。

この段階で、SaveをするとDiskに設定した内容が書き込まれます。

Alteraの遅延シミュレーションでは、コンパイルが重くなるので、専用のコンパイルモードが用意されています。

プロジェク設定をクリックします。

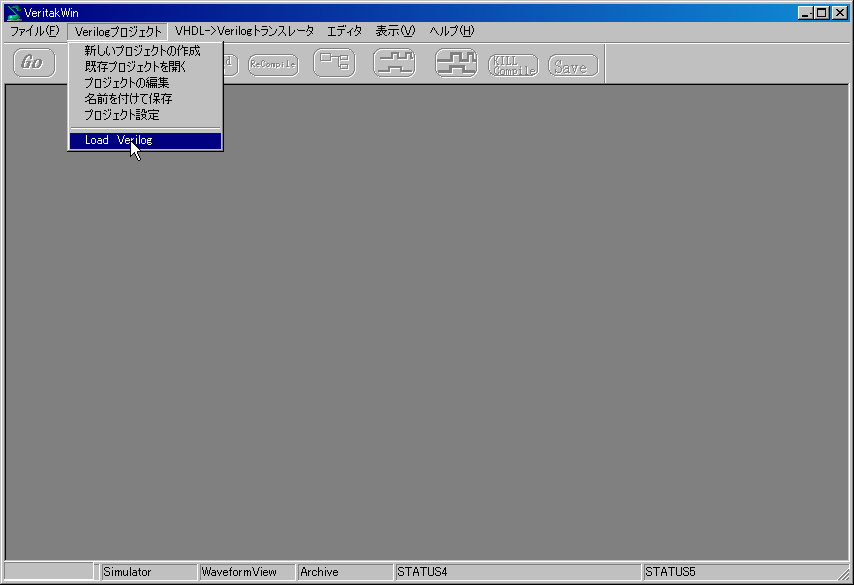

Compile Modeを Altera SDFに設定します。

OKを押し、Saveボタンを押します。

プロジェクトが出来上がりましたので、出来上がったプロジェクトをロードします。

コンパイルが終了すると以下の画面となりますので、Goでシミュレーションを走らせます。

Veritak Lite版では、パターン数制限がある為、途中で、メッセージがでます。「OK」押してください。

観測する信号を選択します。

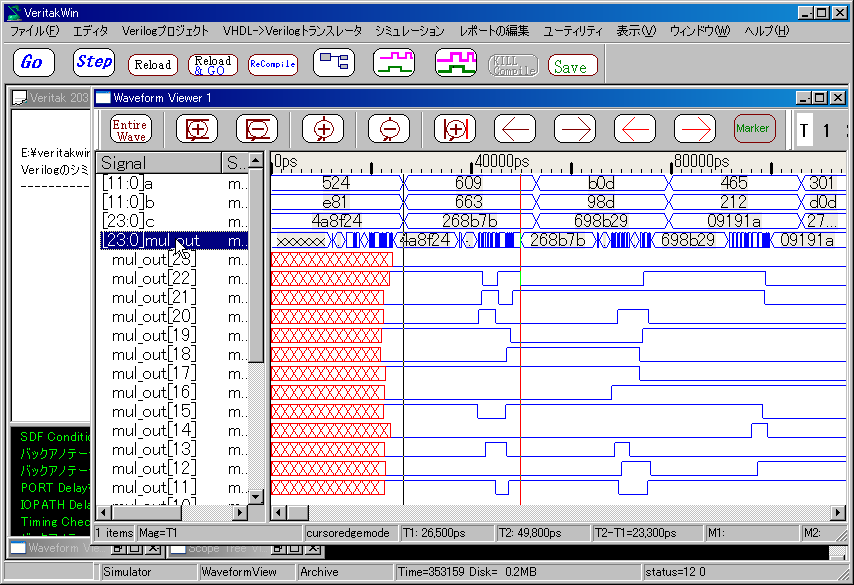

Entireボタンを押すと波形全体を見ることが出来ます。

この波形を観測してみると、合成した回路は20数nsの遅延を持って動いているようです。

信号をダブルクリックするとビットに展開されます。もう一度ダブルクリックすると元に戻ります。

ハードで合成した信号は、下のカーソル間で23.3nsであることが分かります。また、ビット毎に

遅延が違うのは、当然ですが、それが、一定していないことに注目してください。この遅延は、

パターンで違うことが分かります。シミュレーションの遅延は、このようにパターンで変わってくる

いわば、ダイナミックな遅延です。ところがQuartusが言ってくる遅延は、静的遅延の最大値です。必ず、

ダイナミック遅延<=静的遅延

という関係になっています。

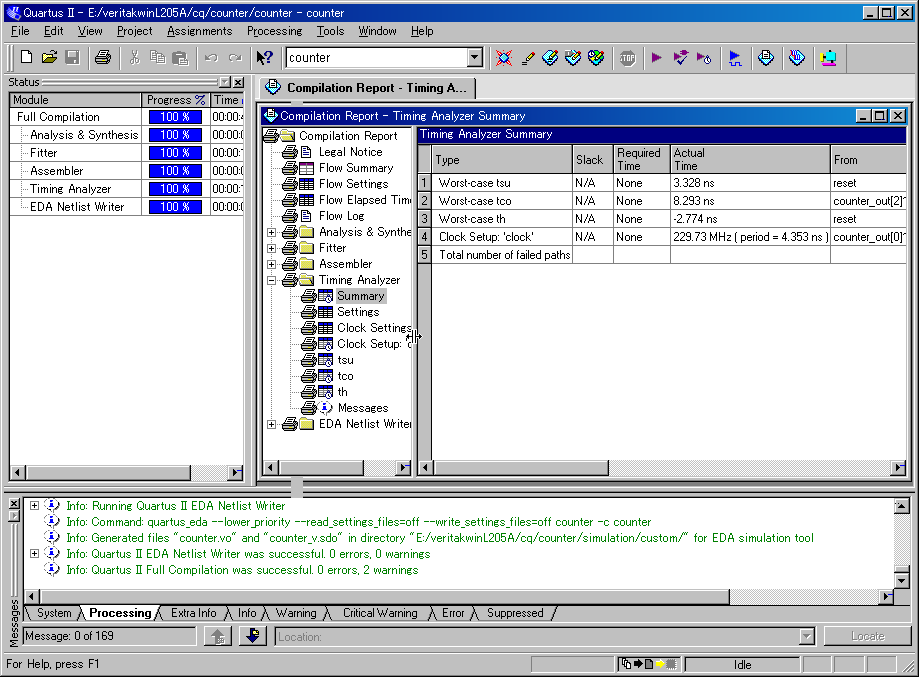

6.7.2 カウンタ

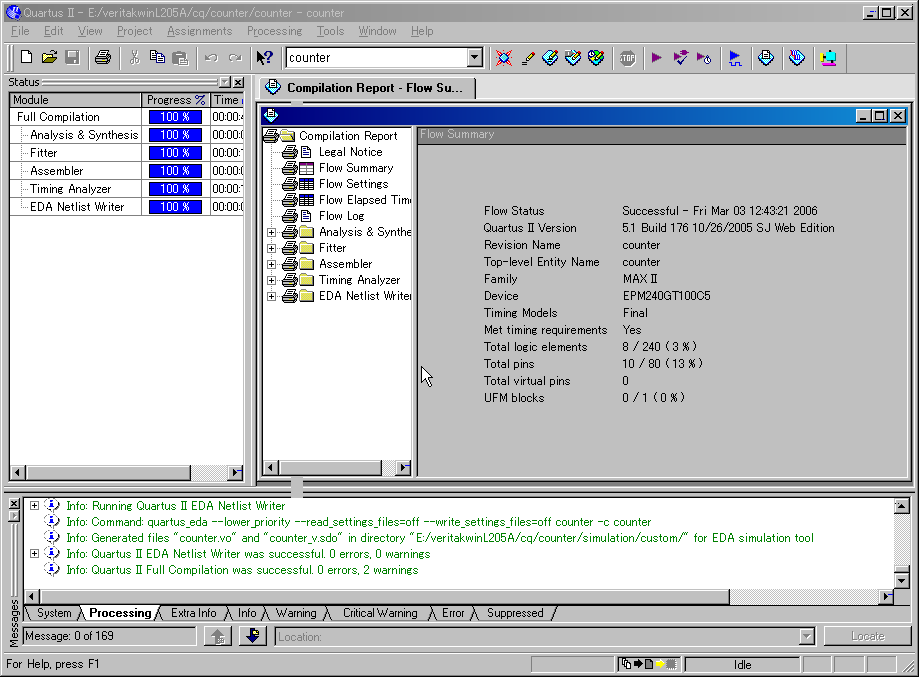

同様にしてカウンタを合成し、シミュレーションしてみましょう。

合成結果です。ご覧のように8ビットのカウンタでは、リソースをあまり消費しません。

Timing Analysisの結果です。この回路は、内部的には、229.73MHzで動くことを示しています。

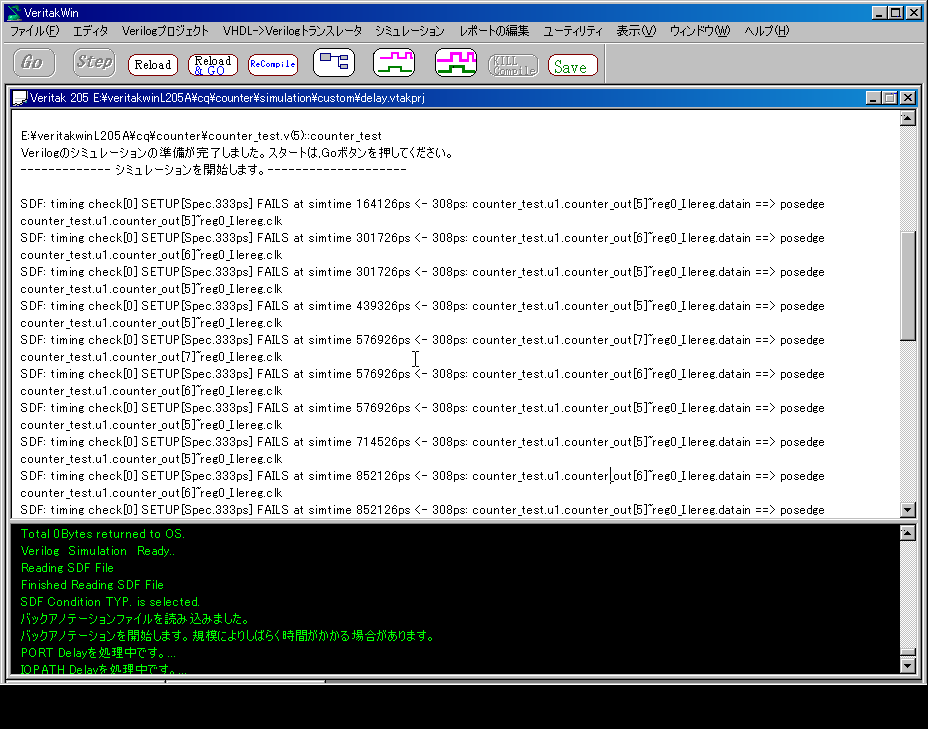

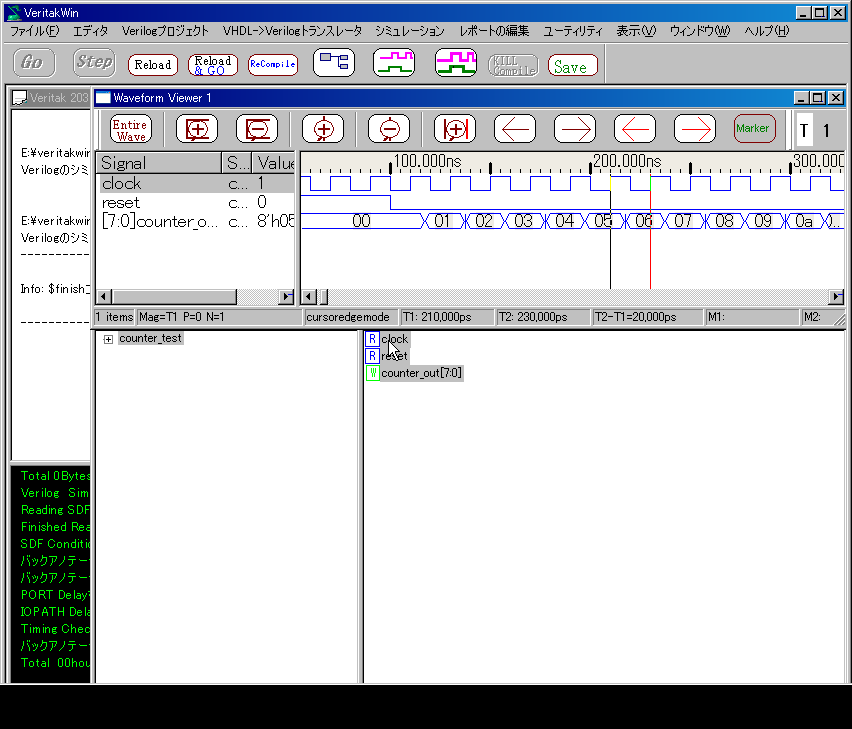

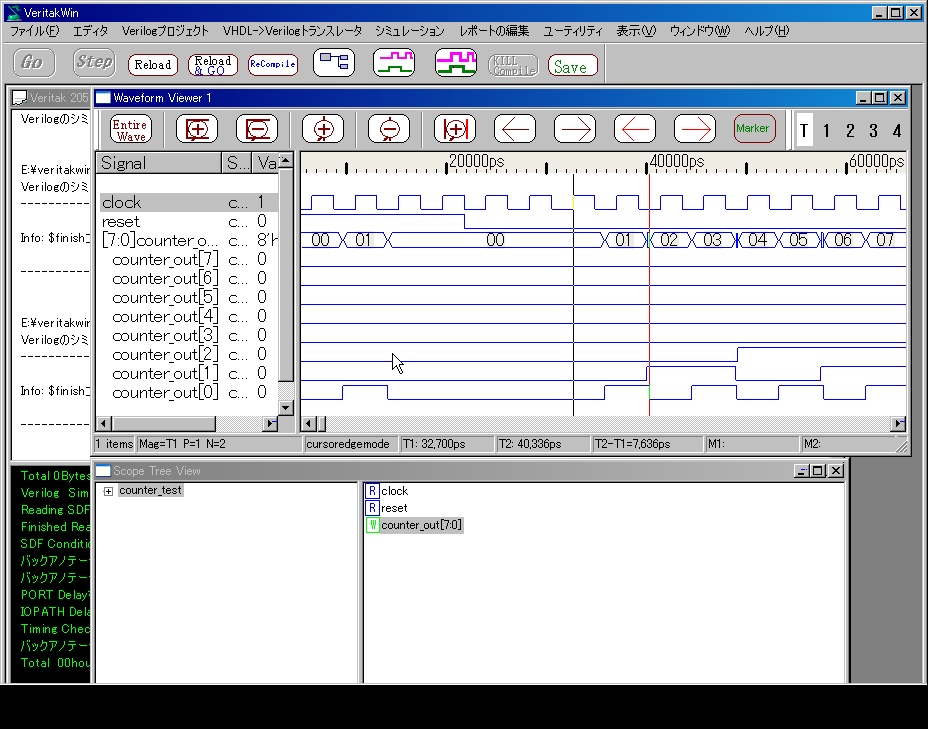

シミュレータを走らせてみると次のようになりました。

カウンタがインクリメントされ、合成が意図したようにできていることがわかります。

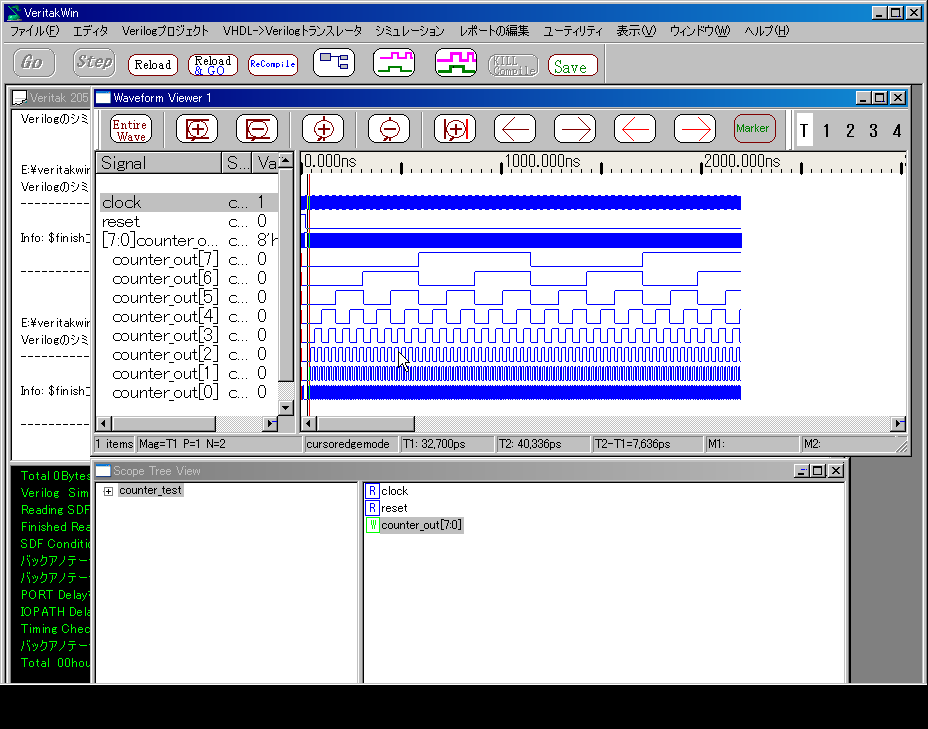

合成器は、229.73MHzで動くと言っているので、それで動くことを確認しておきましょう。

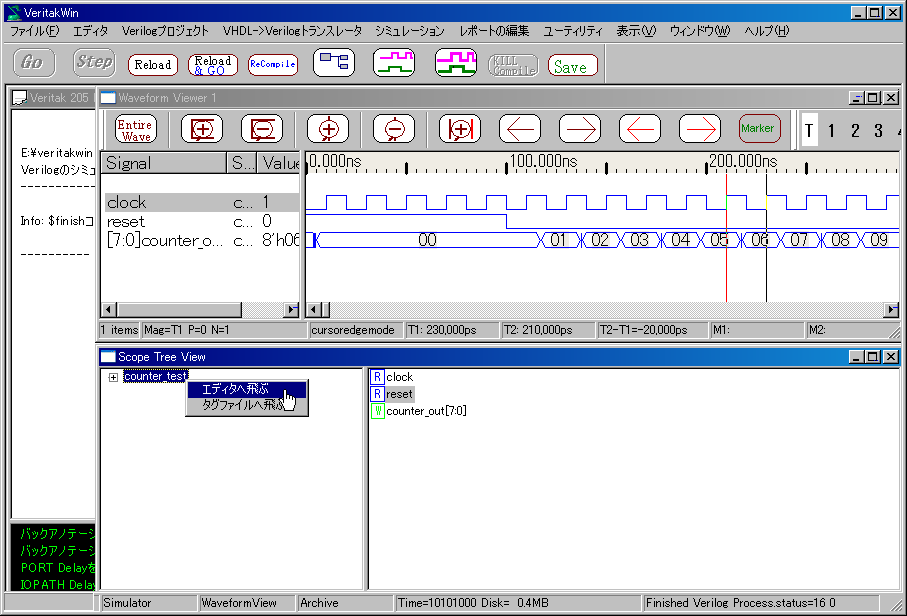

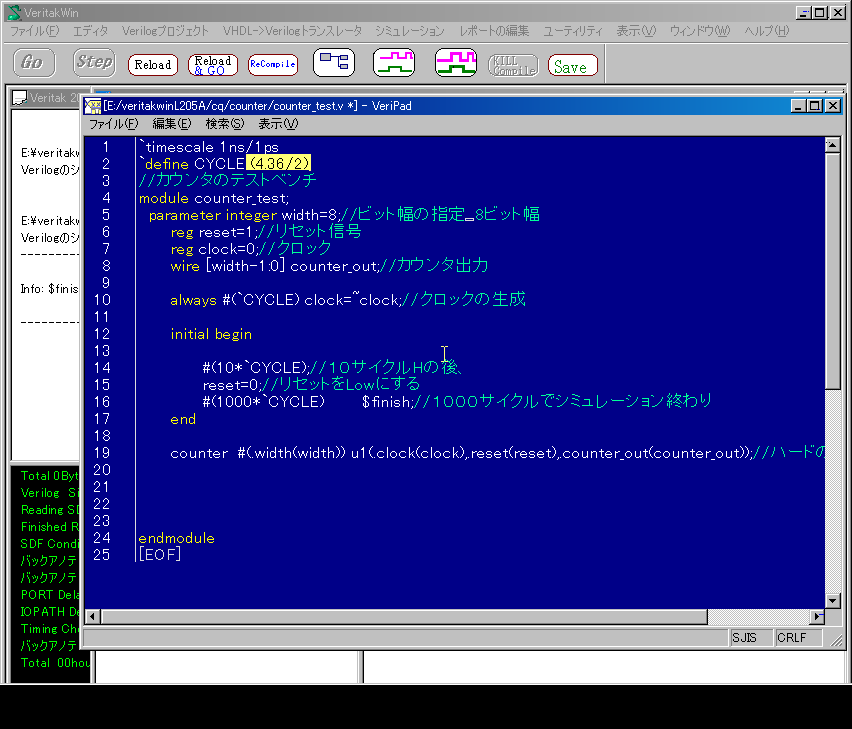

トップ階層のベンチへ行きたいので、

CYCLE を最大駆動周波数を超えない周期に設定します。

確かに最大駆動周波数近くでも動いているようです。出力は、1サイクル(4.36ns)を超える遅延になっており約、7.6nsが観測されます。

全体を眺めた様子です。

それでは、最大駆動周波数を超えるとどうなるのでしょうか?

意図的に、次のような設定をしてみます。

すると、SETUPエラーがでてしまいました。SDFファイルには、フリップフロップのセットアップやホールドタイムの情報が書かれています。

その値を満足しないときは、エラーとして出力されます。

なお、電源投入時、すなわち時間0付近の数ns間は、シミュレータ内部の初期化の過渡状態にあり、擬似的にSDF エラーメッセージが

出ることがあります。その場合は、無視してください。