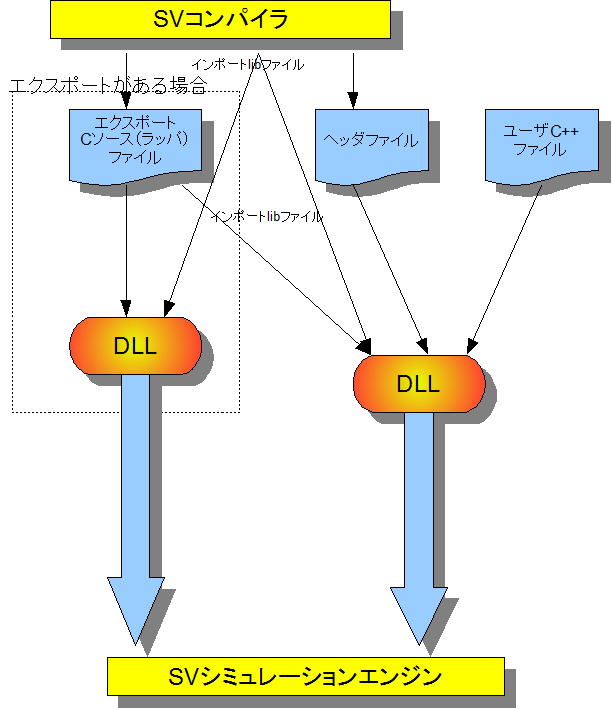

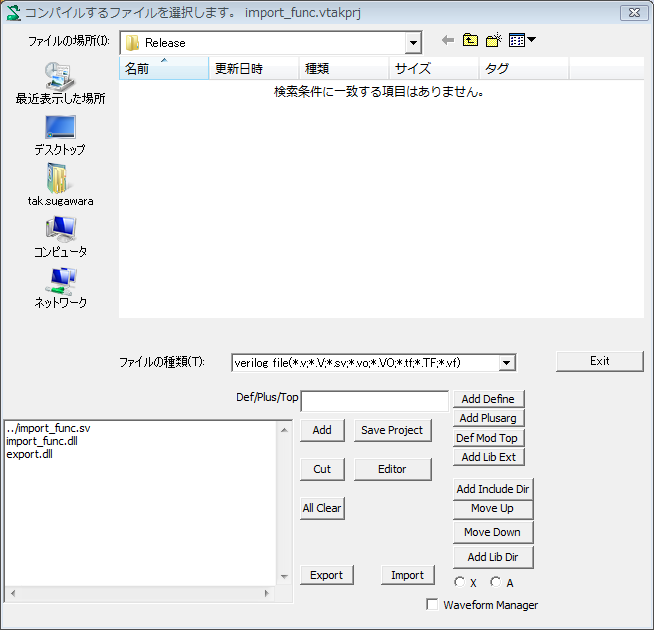

VeritakSV DPI-C/DPI-SC Tutorial 1.DPI-Cコンパイル、リンク手順 1.1 フロー 1.2 サンプル 1.2.1 完成後のVeritakプロジェクト

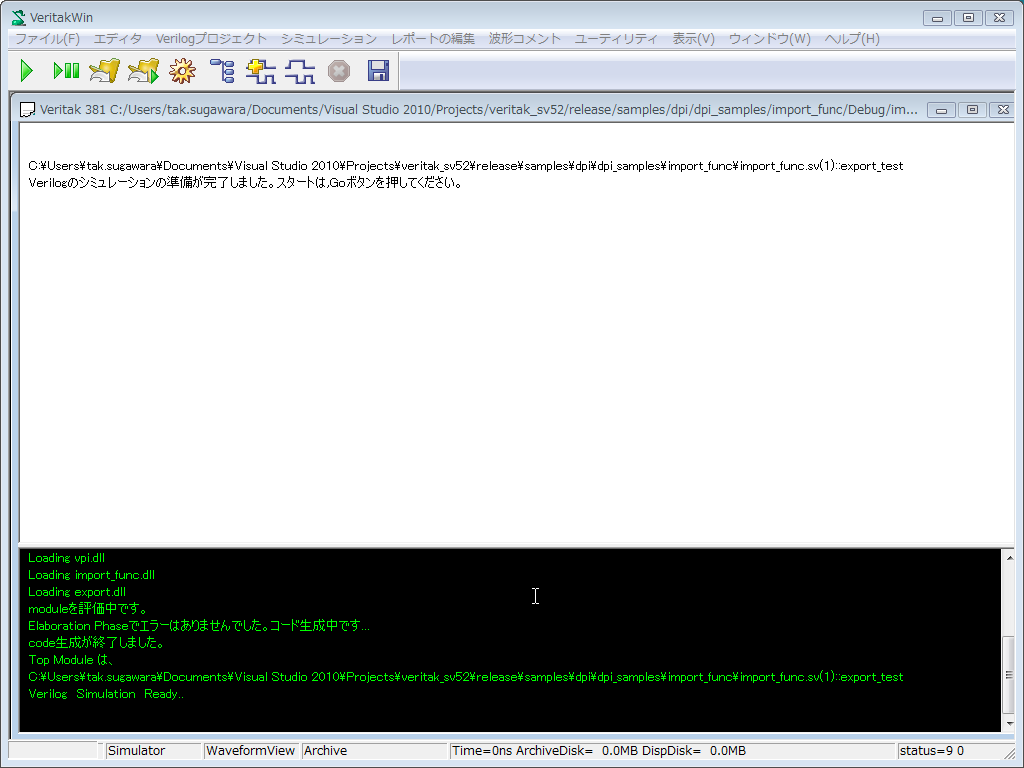

C:\Users\tak.sugawara\Documents\Visual Studio 2010\Projects\veritak_sv52\release\samples\dpi\dpi_samples\import_func\import_func.sv(1)::export_test

Verilogのシミュレーションの準備が完了しました。スタートは,Goボタンを押してください。

***** Veritak SV Engine Version 0.34 Build Jun.4.2010 *****

私は、C のimport_func()です。

私は sv_inc 関数です。

私はCです。 sv_incを呼び出した結果=101が返ってきました 。

vpi_printf:私は、C のimport_func()です 。

私は sv_inc 関数です。

vpi_printf:私はCです。 sv_incを呼び出した結果=101が返ってきました 。

---------- シミュレーションを終了します。time=0ns

**** Test Done. Total 1.00[msec] ****

となります。

module export_test;

import "DPI-C" context function void import_func () ; //Exportするにはimportが必要

export "DPI-C" function sv_inc; //Export宣言では、ファンクション名・タスク名しか書かない

function int sv_inc( int i1) ; //Cから呼ばれるExportファンクション

$display ( "私は sv_inc 関数です。" ) ;

return i1+ 1 ;

endfunction

initial

import_func() ; //Cのインポートファンクションを呼ぶ

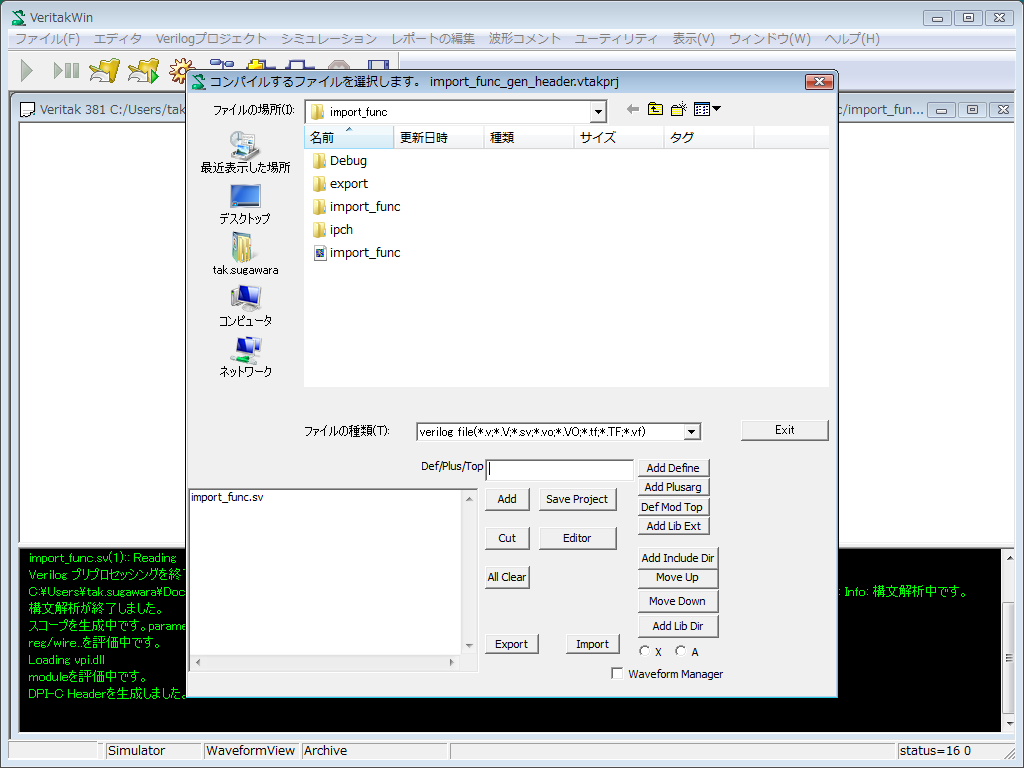

endmodule です。1.2.2 DLLの生成 1.2.2.1 C Headerファイルの生成 DPI-IF Generate C Header

dpi_veritak_export.h

/* Copyright 2010 www.sugawara-systems.com

* Note:

* This file is automatically generated.

* Please do not edit this file - you will lose your edits.*/

#ifndef INCLUDED_DPIHEADER

#define INCLUDED_DPIHEADER

#ifdef __cplusplus

#define DPI_LINK_DECL extern "C"

#else #define DPI_LINK_DECL

#endif

#include "svdpi.h"

DPI_LINK_DECL DPI_DLLESPEC

void import_func() ;

DPI_LINK_DECL DPI_DLLISPEC

int sv_inc( int ) ;

#endif

dpi_veritak_c_export.c

/* Copyright 2010 www.sugawara-systems.com

* Note:

* This file is automatically generated.

* Please do not edit this file - you will lose your edits.*/

#ifndef INCLUDED_DPIHEADER

#define INCLUDED_DPIHEADER

#ifdef __cplusplus

#define DPI_LINK_DECL extern "C"

#else #define DPI_LINK_DECL

#endif

#include "svdpi.h"

DPI_LINK_DECL DPI_DLLESPEC

int sv_inc( int i1)

{

}

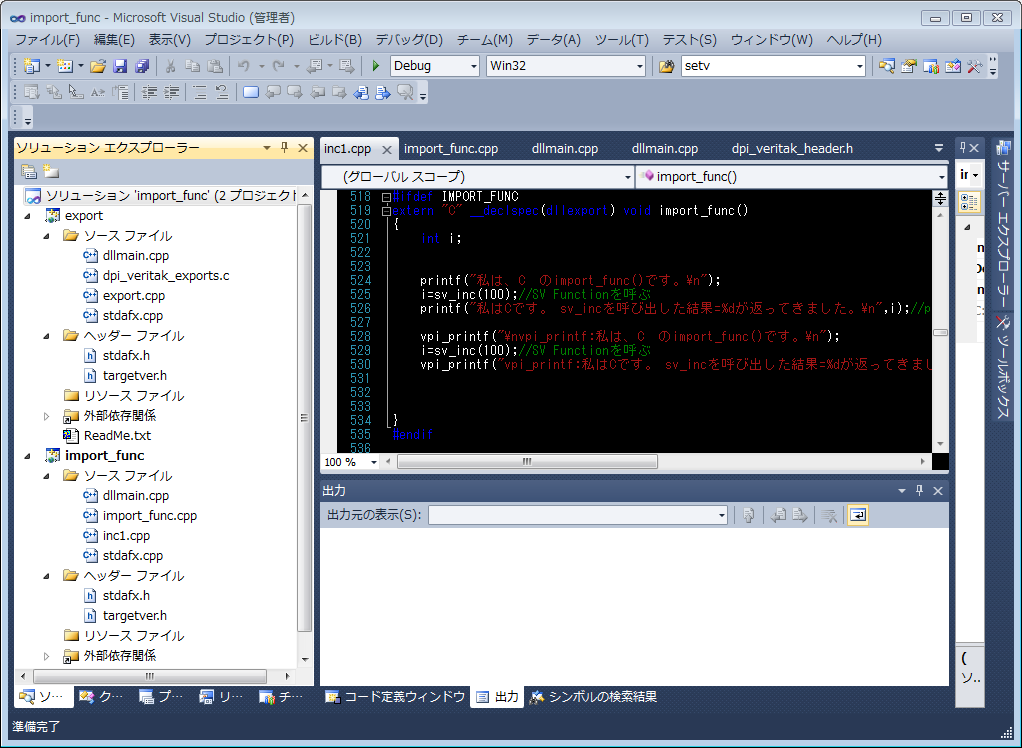

1.2.2.2 エクスポートファイルのコンパイル - export.dllの生成 Express版 でも機能、性能に制約/違いはありません。

samples\dpi\dpi_samples\import_func\Debug

C/C++ ->追加のインクルードディレクトリ

C/C++ ->プリコンパイル済みヘッダー

全般 ->文字セット

テクニカルノートcの関数の中身が空でwarning が出ていますが無視してください。この関数は、VeritakSVでは、単なるWrapperとして使っています。次のプロジェクトでは、

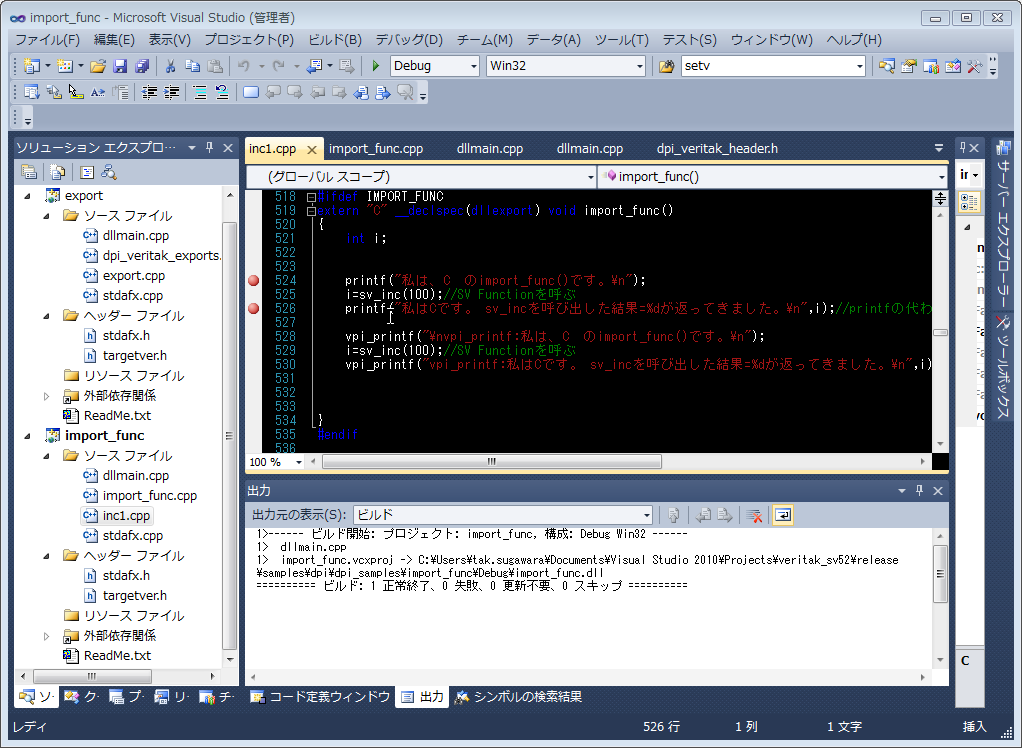

1.2.2.3 インポートファイルのコンパイル - import_func.dllの生成

samples\dpi\dpi_samples\import_func\Debug

C/C++ ->追加のインクルードディレクトリ

C/C++ ->プリコンパイル済みヘッダー

C/C++ -> プリプロセッサの定義

全般 ->文字セット

リンカー -> 入力 -> 追加の依存ファイル

特に、リンカーで、上で生成したexport.lib とライブラリフォルダにあるveritak_sv.lib

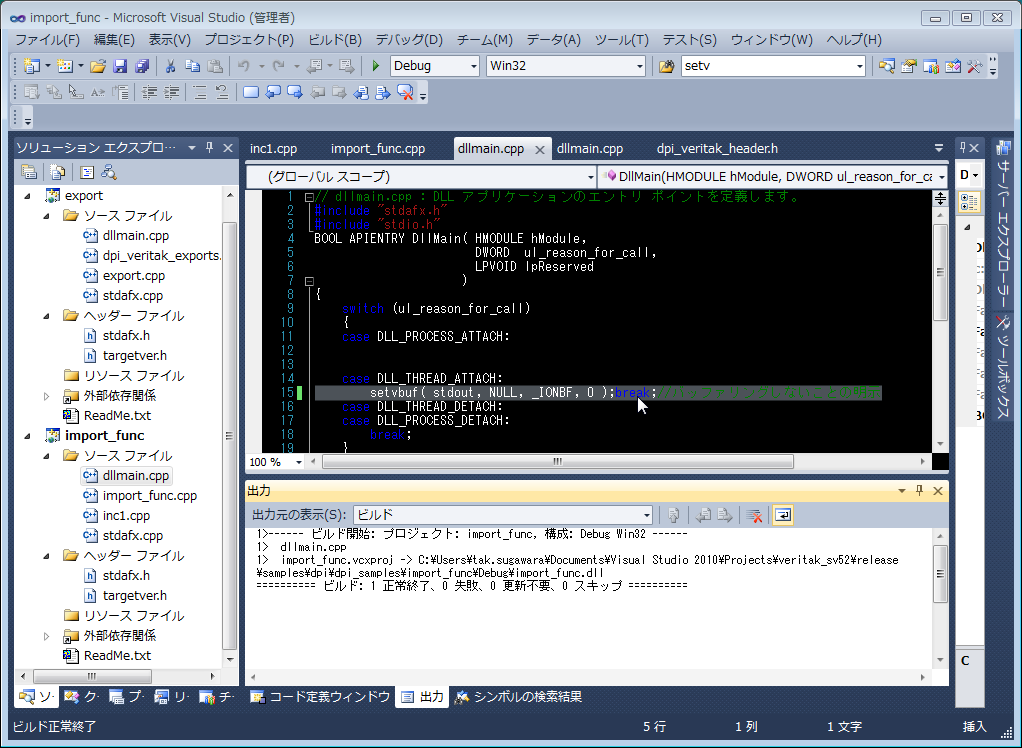

を追加することにご注意ください。バッファリングの問題について DPI-IF No Buffer 基本的には、上のようにすればよいのですが、大量にテキストを吐く場合には、バッファリングなしだと遅くなってしまいます。その場合には、上の対策は実行せずにprintfの代わりに、VPI系の構文

vpi_printf を呼び出します。vpi_printfと $displayは、結局のところ、同じC−RUNTIMEを呼び出すので、バッファリング付きでも問題なく実行できます 。 2 DPI-Cのデバッグ

2.1プロジェクトのロード

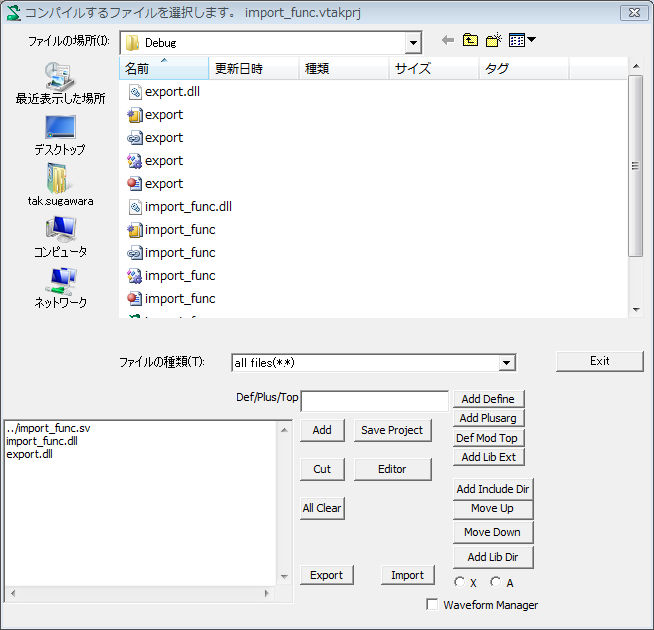

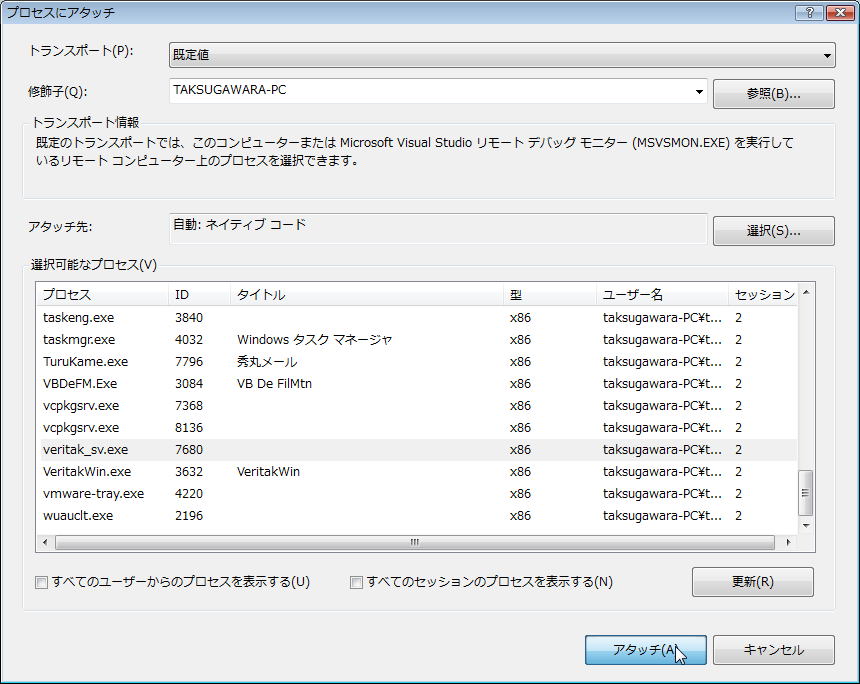

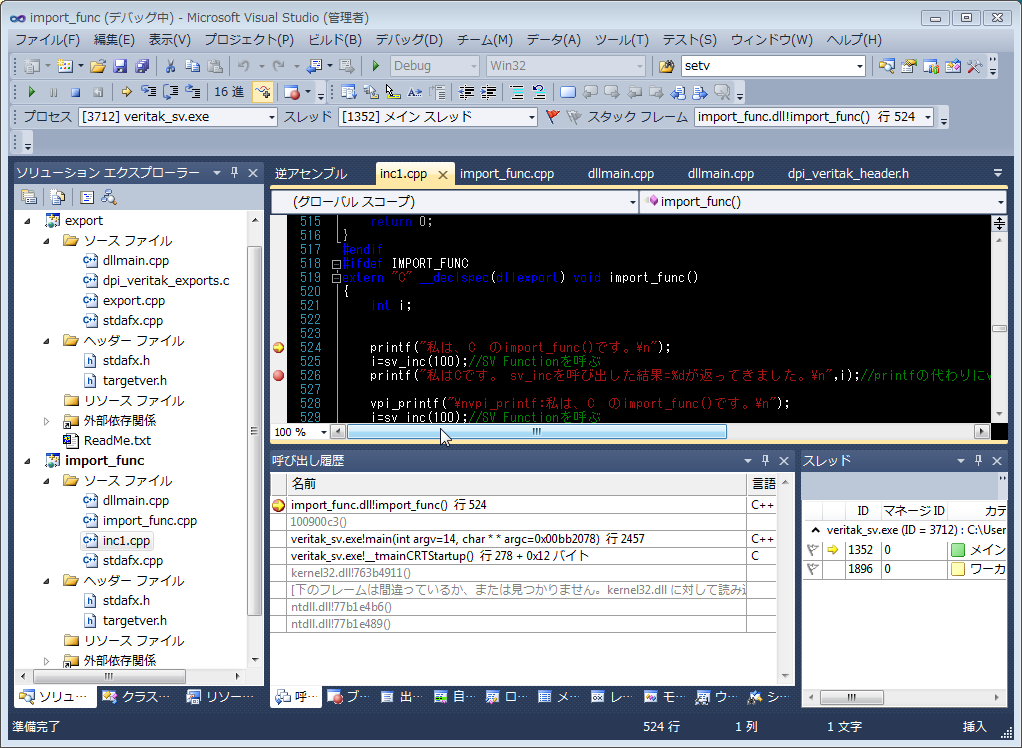

samples\dpi\dpi_samples\import_func\Debug\import_func.vtakprj2.2ブレークポイントの設定 2.3デバッガのアタッチ デバッグ ー>プロセスにアタッチ を押します。アタッチ を押します。2.4 Goボタン F5 キーを押すと実行が再開し次のブレークポイントで止まります。さらに押すとシミュレータに制御が戻り最後まで実行します。デバッガは一つしかアタッチできない

シングル行実行

ブレークポイント設定

ツールチップによる現在値の確認

を行うことができますが、これもVeritakSV搭載のプロセスデバッガによるものです。VisualStudioと同じような原理で動作するデバッガです。この手のデバッガは、アタッチした後でも、速度の低下は殆どないという利点がある反面、アタッチできるデバッガは、一つという制限があります。つまり、HDLソース上でブレークポイントを置きつつ、DPI-Cのコードデバッグを行うことが(今のところVeritakSVα0.35現在)できません。シミュレーション ー>デタッチ

3.SystemCのシミュレーション

VeritakSVでは、SystemCシミュレーションカーネルを統合しており、SystemCのシミュレーションをすることができます。また、OSCIシミュレータのセマンティクスを維持しており、SVとの通信がなければ、全く同じ挙動になります。 次のようなシミュレーションが可能です。

SystemC単独

VerilogHDL単独

VerilogHDLからSystemCのインスタンス化

SystemCからVerilogHDLのインスタンス化

1-4の組み合わせ

DPI-SC

3.0.1 統合カーネルのスケジューラ

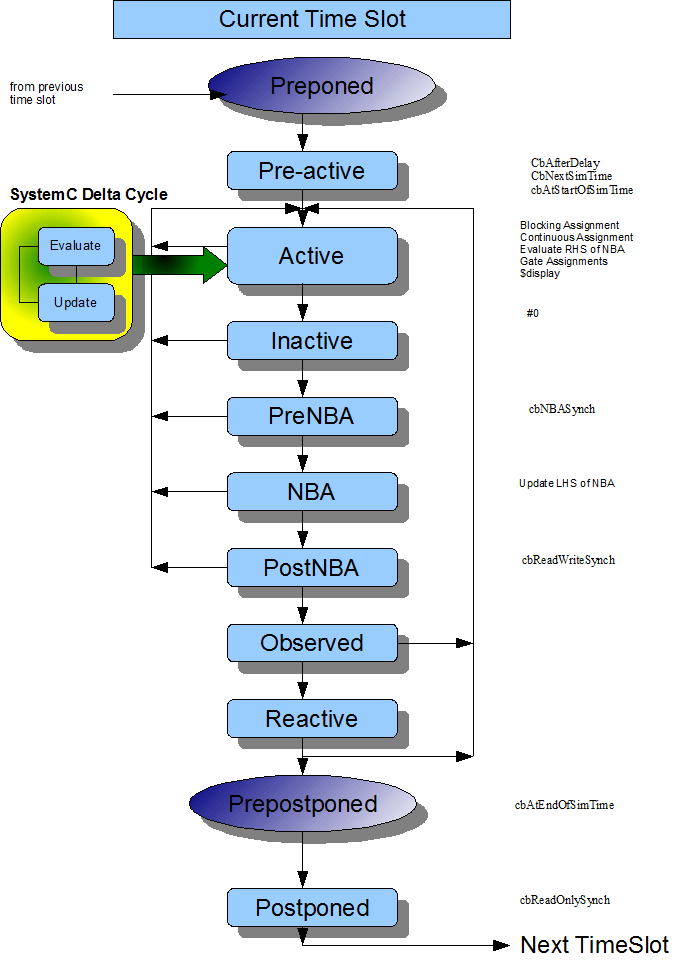

一方、SystemVerilogの1タイムスロットは、下のように領域に分けられます。SystemVerilogがなぜこのような複雑な状態遷移を持つのかは、歴史的な経緯もあり触れません。各領域(region)の意味については、以下のサンーバースト社の論文(英文)が詳しいです。http://www.sunburst-design.com/papers/CummingsSNUG2006Boston_SystemVerilog_Events.pdf 3.0.2 VerilogHDLとSystemCのシミュレーションの仕組み

SC_METHODは、 wait()が記述できない

SC_THREADでは、最低一つのwait()が必要

SC_METHODからSC_THREADを呼ぶことはできない

....

は、VerilogHDLのルール

functionでは、イベント(wait や、@ )やDelay構文を書けない

always プロセス中には、最低一つのイベントもしくはDelay構文を置かなければいけない

functionから、task を呼べない

.. と、なんだか似たところがあります。実際、どちらもイベントドリブンのシミュレーション言語で、

の二つのソフトウェア要素から成ります。言語間で呼び名は、違ってもソフトウェアの視点からは同じものです。

SystemC

VerilogHDL

記憶

C関数

SC_METHOD

function

記憶を持たない

スレッド

SC_THREAD

task

イベント構文で、スレッドを抜ける。イベントトリガによりイベント構文の次にある文の実行に戻る。

3.0.2.1 C関数は組み合わせ回路 3.0.2.2 順序回路は、スレッド 3.1 SystemC単独のシミュレーション

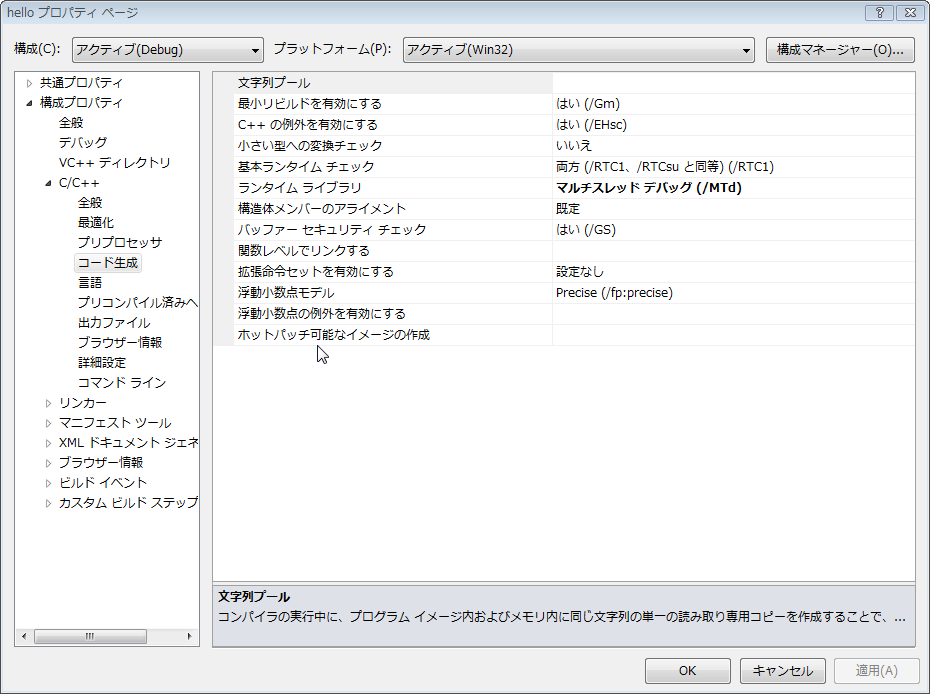

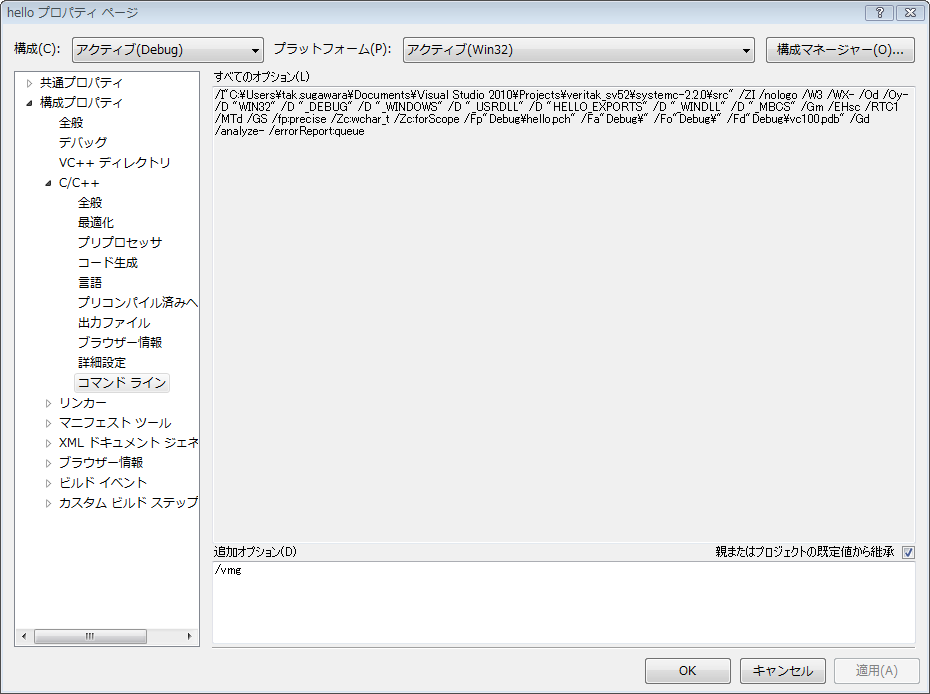

3.1.1Visual C++の設定

以下の設定に注意します。

3.1.1.1 Cランタイムライブラリは"マルチスレッドDLL"ではなく、STATICライブラリであるマルチスレッド (デバッグ)を使う

添付しているSystemC.lib は、スタティックライブラリです。そのために同じスタティック系のライブラリを使用してください。

3.1.1.2 vmg を下のように追加する

その他の設定

文字セット マルチバイト

プロコンパイルヘッダー 使用しない

追加のインクルードディレクトリ

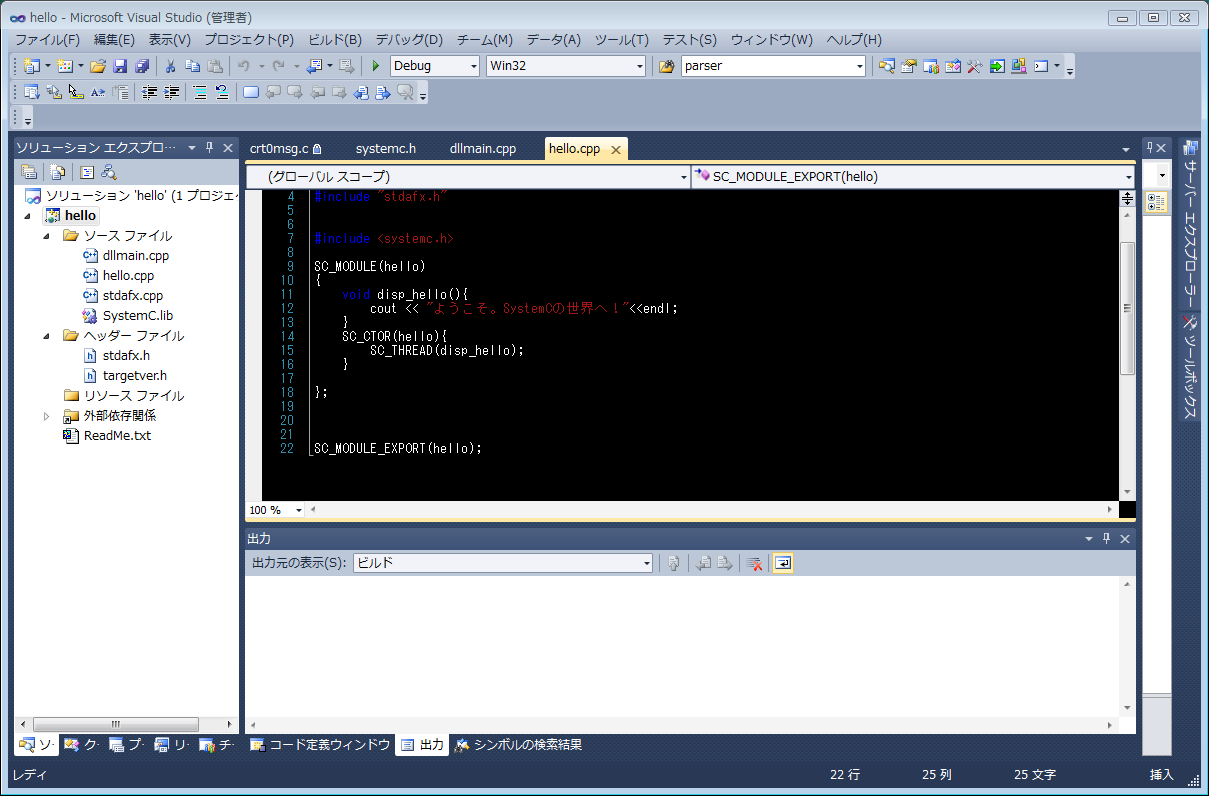

を行います。3.1.2 systemc ソース形式 SC_MODULE_EXPORT SC_MODULE_EXPORT

#include <systemc.h>

SC_MODULE ( hello){

void disp_hello(){

cout << "ようこそ。SystemCの世界へ!" << endl;

}

SC_CTOR ( hello){

SC_THREAD ( disp_hello) ;

}

} ;

SC_MODULE_EXPORT ( hello) ;

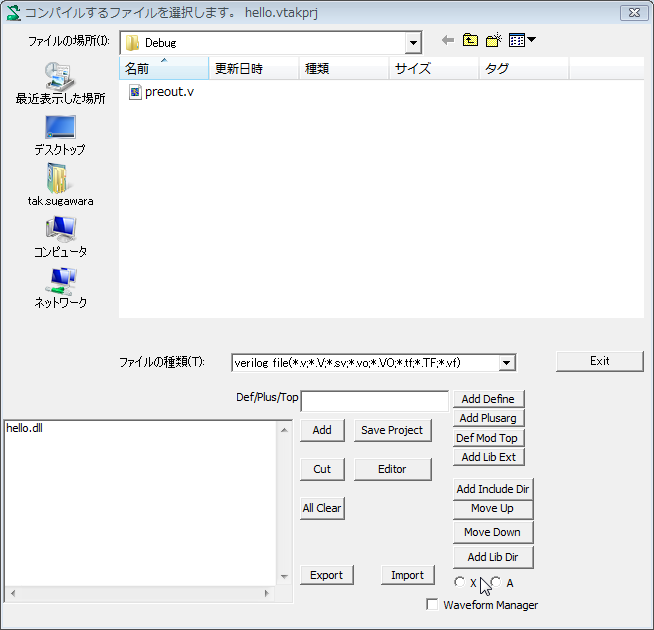

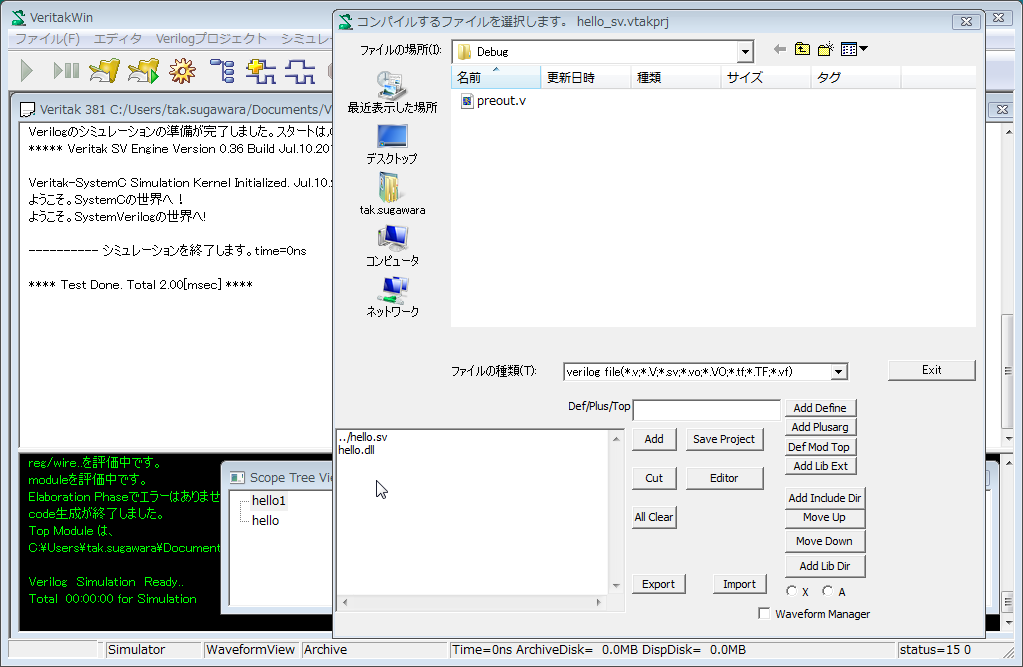

3.1.3 ビルド 3.1.4 Veritak プロジェクト 3.1.5 RUN

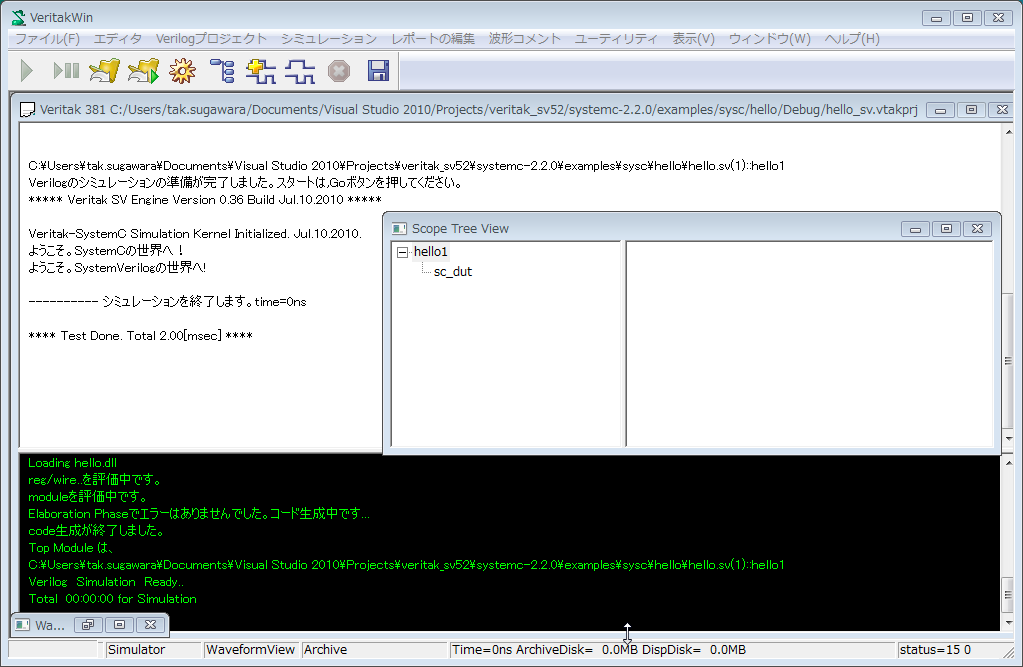

結果です。

***** Veritak SV Engine Version 0.36 Build Jul.10.2010 *****

Veritak-SystemC Simulation Kernel Initialized. Jul.10.2010.

ようこそ。SystemCの世界へ!

---------- シミュレーションを終了します。time=0ns

**** Test Done. Total 0.00[msec] ****

3.2 SystemCとVerilog HDLの並列シミュレーション

次のソースをhello.sv としてプロジェクトに追加します。

module hello1;

initial $display( "ようこそ。SystemVerilogの世界へ!" ) ;

endmodule

3.3 SystemCのインスタンス化 3.3.1 ポートを持たないSystemCモジュールのインスタンス化

module hello1;

initial $display( "ようこそ。SystemVerilogの世界へ!" ) ;

hello sc_dut() ; //SystemC モジュールhelloのインスタンス化

endmodule ;

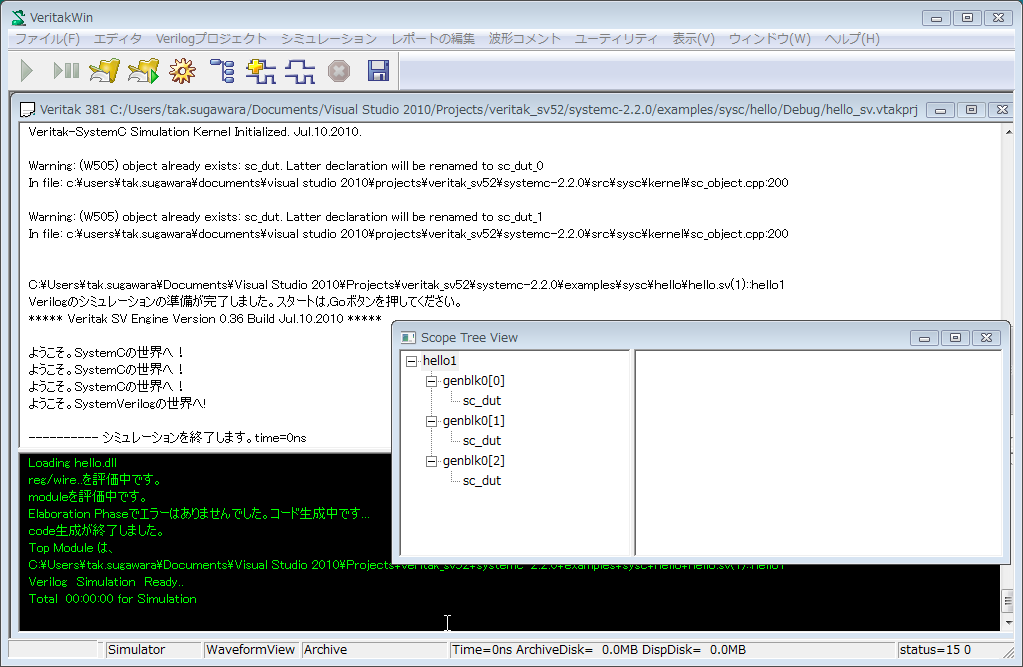

generateによるsystemc モジュールのインスタンス化

module hello1;

initial $display( "ようこそ。SystemVerilogの世界へ!" ) ;

for ( genvar g1= 0 ; g1< 3 ; g1++ )

hello sc_dut() ; //systemc モジュールのインスタンス化

endmodule ;

module hello1;

initial $display( "ようこそ。SystemVerilogの世界へ!" ) ;

reg [ 13 : 0 ] a;

wire [ 7 : 0 ] out;

hello dut( .in1( a) , .out1( out)) ; //SystemC Moduleのインスタンス化 名前結合で接続

always @ ( out) begin //SystemCからの信号をセンスする

$display( " Veriloag Reading : out=%d time=%t" , out, $time) ;

end

initial begin

$timeformat( - 9 , 3 , "ns" , 8 ) ;

a= 0 ;

repeat ( 4 ) begin

a= a+ 1 ;

$display( "Verilog Writing: a=%3d sv time=%t" , a, $time)

;# 1 ;

end

end

endmodule

SC_MODULE ( hello

){

sc_in < sc_int < 8 >> in1; //Verilog HDLに接続するポート

sc_out < sc_int < 8 >> out1; //Verilog HDLに接続するポート

SC_CTOR ( hello) : //コンストラクタ

in1( "in1" ) ,out1( "out1" ) //接続するVerilogポート名と同じにする

{

SC_THREAD ( disp_hello) ;

SC_METHOD ( disp_in1) ;

sensitive << in1;

}

void disp_in1(){ //in1をセンス

cout << "--------------------------------- SystemC reading: :in1=" << in1.read () << " sc time=" << sc_time_stamp() << endl;

}

void disp_hello(){

wait ( 1000 ,SC_NS ) ;

out1.write ( 0 ) ;

wait ( 1 ,SC_PS ) ;

cout << "--------------------------------- SystemC Wriing : out1=" << out1.read () << " sc_time=" << sc_time_stamp() << endl;

for ( int i= 0 ; i< 5 ; i++ ){

wait ( 100 ,SC_NS ) ;

out1.write ( out1.read () + 1 ) ;

wait ( 1 ,SC_PS ) ;

cout << "-------------------------------- SystemC Wriing : out1=" << out1.read () << " sc_time=" << sc_time_stamp() << endl;

}

cout << "---------------------------------- ようこそ。SystemCの世界へ!" << endl;

}

} ;

SC_MODULE_EXPORT ( hello) ;

結果です。左側が Verilogモジュール側の出力、右側が SystemCモジュールからの出力です。

C:\Users\tak.sugawara\Documents\Visual Studio 2010\Projects\veritak_sv52\systemc-2.2.0\examples\sysc\hello\systemc_instance.sv(1)::hello1

Verilogのシミュレーションの準備が完了しました。スタートは,Goボタンを押してください。

***** Veritak SV Engine Version 0.36 Build Jul.10.2010 *****

--------------------------------- SystemC reading: :in1=0 sc time=0 sec

ようこそ。SystemVerilogの世界へ!

Verilog Writing: a= 1 sv time= 0.000ns

--------------------------------- SystemC reading: :in1=1 sc time=0 sec

Verilog Writing: a= 2 sv time= 1.000ns

--------------------------------- SystemC reading: :in1=2 sc time=1 ns

Verilog Writing: a= 3 sv time= 2.000ns

--------------------------------- SystemC reading: :in1=3 sc time=2 ns

Verilog Writing: a= 4 sv time= 3.000ns

--------------------------------- SystemC reading: :in1=4 sc time=3 ns

--------------------------------- SystemC Wriing : out1=0 sc_time=1000001 ps

Veriloag Reading : out= 1 time=1100.001ns

-------------------------------- SystemC Wriing : out1=1 sc_time=1100002 ps

Veriloag Reading : out= 2 time=1200.002ns

-------------------------------- SystemC Wriing : out1=2 sc_time=1200003 ps

Veriloag Reading : out= 3 time=1300.003ns

-------------------------------- SystemC Wriing : out1=3 sc_time=1300004 ps

Veriloag Reading : out= 4 time=1400.004ns

-------------------------------- SystemC Wriing : out1=4 sc_time=1400005 ps

Veriloag Reading : out= 5 time=1500.005ns

-------------------------------- SystemC Wriing : out1=5 sc_time=1500006 ps

---------------------------------- ようこそ。SystemCの世界へ!

---------- シミュレーションを終了します。time=1500006ps

**** Test Done. Total 4.00[msec] ****

3.4 Verilog モジュールのインスタンス化と接続

module counter16( input clk, input enable, output bit [ 3 : 0 ] counter) ;

always @ ( negedge clk) begin

if ( ! enable) counter<= 0 ;

else counter <= counter+ 1 ;

end

endmodule

上のモジュールをインスタンス化するには、下のようなSystemCの階層でラッパモジュールが必要になります。VerilogHDL側のモジュール名、ポート名をそのまま

#include <systemc.h>

class counter16 : public sc_core:: sc_module

{

public :

sc_in < bool > clk,enable; //verilog ポート方向に合わせる

sc_out < sc_uint < 4 >> counter; //verilog ポート方向に合わせる

counter16 ( sc_module_name nm) :

sc_core:: sc_module ( nm,"counter16" ) , //Verilog HDL側のモジュール名として参照される

clk( "clk" ) ,enable( "enable" ) ,counter( "counter" )//Verilog HDL側のポート名に合わせる

{

}

} ;

このラッパーモジュールを制御するSystemCテストベンチが下の記述です。 このテストベンチは、上のcounter16モジュールをインスタンス化しています。enable

端子を制御しています。

SC_MODULE ( test_bench

){

counter16 dut;

sc_signal < sc_uint < 4 >> counter; //モニタ用

sc_clock clock ; //テストベンチクロック源

sc_signal < bool > enable; //制御信号

SC_CTOR ( test_bench) :

dut( "counter16" ) ,

clock ( "clock" ,10 ,SC_NS ,0.5 ,1 ,SC_NS ,true )//レースを防ぐために1ns後に発振開始 Duty 50% 10ns サイクル Pos

{

dut.clk ( clock ) ;

dut.counter ( counter) ;

dut.enable ( enable) ;

SC_THREAD ( enable_control) ;

SC_METHOD ( disp_counter) ;

sensitive << counter;

}

void enable_control(){

wait ( 1000 ,SC_NS ) ;

cout << "イネーブル端子をアサートしました。time=" << sc_time_stamp() << endl;

enable.write ( true ) ;

}

void disp_counter(){ //モニタ

cout << "counter=" << counter.read () << " time=" << sc_time_stamp() << endl;

}

} ;

SC_MODULE_EXPORT ( test_bench) ;

全体の記述を通して、トップ階層は、test_benchになります。SC_MODULE_EXPORTでsystemc側のトップ階層を指示しています。

***** Veritak SV Engine Version 0.36 Build Jul.10.2010 *****

counter=0 time=0 sec

イネーブル端子をアサートしました。time=1 us

counter=1 time=1006 ns

counter=2 time=1016 ns

counter=3 time=1026 ns

counter=4 time=1036 ns

counter=5 time=1046 ns

counter=6 time=1056 ns

counter=7 time=1066 ns

counter=8 time=1076 ns

counter=9 time=1086 ns

counter=10 time=1096 ns

counter=11 time=1106 ns

counter=12 time=1116 ns

counter=13 time=1126 ns

counter=14 time=1136 ns

counter=15 time=1146 ns

counter=0 time=1156 ns

...

このように、Verilogのテストベンチをsystemcで記述することができます。3.5 DPI-SC systemcとverilog HDL間の通信 3.5.1 ビルドの手順

SVソースの作成

1に対して、veritakプロジェクトを作成し、Cヘッダ/ソースファイルの生成する

2のソースのDLL化 (exportプロジェクトのビルド)

systemc ユーザプロジェクトのDLL化(下の例ではdpi_sc_test)

SVソースとDLLをVeritakプロジェクトに入れてRun

SVソースです。systemcのスレッドから呼び出されるtaskのみ"DPI-SC"

で宣言します。書法はDPI-Cに同じです。

module dpi_sc_dut;

export "DPI-SC" context task wait_task;

import "DPI-C" function void get_data_fm_systemc( inoutint ) ;

reg clock= 0 ;

always # 10 clock=~ clock;

task wait_task( input int nclks) ;

int data ;

$display( "\t\t\t\t\t\t SV task に入りました。 nclks=%3d 時刻:%t" , nclks, $realtime) ;

repeat ( nclks) begin

@ ( posedge clock) ;

get_data( data ) ;

end

# 1 ;

$display( "\t\t\t\t\t\t SV task を終了します。 時刻:%t" , $realtime) ;

endtask

function void get_data( inout int data ) ;

$display( "\t\t\t\t\t\t DPI-Cを使ってSystemCクラス内データを取得します。時刻:%t" , $realtime) ;

get_data_fm_systemc( data ) ;

$display( "\t\t\t\t\t\t 取得したSystemCクラスメンバーデータは%3dです。時刻:%t" , data , $realtime) ;

endfunction

initialbegin

$timeformat( - 9 , 3 , "ns" , 8 ) ;

$display( "\t\t\t\t\t\t SystemVerilogの世界へようこそ!" ) ;

# 1000 $finish;

end

endmodule

SystemC ソースです。

#include <systemc.h>

#include "dpi_veritak_header.h"

struct hello;

static hello* hello_ptr= 0 ;

void register_instance( hello* h ){ hello_ptr= h; }

hello* get_instance (){ return hello_ptr; }

SC_MODULE ( hello

){

int my_data;

void get_data_fm_systemc( int * data_ptr ){

cout << "SystemCメンバー関数が呼び出されました。" << endl;

cout << "my_data " << my_data<< "をセットします。" << endl;

* data_ptr= my_data++ ;

}

void disp_hello(){

cout << "ようこそ。SystemCの世界へ!" << endl;

wait ( 100 ,SC_NS ) ;

cout << "Systemc time=" << sc_time_stamp() << " DPI-SCを使って" << endl;

cout << "SystemVerilogの時間消費タスクを呼び出します。" << endl;

wait_task( 3 ) ; //DPI-SC export task

cout << "Systemc time=" << sc_time_stamp() << " DPI-SCを使って" << endl;

cout << "SystemVerilogタスクから戻りました。" << endl;

}

SC_CTOR ( hello){ //コンストラクタ

SC_THREAD ( disp_hello) ; //スレッド

register_instance( this ) ; //クラスオブジェクトをDPI-Cで接続する

my_data= 100 ;

}

} ;

SC_MODULE_EXPORT ( hello) ;

DPI_LINK_DECL DPI_DLLESPEC void get_data_fm_systemc( int * data ){

get_instance() - > get_data_fm_systemc( data) ;

}

Verilogのシミュレーションの準備が完了しました。スタートは,Goボタンを押してください。

***** Veritak SV Engine Version 0.36 Build Jul.10.2010 *****

Veritak-SystemC Simulation Kernel Initialized. Jul.10.2010.

ようこそ。SystemCの世界へ!

SystemVerilogの世界へようこそ!

Systemc time=100 ns DPI-SCを使って

SystemVerilogの時間消費タスクを呼び出します。

SV task に入りました。 nclks= 3 時刻: 100.000ns

DPI-Cを使ってSystemCクラス内データを取得します。時刻: 110.000ns

SystemCメンバー関数が呼び出されました。

my_data 100をセットします。

取得したSystemCクラスメンバーデータは100です。時刻: 110.000ns

DPI-Cを使ってSystemCクラス内データを取得します。時刻: 130.000ns

SystemCメンバー関数が呼び出されました。

my_data 101をセットします。

取得したSystemCクラスメンバーデータは101です。時刻: 130.000ns

DPI-Cを使ってSystemCクラス内データを取得します。時刻: 150.000ns

SystemCメンバー関数が呼び出されました。

my_data 102をセットします。

取得したSystemCクラスメンバーデータは102です。時刻: 150.000ns

SV task を終了します。 時刻: 151.000ns

Systemc time=151 ns DPI-SCを使って

SystemVerilogタスクから戻りました。

Info: $finishコマンドを実行します。time=1000000ps

**** Test Done. Total 3.00[msec] ****