僾儘僌儔儉丂(program)

奣梫

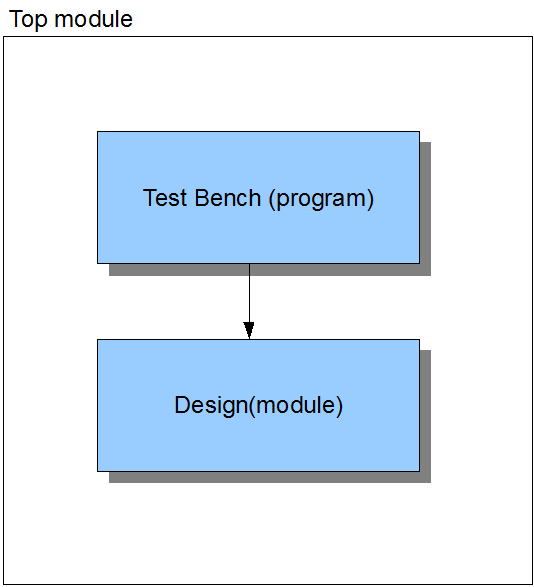

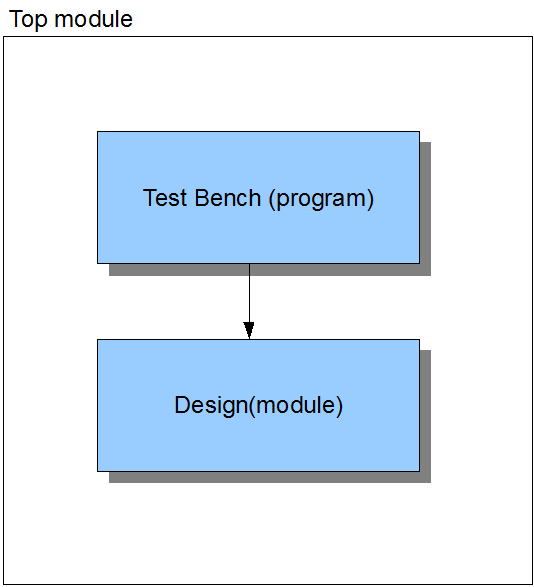

module 偼丄婎杮揑側價儖僨傿儞僌僽儘僢僋偱偁傝丄偦偙偵僥僗僩儀儞僠偲僴乕僪僂僃傾偺婰弎偑崿嵼偟偨偺偑廬棃偺婰弎僗僞僀儖偱偟偨丅

SV偱偼丄module偼丄僴乕僪僂僃傾偺婰弎偵巊偄丄僥僗僩儀儞僠偼丄program 偱婰弎偡傞偲偄偆偺偑丄悇彠偝傟傞婰弎僗僞僀儖偵側傝傑偡丅

廬棃捠傝丄僥僗僩儀儞僠傕module撪偵僥僗僩儀儞僠傪婰弎偡傞僗僞僀儖傕壜擻偱偡偑丄program偺巊梡偱偼丄埲壓偺儊儕僢僩偑偁傝傑偡丅

- 僥僗僩儀儞僠偲僨僓僀儞偺暘棧

- 壜撉惈偺岦忋

- 僥僗僩儀儞僠娫乕僨僓僀儞娫偑儗乕僗僼儕乕

丂揟宆揑側丂峔憿偼丄Top丂module偺壓偵 test bech偑偁傝丄僥僗僩偝傟傞僴乕僪僂僃傾乮Device丂Under丂Test乯偑偁傞偲偄偆宍偵側傝傑偡丅

program偼丄module傪僀儞僗僞儞僗壔偡傞偙偲偑偱偒側偄偺偱丄奒憌偺僩僢僾偼丄偙傟傑偱捠傝丄module偵側傝傑偡丅

僥僗僩儀儞僠娫乕僨僓僀儞娫偺儗乕僗僼儕乕

儗乕僗(race)偲偄偆偺偼丄幚峴弴彉偑僔儈儏儗乕僞娫丄偁傞偄偼丄摨偠僔儈儏儗乕僞偱傕丄僶乕僕儑儞/嵟揔壔偺桳柍摍偵傛傝丄幚峴弴彉偑曄傢偭偰偟傑偆傕偺偱偡丅丂嵟傕扨弮側椺偲偟偰偼丄

module test;

reg a,b;

initial

a = 0;

initial

b = a;

initial

begin

#1;

$display("Value a=%b Value of b=%b",a,b);

end

endmodule

偙偺椺偵偍偄偰丄b偺抣偼丄僔儈儏儗乕僞偱堘偆壜擻惈偑偁傝傑偡丅1'bx 傪昞帵偡傞傕偺傕偁傟偽丄1'b0偵側傞傕偺傕偁傝偳偪傜傕儕乕僈儖偱偡丅LRM偼丄module撪奜initial偺幚峴弴彉傪婯掕偟偰偄傑偣傫丅偙傟偵偮偄偰偼SV傕摨條偱偡丅

-verilogHDL偺巇條偑濨枂偲偄偆偙偲偱偁傝傑偣傫丅傑偨丄"僶僌偱偼側偔巇條偱偡"丄偲尵偭偨椶偺尵偄栿偱傕偁傝傑偣傫丅柧妋偵丄堄恾偟偰柍婯掕傪鎼偭偰偄傑偡丅幚偼丄verilog

HDL 僔儈儏儗乕僞偑崅懍側棟桼偑偙偙偵偁傝傑偡丅

SV偱堘偆偺偼丄怴愝偝傟偨program偲module娫偱丄幚峴弴彉偑妋掕揑偵側傞偙偲偱偡丅program(僥僗僩儀儞僠乯撪丄傑偨偼丄module(僨僓僀儞乯撪偺儗乕僗偼丄偙傟傑偱偲摨偠偔丄儗乕僗偑懚嵼偡傞壜擻惈偵偮偄偰偼丄曄傢傝傑偣傫丅

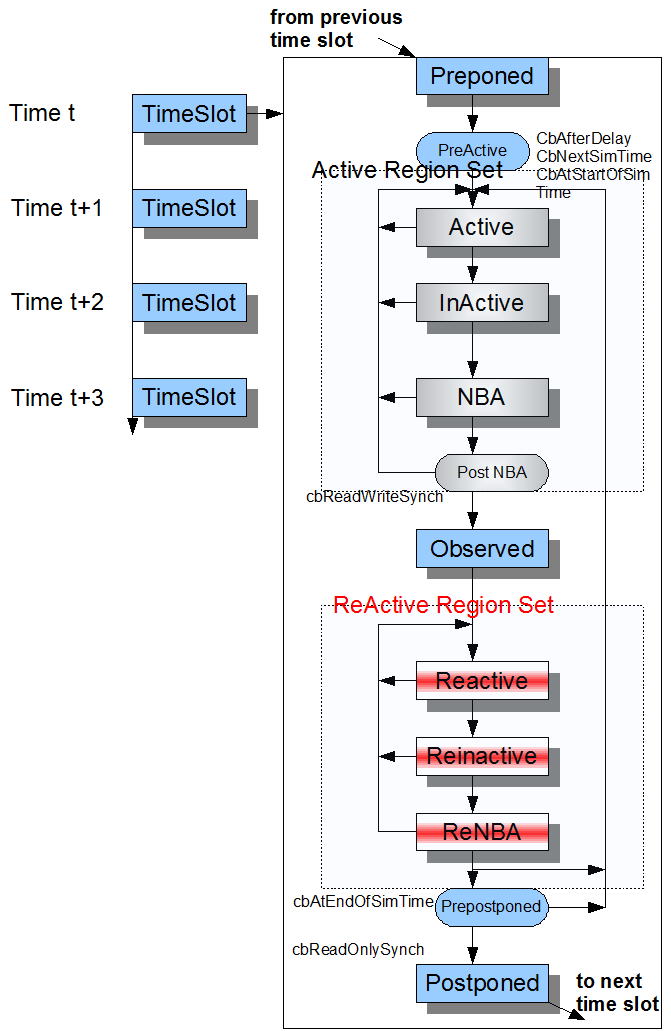

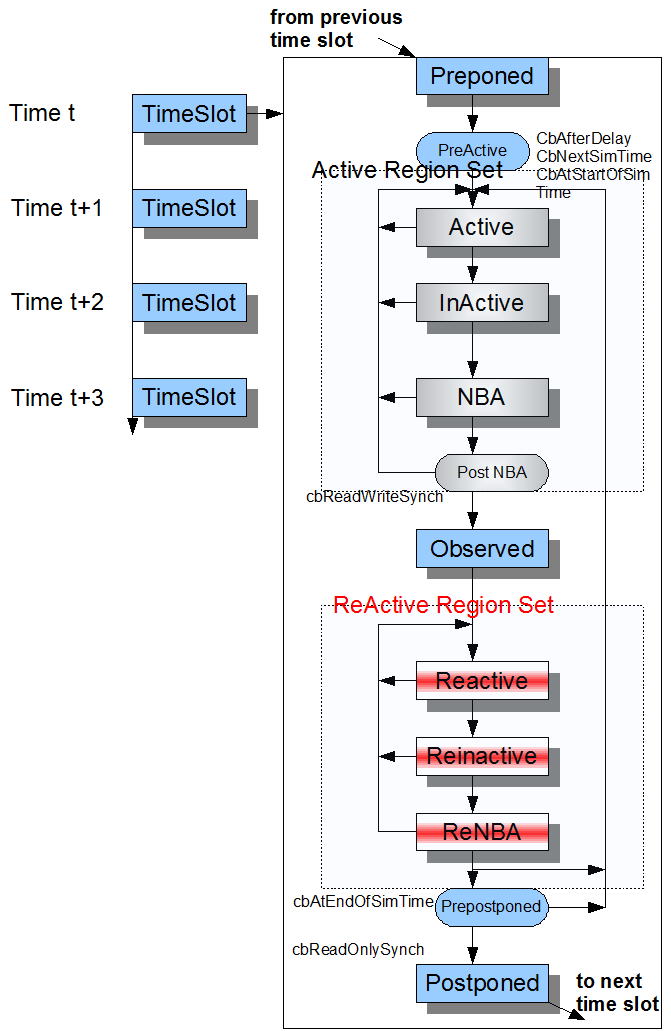

SV偺僞僀儉僗儘僢僩

壓偼丄僞僀儉僗儘僢僩偺奣擮恾偱偡丅奺帪崗偱偺僀儀儞僩偼丄帪崗偱僜乕僩偝傟奺帪崗偵懳偡傞僉儏乕傪帩偭偰偄傑偡丅奺帪崗偵偮偄偰偼丄偝傜偵丄僞僀儉僗儘僢僩偲屇偽傟傞丄僀儀儞僩僉儏乕偑偁傝傑偡丅SV偺LRM偱偼丄幚偵17傕偺幚峴僼僃乕僘(region)傪婯掕偟偰偄偰丄嵶偐偔摦嶌傗幚峴弴偑掕傔傜傟偰偄傑偡丅

-VeritakSV偵偍偄偰傕丄庒姳偺堘偄偼偁傞偺偱偡偑17region傪巊梡偟偰偄傑偡丅丂廬棃偼悢regions偟偐偁傝傑偣傫偱偟偨偺偱丄僷僼僅乕儅儞僗偵僸僢僩偡傞偺偼旔偗偑偨偄偺偱偡偑丄悢昐峴埲壓偺彫婯柾僜乕僗偱側偄尷傝栚棫偭偨曄壔偼側偄偲巚偄傑偡丅

埲壓偺恾偱丄ActiveRegionSet偲昤偐傟偨僌儗乕偺晹暘偑丄廬棃晹偱丄ReActiveRegionSet偲彂偐傟偨愒偄晹暘偑program梡偵怴偟偔捛壛偝傟偨晹暘偵側傝傑偡丅

儐乕僓偼丄偙偺恾傪徻嵶偵棟夝偡傞昁梫偼偁傝傑偣傫丅廬棃傕丄僽儘僢僉儞僌傾僒僀儞儊儞僩丒僲儞僽儘僢僉儞僌傾僒僀儞儊儞僩埵偟偐丄堘偄傪堄幆偡傞偙偲偼側偐偭偨偲巚偄傑偡丅偦傟傜偑丄program撪偱彂偄偨傕偺偲丄module撪偱彂偄偨傕偺偱偼丄暿僼僃乕僘偱幚峴偝傟傞埵偺堄枴偱懆偊偰偍偗偽傛偄偲巚偄傑偡丅

programa 偺僀儞僗僞儞僗壔

program偼丄儌僕儏乕儖偲摨條偵婰弎偡傞偙偲偑偱偒傑偡丅

program prog1;

initial $display("SV僾儘僌儔儉偺悽奅傊傛偆偙偦");

//always always_ff..偼丄晄壜

endprogram

偟偐偟丄program撪偵偼丄always 宯偺僾儘僙僗偼丄抲偔偙偲偑偱偒傑偣傫丅廬偄丄initial

偱僞僗僋傪惗惉偟側偑傜丄僥僗僩儀儞僠傪嶌傞偲偄偆偺偑丄婎杮揑側僗僞僀儖偵側傞偲巚偄傑偡丅

***** Veritak SV32 Engine Version 432 Build Dec 31 2012*****

SV僾儘僌儔儉偺悽奅傊傛偆偙偦

---------- 僔儈儏儗乕僔儑儞傪廔椆偟傑偡丅time=0ns

program偼丄module 偲摨條偵僀儞僗僞儞僗壔偡傞偙偲偑弌棃傑偡丅

program prog(input a);

reg b;

initial begin

b=a;

$display("program Value test.a=%b Value of b=%b",test.a,b);

end

endprogram

module mod(input a);

reg b;

initial begin

b=a;

$display("module test.a=%b Value of b=%b",test.a,b);

end

endmodule

module test;

reg a;

prog dut(a);

mod mut(a);

initial

a = 0;

endmodule

program-module娫偺幚峴弴彉

忋偱偼丄僀儞僗僞儞僗壔偟偨module偲program偲偱丄摨偠撪梕偺initial偑婰弎偝傟偰偄傑偡丅丂module懁偱偼丄忋偱愢柧偟偨捠傝丄b偺抣偼丄initial偺幚峴弴偺塭嬁傪庴偗丄僔儈儏儗乕僞枅偵堘偆抣傪昞帵偟偰偟傑偆壜擻惈偑偁傝傑偡丅偟偐偟側偑傜丄programa懁偱偼丄僔儈儏儗乕僞偵傛傜偢丄抣偼丄b=0偵昞帵偝傟傑偡丅偙傟偼丄僞僀儉僗儘僢僩偺崁偱弎傋偨傛偆偵丄module偲丄program偱偼丄摨偠帪崗偱傕丄幚峴弴彉偑婯掕偝傟偰偄傞堊偱偡丅

婎杮揑偵偼丄module撪傪愭偵幚峴偟丄恾偱僨僓僀儞乮Active儅僀僫乕儖乕僾)偺埨掕壔屻偵乮module撪僀儀儞僩偑柍偔側偭偨屻偵乯program撪偵惂屼偑堏傝傑偡丅program撪偱偼丄廬棃偲Dual側region(ReActive儅僀僫乕儖乕僾re-active,re-inactive,re-nba..乯偺埨掕壔屻丄program撪偺寢壥偑億乕僩傪捠偠偰丂module撪偵揱攄偟傑偡丅偦偺寢壥丄module撪偺Active儅僀僫乕儖乕僾偵擖偭偰丄嵟弶偐傜傗傝捈偡応崌傕偁傞偱偟傚偆偟丄傑偨媡偵僀儀儞僩偑側偔師偺僞僀儉僗儘僢僩偵峴偔応崌傕偁傞偱偟傚偆丅

***** Veritak SV32 Engine Version 432 Build Dec 31 2012*****

module test.a=0 Value of b=0

program Value test.a=0 Value of b=0

---------- 僔儈儏儗乕僔儑儞傪廔椆偟傑偡丅time=0ns

program幚峴偼丄design偺儅僀僫乕儖乕僾(Active Regions)屻丄ReActive Regions偱峴傢傟傞

忋偺儀儞僠偱丄28峴栚丂a=0;傪a<=0;偲彂偒姺偊偰幚峴偟偰傒傑偡丅偡傞偲寢壥偼丄僔儈儏儗乕僞偵傛傜偢妋掕揑偵側傝丄

***** Veritak SV32 Engine Version 432 Build Dec 31 2012*****

module test.a=x Value of b=x

program Value test.a=0 Value of b=0

偵側傝傑偡丅a<=0;偵傛傝丄僲儞僽儘僢僉儞僌暥偺戙擖偼丄design椞堟(module懁)慡僗僥乕僩儊儞僩偺幚峴屻偵婲偙傞偺偱丄b=a;帪揰偱偼丄偄偢傟偵偟偰傕丂1'bx偱偡丅

堦曽丄program撪偺initial偼丄design(module懁乯偺僲儞僽儘僢僉儞僌戙擖屻偵幚峴偝傟傑偡丅廬偭偰丄偙偺儀儞僠偼丄儗乕僗僼儕乕偱偡丅

program port偺嫇摦乮clocking僽儘僢僋偑側偄応崌乯

僾儘僌儔儉帺懱偼丄僀儞僗僞儞僗傪帩偮帠偑弌棃側偄偺偱丄僾儘僌儔儉偼丄忢偵module偐傜僀儞僗僞儞僗壔偝傟傞懁偵偁傝傑偡丅

偙偺傛偆側応崌偺嫇摦傪師偺椺偱尒偰傒傑偡丅

module top;

logic r;

wire dw1, dw2;

initial begin

r = 0;

#10 r = 1;//Active

end

assign dw1 = r;//Active

p p_i(dw2, dw1);

always @(dw2) //Active

$display("dw2 is %b %t", dw2,$time);

endmodule

program p(output pw2, input pw1);

assign #1 pw2 = pw1;//ReActive

initial

forever begin

@(pw1);//ReActive

$display("pw1=%b %t",pw1,$time);

end

initial begin

#100;//Reactive

$exit();//ProgramDerivedThread偺傒壜

end

endprogram

5峴栚偺r偺曄壔偼丄8峴栚 dw1偵 Active Region偱揱傢傝傑偡丅儌僕儏乕儖撪偺偙偺曄壔偼丄摨帪崗偵僾儘僌儔儉億乕僩偵揱傢傝傑偡丅Reactive丂Region偱丂pw1偼丄曄壔偟丄8峴栚pw2偼丄丄#1屻偺Reactive丂Region偱曄壔偟傑偡丅偦偺曄壔偼丄@(pw1)偱傑偢丄揱傢傝丄億乕僩傪捠偠偰丂儌僕儏乕儖懁偵傕揱傢傝傑偡丅摨帪崗偺program撪偺僀儀儞僩偑恠偒偨偺偱丄傕偆堦搙儊僕儍乕儖乕僾偵栠傝丄Active丂Region偱丄@(pw2)偐傜師偺峴偵峴偒傑偡丅丂

傑偲傔偲偟偰丄

program撪怣崋(曄悢偍傛傃僱僢僩乯偼丄偡傋偰Reactive丂Regions偱偺傒偱摦偔丂program

net偲偟偰埖傢傟傑偡丅堦曽丄program奜偱愰尵偝傟偨怣崋偼乮module/interface/package/$unit傕乯偡傋偰丄design

nets 偵側傝傑偡丅庡偵Active丂Regions偱埖傢傟傑偡丅

奒憌傾僋僙僗

儌僕儏乕儖懁偐傜偼丄program偵懳偟丄奒憌揑側傾僋僙僗偼偱偒傑偣傫丅堦曽丄program偺懁偐傜偼丄module偼丄壜帇偱偁傝丄奒憌揑側傾僋僙僗偑壜擻偱偡丅

偙傟偼丄僥僗僩儀儞僠偺懁(program)偑丄僨僓僀儞傪惂屼壓偵抲偔丄偲偄偆偙偲偲丄僨僓僀儞帺懱偼丄僥僗僩儀儞僠偺塭嬁傪庴偗側偄傛偆偵偡傞偲偄偆峫偊曽偑攚宨偵偁傝傑偡丅

僨僓僀儞懁偱偼丄僾儘僌儔儉懁偐傜偺傾僋僙僗偝傟偨応崌偼丄Reactive丂Region丂偱摦偒傑偡丅捠忢偺傾僋僙僗偱偼丄Active丂Region丂側偺偱丄Design丂Net偼丄擇偮偺Region偱摦偔壜擻惈偑偁傝傑偡丅堦曽program丂怣崋偼丄module懁偐傜偺奒憌傾僋僙僗偼偁傝偊側偄偺偱丄ReActive丂Region偱偺傒摦偒傑偡丅

module top;

reg r;

task t1;

r=0;//module偐傜屇偽傟偨傜Active丂Region/ program偐傜屇偽傟偨傜ReActive丂Region

#2;// module偐傜屇偽傟偨傜Active丂Region/ program偐傜屇偽傟偨傜ReActive丂Region

r<=1;//module偐傜屇偽傟偨傜NBA丂Region/ program偐傜屇偽傟偨傜ReNBA丂Region

endtask

function f1;

r=!r;//module偐傜屇偽傟偨傜Active丂Region/ program偐傜屇偽傟偨傜ReActive丂Region

endfunction

initial begin

t1;

f1;

end

prg test_bench();

endmodule

program prg;

initial begin

#10

top.t1;

top.f1;

end

endprogram

program偺module偺廔椆偺巇曽偺堘偄

module偩偗偟偐側偄応崌偵偼丄僀儀儞僩偑恠偒傞偐$finish偑屇偽傟傑偱丄柍尷偵憱傝傑偡偑丄program偑偁傞応崌偵偼丄program偺慡initial暥偑枛抂偵払偡傞偲廔椆偟傑偡丅

-program偺曽偼丄僥僗僩儀儞僠傪憐掕偟偰偍傝丄慡initial暥偑枛抂偵払偟偨=僥僗僩廔椆偲偄偆偙偲偱偟傚偆丅

師偺椺偱偼丄儖乕僾偼丄#1000傑偱憱傝懕偗傑偡偑丄

module prog14;

initial

fork

forever begin

#10;

$display("Hi 儖乕僾拞偱偡丅");

end

#1000 $finish;

join_none

initial #31;

endmodule

摨偠僜乕僗偱丂module 傪program偵偟偨偩偗偺僜乕僗偱偼丄#31偱廔椆偟傑偡丅

***** Veritak SV32 Engine Version 433 Build Jan 3 2013*****

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

---------- 僔儈儏儗乕僔儑儞傪廔椆偟傑偡丅time=31ns

乮2峴栚偺initial偼丄fork-join_none偵傛傝time0偱廔椆偟傑偡丅12峴栚偺initial偼丄#31偱廔椆偟傑偡丅寢壥偲偟偰丄#31偱偡傋偰偺initial偑廔椆偡傞偺偱丄廔椆偲側傝傑偡丅乯

乮廔椆偝偣傞撪晹揑側庤弴偼丄慡initial偑枛抂偵払偟偨傜丄program桼棃偺偡傋偰偺僗儗僢僪傪廔椆偝偣偰($exit)偐傜丄埫栙偺$finish傪屇傫偱廔椆偝偣偰偄傑偡丅乯

fork -join_non 偁傞偄偼丄fork-join_any偱惗惉偟偰僗儗僢僪偑憱偭偰偄傞嵟拞偼丄掆巭偝偣偨偔側偄応崌偼丄

師偺傛偆偵 wait fork丂偱慡偰偺惗惉僗儗僢僪偺廔椆傪懸偪傑偡丅

program prog14b;

initial

begin

fork

forever begin

#10;

$display("Hi 儖乕僾拞偱偡丅");

end

#1000 $finish;

join_none

wait fork;//偙偺initial偱惗惉偟偨偡傋偰偺僗儗僢僪偺廔椆傪懸偮

end

initial #31;

endprogram

...

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

Info: $finish僐儅儞僪傪幚峴偟傑偡丅time=1000ns

$exit偲偼

偙傟傪initial偺搑拞偐傜偱傕偱偒傞傛偆偵偟偨偺偑丄$exit偱偡丅$exit偼丄僾儘僌儔儉桼棃偺僗儗僢僪偐傜偟偐屇傇偙偲偼偱偒傑偣傫丅($exit傪儌僕儏乕儖偺initial峔暥忋偱屇傇偙偲偼偱偒傑偣傫丅乯丂昞柺揑側廔椆偺巇曽傪尒傞偲丄$finish偲嬫暿偑偮偐側偄偲巚偄傑偡丅

program prog16;

initial

fork

forever begin

#10;

$display("Hi 儖乕僾拞偱偡丅");

end

#1000 $finish;

join_none

initial #31;

initial #21 $exit();

endprogram

***** Veritak SV32 Engine Version 433 Build Jan 3 2013*****

Hi 儖乕僾拞偱偡丅

Hi 儖乕僾拞偱偡丅

---------- 僔儈儏儗乕僔儑儞傪廔椆偟傑偡丅time=21ns

program 偲module偺堘偄

program偲module偺堘偄傪傑偲傔傞偲埲壓偺傛偆偵側傝傑偡丅

|

梡搑 |

僞僀儉僗儘僢僩撪僼僃乕僘偺屇徧 |

奒憌壜帇 |

僀儞僗僞儞僗壔 |

埫栙僀儞僗僞儞僗壔 |

always 宯僾儘僙僗 |

廔椆 |

$exit 偵傛傞廔椆 |

| module |

design |

Active丂Region |

program傪擿偔偙偲偼晄壜 |

壜擻 |

壜擻 |

壜擻 |

僀儀儞僩偑柍偔側傞偐$finish |

晄壜 |

| program |

test bench |

ReActive丂Region |

帺桼偵module撪傪擿偔偙偲偑偱偒傞丅 |

program偼丄program/module 傪僀儞僗僞儞僗壔偱偒側偄 |

壜擻 |

晄壜 |

program撪慡initial偑枛抂傑偱払偟偨

傕偟偔偼丄$exit/$finish |

壜擻 |

側偤always偑側偄丠

always偼丄尦乆偼丄僴乕僪僂僃傾偺儌僨儕儞僌梡搑偱偡丅

傕偟傕always暥傪嫋偟偨偲偡傞偲丄慡initial偺廔椆=僥僗僩偺廔椆偲偡傞偙偲偼偱偒偢丄帺摦廔椆偺宍偑偲傟側偄偙偲偵側傝傑偡丅僥僗僩儀儞僠亖僥僗僩僔僫儕僆偲偄偆僔乕働儞僔儍儖揑側傕偺偲憡梕傟側偄傕偺偐傕偟傟傑偣傫丅乮initial

forever 偱婡擻揑偵偼丄摨摍偺婰弎偑偱偒傑偡丅乯

埫栙偺僀儞僗僞儞僗壔

module偲摨條偵丄program傕埫栙偺僀儞僗僞儞僗壔偑偱偒傑偡丅偨偩偟丄program偼丄懠偺program傗module傪僀儞僗僞儞僗壔偱偒側偄偺偱丄nested

module偺傛偆側奒憌壔偼丄偱偒傑偣傫丅

module prog28;

bit clk=0;

int counter;

always #10 clk=~clk;

always_ff @(posedge clk) begin

counter&le=counter+1;

$display(" module: counter=%h %t",counter,$time);

end

program my_prog;

initial

fork

forever begin

@(posedge clk);

$display("program counter=%h %t",counter,$time);

end

#40 ;

join_any

endprogram :my_prog

endmodule : prog28

***** Veritak SV32 Engine Version 433 Build Jan 7 2013*****

module: counter=00000000 10

program counter=00000001 10

module: counter=00000001 30

program counter=00000002 30

---------- 僔儈儏儗乕僔儑儞傪廔椆偟傑偡丅time=40ns

忋偺僾儘僌儔儉偱偼丄fork -join_any偱丄擇偮偺僗儗僢僪傪惗惉偟偰偄傑偡丅堦偮偼丄forever

儖乕僾偱丄傕偆傂偲偮偼丄#40偱偡丅#40屻丄壓偺僗儗僢僪偼丄廔椆偟丄fork 傪婲摦偟偨恊僗儗僢僪偵惂屼偑堏傝傑偡丅偡傞偲偦偙偼丄initial

偺枛抂丂偐偮桞堦偺僾儘僌儔儉僗儗僢僪側偺偱丄僔儈儏儗乕僔儑儞慡懱偑廔椆偟傑偡丅

忋偺寢壥偱丄module懁偺僇僂儞僞昞帵偲丂program懁偺僇僂儞僞昞帵偑堦偮堘偆偙偲偵拲堄偟偰偔偩偝偄丅

乮module懁偼丄Active丂Region丄program懁偼丄ReActive丂Region偱摦偒傑偡丅乯