VeritakSV の評価結果 Oct.18..2010 updated by Tak.Sugawara

1.目的

開発中のSIMエンジンの評価を行い、フレームワークの検証を行う。 比較対象としてModelSimXE6.5Cを使用。

2.ベンチ

| Item | Description | Remarks |

|---|---|---|

| Machine | Q9550(2.87GHz) DDR2 8GB memory Core i7 920 DDR3 6GB memory |

|

| OS | Vista Ultimate 32bit (Q9550) Windows7 64bit (Core i7) |

|

| Test Bench | Verilator's Site Bench/ FZ80/ Etc. | |

| Simulator | VeritakSV3.83A(0.39α) /Veritak3.75(Basic/Pro) MXE6.5C(Not Starter. Full Xilinx Edition of Modelsim) |

|

| Measured Time | From Simulation Starts to Simulation ends. Not include compile time. |

Veritak:Optimized Debug:Normal/ Level/2/NBA/Fast Switch |

3. 結果

コンパイル後実行から終了までの時間を計測

Machine Q9550 Vista Ultimate 32bit-8GB DDR2

| Category | Bench Test Name | Veritak-Pro(sec) | VeritakSV(sec) | MXE (sec) | MXE/VeritakSV | Veritak SV Remarks | |||

| w/o waveform | w/ waveform | w/o waveform |

w/ waveform |

w/o waveform |

w/ waveform |

||||

| Gate | C6288(ISCAS'85) | 14 | 0.38 | 0.83 | 57.44 | 151.96 | 151x | 84x | CycleBased |

| Altera | Altera PLL | 15 | 2.69 | 3.25 | 9.36 | 20.53 | 3.59x | 6.3X | |

| ddr | 34 | 10.0 | 11.8 | ||||||

| ddr3 | 78 | 28 | 37 | ||||||

| ddr2-avalon | 20 | 6.18 | 7.0 | ||||||

| rapid-io | 121 | 27.6 | 35.16 | ||||||

| pci-express | - | 19 | 25.5 | ||||||

| Xilinx | DCM | 69 | 12.8 | 17 | 21.12 | 39.34 | 1.65x | 2.31x | |

| RAM36 | 17 | 7 | 7.2 | 142 | 149.1 | 20.29x | 20.71x | ||

| pci-xilinx | 15 | 4.92 | 7.1 | ||||||

| ddr2 -m | 2 | 0.86 | 0.96 | ||||||

| ddr3-11.1 | 204 | 91 | 101 | ||||||

| Small Design | WB_Z80(opencores) | 28 | 6.1 | 6.57 | 69.56 | 83.87 | 12.4x | 12.8x | |

| DIV(opencores) | 136 | 63 | 70 | 556 | 682 | 8.83x | 9.74x | ||

| USB1.1(opencores) | 21 | 8.7 | 9.43 | 1013 | 120 | 11.61x | 12.72x | ||

| m68k(opencores) | 137 | 32 | 119 | 562 | 1147 | 17.56x | 9.64x | ||

| ata(opnecores) | 107 | 36.6 | 107 | 732 | 1161 | 20.0x | 10.85x | ||

| tv80(opencores) | 10 | 5.3 | 6.0 | 31.12 | 75.69 | 5.87x | 12.62x | ||

| fz80 | 15 | 5.43 | 6.43 | 42.6 | 71.17 | 8.82x | 11.07x | CycleBased | |

| AES(sugawara-systems.com) | 7 | 2 | 2.84 | 18.22 | 67.61 | 9.12x | 23.78x | CycleBased | |

| VGA(user contributed) | 17 | 9 | 19 | 140 | 292 | 15.56x | 15.37x | ||

| conmux(opencores) | 14 | 4.75 | 5.15 | 82.75 | 148 | 17.43x | 28.74x | ||

| AC97(opencores) | 392 | 202.9 | 230 | 1868 | 2030 | 9.21x | 8.83x | ||

| H8(sugawara-systems.com) | 5 | 2.05 | 2.4 | ||||||

| YACC-w/o cache(opencores) | 65 | 81 | |||||||

| YACC-w/ cache(sugawara-systems.com) | 215 | 135 | 165 | ||||||

| openrisc(opencores) | 5 | 1.48 | 1.84 | 14.58 | 17.26 | 9.82x | 17.26x | ||

| A0(sugawara-systems.com) | 4 | 2.71 | 2.96 | 11.08 | 16.44 | 4.09x | 5.55x | ||

| LatticeMico32 | 387 | 126 | 146 | 765 | 2018 | 6.07x | 13.82x | ||

| fpu(opencores) | 1636 | 432 | 750 | 3844 | 12950 | 8.90x | 17.5x | ||

| Large Design | PCI(opencores) | 305 | 557 | 2482 | 5533 | 8.06x | 9.93x | ||

| Ethernet(opencores) | 322 | 476 | Iterationlimit | - | |||||

| Basic Component | base_test_bench_delay | 9 | 6.04 | 25.11 | 4.15x | ||||

| base_test_bench_nba_delay | 10 | 7.27 | 54.78 | 7.54x | |||||

| base_test_bench_prop | 8 | 0.53 | 2.92 | 5.51x | |||||

| base_test_bench_prop_delay | 50 | 8.35 | 76 | 9.11x | |||||

| base_test_bench_prop_nba | 53 | 10.61 | 107 | 10.08x | CycleBased | ||||

| base_test_bench | 3 | 0.43 | 1.36 | 3.16x | |||||

| base_test_bench_inv | 3 | 0.44 | 1.32 | 3.0x | |||||

* w/o : 波形Saveなし

w/ : デザイン全体の波形Saveあり

4.考察

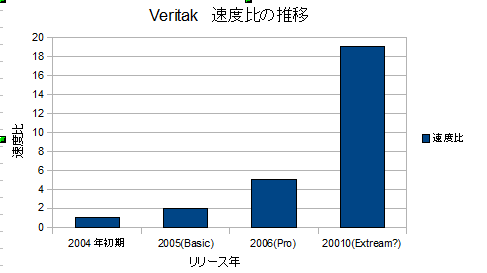

4.1 速度比

MXEとの比較では、全体の95%のベンチで3倍速以上、平均的には、MXE比10倍速が得られた。現行VeritakPro-Fastモードの比較では、3倍速程度となった。なお、MXEは、40%

of PE、SEは、PEの1-3xとされている。

4.2 波形追加

波形を追加すると、1.1倍から2倍程度に速度低下している。一般に低速なシミュレータでは、波形追加しても目立った速度低下は起きない。しかし、高速なシミュレータでは、波形を追加すると、SIMEngineよりも波形処理の方が重くボトルネックになることがある。VeritakSVでは、GUI部のマルチスレッド化で分散処理することにより、波形追加による速度低下を抑えている。特に大規模デザイン(上表でPCIやEthernet等)、または長期シミュレーション(fpu)では、ディスクアクセスがネックになるがその場合でも効果的に作用していると言える。勿論、この優位性は、DualCPU以上のマシンでのみ発揮される。SIMエンジンに1CPU,波形処理に1CPU,大量にログテキストを吐く場合には、さらに1CPUあるのが理想的であるので、VeritakSVのパワーをフルに発揮するには3CPU以上を推奨する。

64 bit Simulatorの効果

<32ビットの限界>

32ビットOS環境下では、1プロセスあたりのユーザメモリは、搭載RAM容量によらず2GBMaxになる。これを上回るデータが発生した場合は、ディスクに退避されることになる。これは、OSの制限であってアプリケーション側では避けることができない。このために例えば8GBというRAMを搭載していても32ビットOS下では、有効に生かすことはできない。

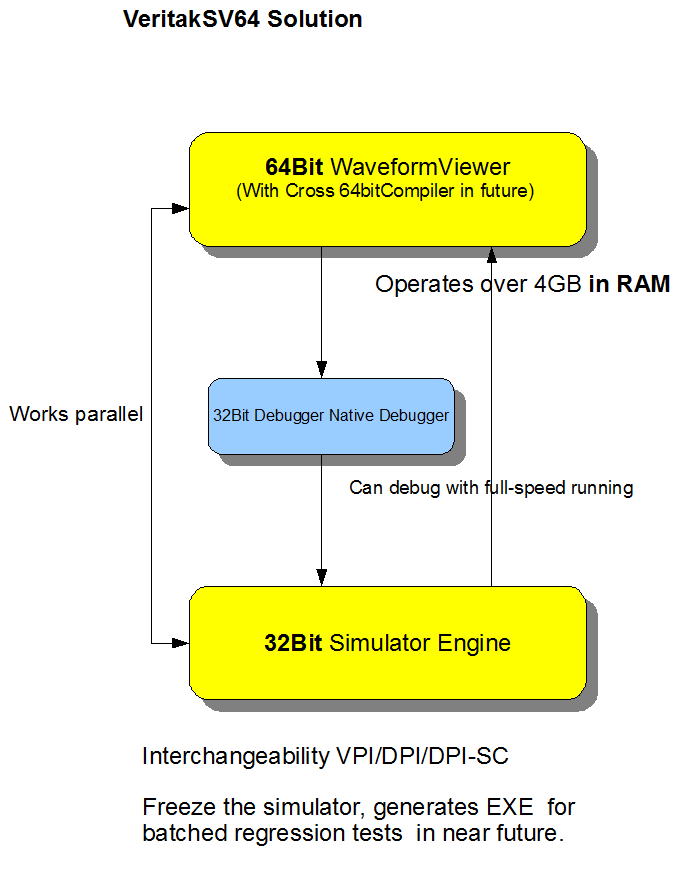

そこで、VeritakSVでは、64ビットOS環境下で動作する専用GUI(VeritakSV64)を搭載してこの問題に対処する。なお、SimEngine自体は、32ビットで動作するので、従来通り外部環境インターフェースVPI/DPI/DPI-SCは変更の必要がない。

上の32ビットOS環境データで、波形追加で比較速度劣化の大きいベンチについて、64ビット環境(VeritakSV64)との比較を示す

| Category | Bench Test Name | VeritakSV(sec) 8GB-32ビットVista |

VeritakSV64(sec) 6GB-64ビットWindows7 |

MXE (sec) 8GB-32ビットVista |

MXE/VeritakSV64 | ||||

| w/o waveform | w/waveform | w/o waveform | w/ waveform | w/o waveform |

w/ waveform |

w/o waveform |

w/ waveform |

||

| Small | ATA | 36.6 | 107 | 32 | 40.7 | 731 | 1161 | 24x | 29x |

| Small | VGA | 9 | 19 | 8.2 | 11.6 | 140 | 292 | 17x | 24X |

| Small | M68K | 32 | 119 | 30 | 40.1 | 562 | 1147 | 19x | 29x |

<マシン性能比 Q9550-Corei7 vs 920>

波形なしで比較してみると、32ビットマシンと64ビットマシンの速度差は、殆どない。WOW64のオーバヘッドは、殆どないと考えられ、速度差は、Q9550とCorei7-920の性能差と見る。

<安くなったDDRを生かす>

これに対して、波形ありでは、64ビットマシンとの差は歴然としている。上の考察の通り、6GB搭載RAMが有効に生かされ、ディスクアクセスがなかった為に64ビットマシンでは目立った劣化がない。このように、大規模・長期シミュレーションでは、64ビット環境で,マルチCPUを有効に使い、かつ安くなったDDR-RAMを大量に搭載することで、ドラスティックな体感速度の向上が得られる可能性が高い。

4.3 Native Debugger

VeritakSVでは、NativeDebuggerが搭載されているのでデバッグモードは存在しない。最高速で走行中に、手続き構文のみならず、ネット構文にもブレークポイントが置け、ツールチップ付きのシングルステップ行RUNが利用可能である。

5.課題

64ビットOS環境下では、32ビットのワークスペースは2GBではなく、ほぼ32ビット限界の4GBが利用可能であり、従来より2倍強デザイン規模の拡大が可能になる。64ビットクロスコンパイルを構築し、さらなる大規模デザインに対応する必要がある

<参考>

http://www.synopsys.co.jp/products/technology/vcs/cross_compile_tb.html

遅延なしゲートシミュレーションの高速化、RTLソースなしIPをゲートレベル記述で高速シミュレートする。

シミュレータの内部状態Save機能の搭載。Veritakでは、シリアライズ機能でSaveしてきたが、メンテナンス性に難があった。メモリプールを利用した高速な状態Save方式の開発が必要。 結果的にExe化することができる。 EXEがあれば、コンパイル時間不要で、バッチ化したregression testを並列に何本も走らせることが容易になる

が未だ残っているが基本的なフレームワークとしては、確認できたと考える。これらは、

といった背景技術により支えられている

6. 結論