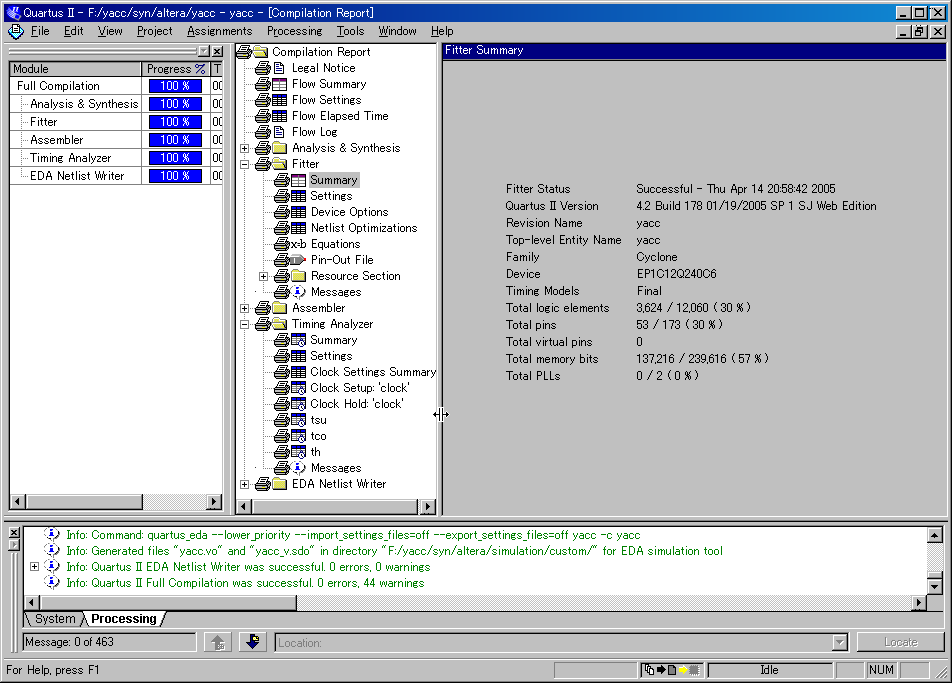

Cyclone

6.論理合成

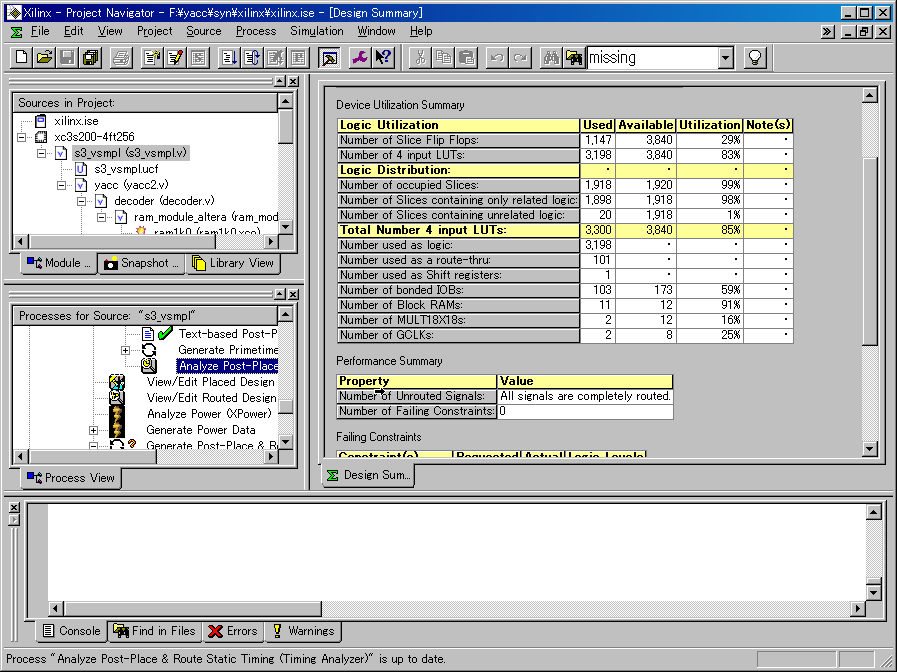

Stratixでパイプラインの検討しましたので、Xilinxでは不利な結果になっています。また、スタータキットのデバイスは遅いランク品で99%のリソース使用率です。それらを考慮してもこれほど差がでるとは思いませんでした。

| プラットフォーム | 論理合成結果 スライス数・セル数 | 動作周波数 | 備考 |

| XILINx Starter Kit(XC3S200 ISE7.1) | 1918(99%) | 25MHz | AREA優先、乗算2CLOCK |

| Cyclone(EP1C12Q240C6Web Editiion Quartus4.2SP1) | 3624(30%) | 104.7MHz | SPEED優先、乗算32CLOCK Version、 |

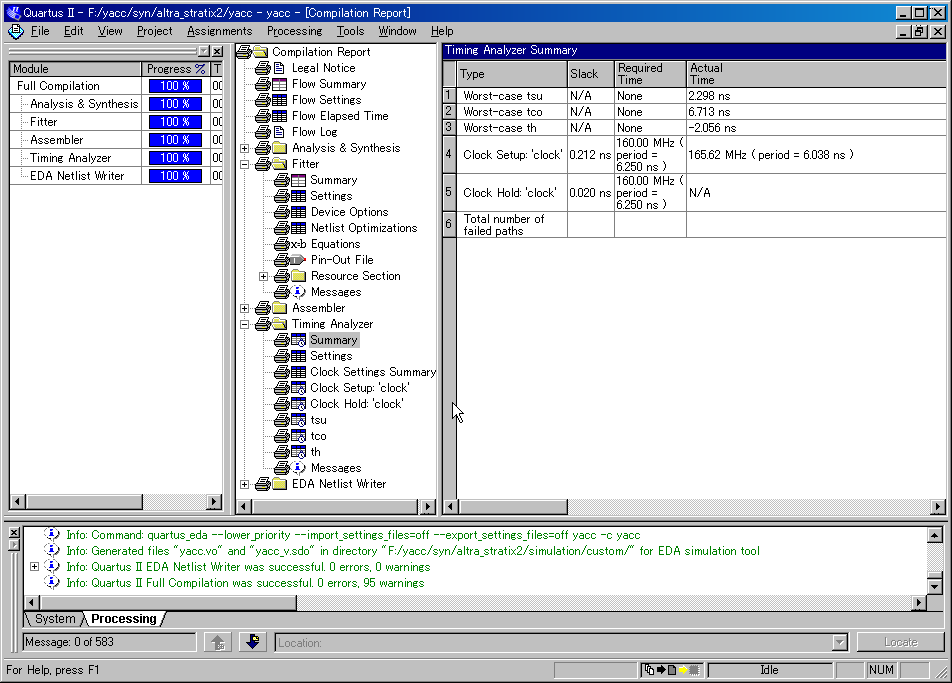

| StatatixⅡ(EP2S15F484C3 Web Editiion Quartus4.2SP1) |

2926(23%) | 165MHz | SPEED優先、乗算2CLOCK Version、 |

Xilinx 合成結果

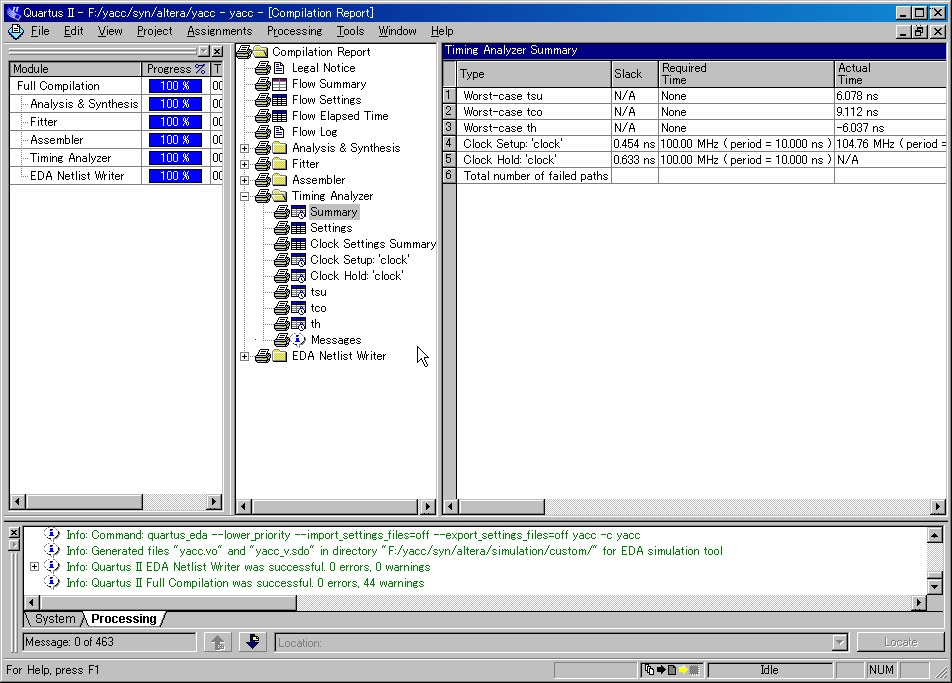

Cyclone

StratixⅡ

Stratixは、ゲートシミュレーションでうまく動かず苦労しました。今回の原因もALUの減算部分にありました。H8で使った記述もうまく動かず、結局減算をmoduleを分けて記述するとなぜか動いてくれました。(多分合成のバグです。)