12.Cコンパイル例

12.1 RTL

RTL シミュレーションでは、シミュレータ上で走らせるために、Cプログラムの出力をUARTから、コンソールに変更しています。また、実時間で数十msで終わるようにCプログラムを書いています。実時間で数十msでも、RTLシミュレータ上では、長大な時間を要することに注意してください。(特にXilinxでは、遅いです。RAMの記述方法が違うためです。)

| フォルダ | C プログラム | 内容 | バッチファイル | Veritak Project(\bench\verilog) |

| \bench\c_src\count | count_tak.c | Steve Rhords氏によるCPU動作チェック | compile.bat | altera_rtl/xilinx_rtl |

| \bench\c_src\pi | pi2.c | π十桁計算プログラム | compile.bat | altera_rtl_no_wave/xilinx_rtl_no_wave |

| \bench\c_src\dhrystone | dhry21_tak.c | ドライストーンプログラム | compile.bat | altera_rtl_no_wave/xilinx_rtl_no_wave |

| \bench\c_src\reed solomon | rs_tak.c | Phil Karn氏のプログラムを組み込みCPU用にポート | compile.bat | altera_rtl_no_wave/xilinx_rtl_no_wave |

| \bench\c_src\calculator | uart_echo_test.c | PCターミナルを利用した電卓プログラム。割り込みのチェックに使用 | compile.bat | altera_calculator_test_using_uart_echo/xilinx_calculator_test_using_uart_echo |

RTLシミュレーション手順

12.2 ゲートシミュレーション

RTLシミュレーションのcountでのメモリ初期化ファイルをコピーしゲートシミュレーションを行いました。ゲートシミュレーションは、RTLのさらに数倍時間がかかるので、UART出力を待っていられません。そのため、コンソールに出力させます。RTLのIFを使って合成しています。StratixⅡでは、例によって、非同期リセットがうまく合成されていないので、IFDEF対応しました。(yacc2.v)

また、駆動周波数は、ポストレイアウト後の駆動可能最大周波数にテストベンチを設定し直し、コンソール出力がRTLと同じ結果になることを確認しました。

| フォルダ | Veritakプロジェクトファイル | 駆動周波数 |

| \syn\altra_stratix2\simulation\custom | Gate_altera | 165MHz |

| \syn\altera\simulation\custom | Gate_altera | 100MHz |

| \syn\xilinx | Gate_xilinx | 25MHz |

12.3 FPGA実動作用

RTLとの違いは、出力をUARTにしている点です。また、実時間に見合ったループ数(Cプログラム)にしています。

| フォルダ | C プログラム | バッチファイル | 内容 |

| \syn\c_src\count | count_tak.c | compile.bat | Steve Rhords氏によるCPU動作チェック |

| \syn\c_src\pi | pi2.c | compile.bat | π800桁計算プログラム |

| \syn\c_src\reed solomon | rs_tak.c | compile.bat | Phil Karn氏のプログラムを組み込みCPU用にポート |

| \syn\yacc\bench\c_src\calculator | uart_echo_test.c | compile.bat | PCターミナルを利用した電卓プログラム。 |

<合成方法>

12.4 FPGA 動作確認

| FPGA | FPGA BOARD | Device | Clock | CPU CLOCK | UARTボーレート | 合成 |

| Altera | Future Electronics Cyclone/Nios II Development Board | EP1C12Q240C6 | 50MHz | 50MHz | 115.2KBPS | Quartus4.2 |

| Xilinx | Xilinx Spartan3 Starter Kit | XC3S200-4FT256C | 50MHz | 25MHz | 57.6KBPS | ISE7.1 |

Future Electronics Cyclone/Nios II Development Board Spartan3 Starter Kit

(1) count

RTL と同様の画面が流れます。無限ループになっています。

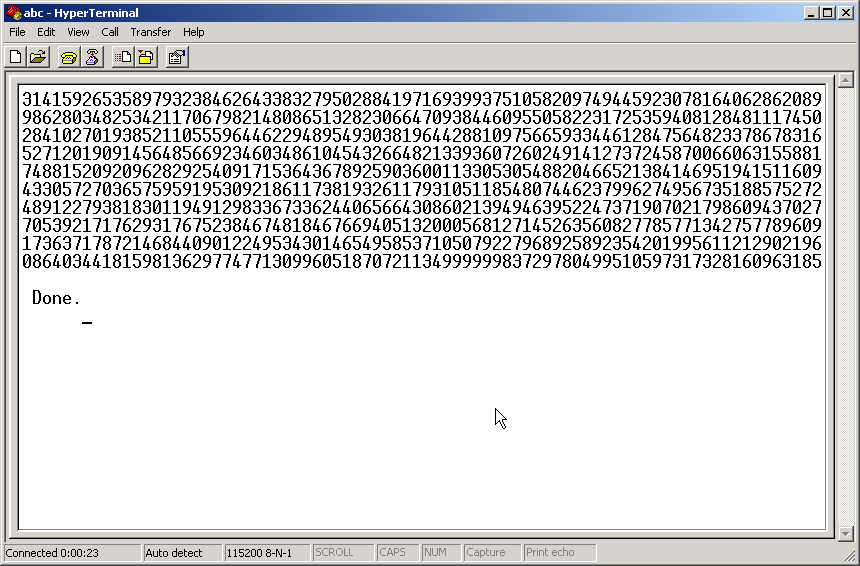

(2) pi

3.1415...と800桁続きます。PCで計算した値と同じです。

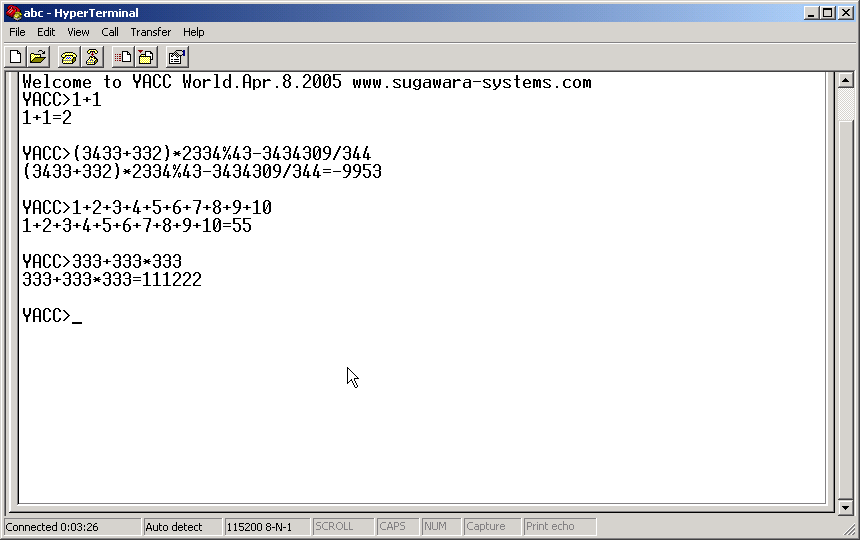

(3)Interactiveな電卓

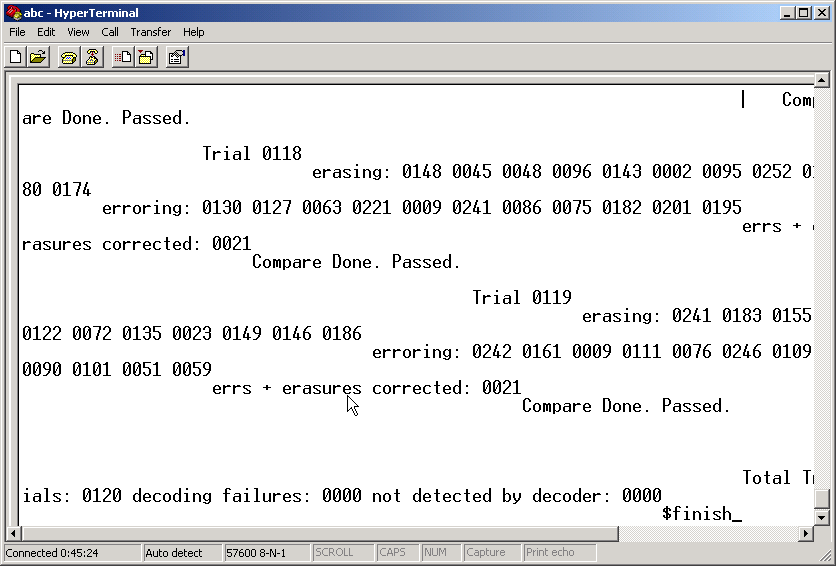

(4)リードソロモン

大変複雑な処理を120回行い、誤訂正は、0です。255個のデータの内、32BYTEのECCが付加され21バイトの訂正を行っています。(Erasure含む)