# Veritak1.41 の速度評価

Nov.15.2004 菅原システムズ 菅原孝幸

# 1. 目的

Version 1.29B から、1.41 では、Veritak 内部 Data 構造を変更している。その、主目的は、速度 Up とメモリ所要量の削減である。

### 2. 結論

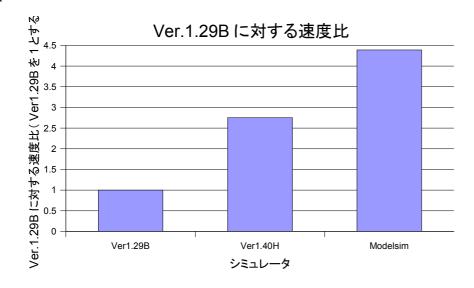

記述により、改善量は、異なり、50% 程度しか改善されないものから、8 倍程度になるものまで様々である。 平均的には、3 倍弱の結果となった。MODELSIM ALTERA 版との比較では、勝るベンチもあるが、総じて 50% 程度の差がある。

## 3. 評価方法

各種ベンチマークプログラムを走らせ、シミュレーション時間(Goから終了までの時間)を比較する。

# 条件

評価ソフトウェア

- VeritakVer.1.29B

- VeritakVer.1.40H(内部 Version)

- MODELSIM-ALTERA5.8C

## ハードウェア

Athron 64 3000+(939ピン) メモリ PC3200 1 GB (512 MB x2: Dual)

### ソフトウェア設定条件

- ・Debug Mode OFF,Save なし。

- 1.40H (Optimize Net Structure オン)

# 4. 結果

| _            |        |                         | シミュレーション時間 (S) |          | 速度比      |      |       |

|--------------|--------|-------------------------|----------------|----------|----------|------|-------|

| ベンチマークプログラム  |        |                         | Α              | В        | С        | A/B  | A/C   |

| 略称           | 行数     | 備考                      | Ver1.29        | Ver.1.40 | Modelsim |      |       |

| A0           | 20K 行  | CBIC 5万ゲート              | 28             | 16       | 17       | 1.75 | 1.65  |

| PR752_100    | 100行   | インスタンス数100x1 FF         | 9              | 6        | 5        | 1.5  | 1.8   |

| PR752_100_32 |        | インスタンス数100x32FF         | 109            | 13       | 9        | 8.38 | 12.11 |

| PR752_1K     |        | インスタンス数 1K x1 FF        | 19             | 9        | 注2)      | 2.11 |       |

| PR752_1K_32  |        | インスタンス数 1K x 32FF       | 132            | 22       | 計測不能     | 6    |       |

| PR752_10K    |        | インスタンス数 10K x1 FF       | 27             | 17       | 計測不能     | 1.59 |       |

| PR752_10K_32 |        | インスタンス数 10K x 32FF      | 149            | 123      | 計測不能     | 1.21 |       |

| PR752_100K   |        | インスタンス数 100K x1 FF      | 注1)不能          | 注3)20    | 計測不能     |      |       |

| USB1.1       | 10 K 行 | OPENCORES               | 332            | 159      | 164      | 2.09 | 2.02  |

| H8           | 5 K 行  | By sugawara-systems.com | 192            | 53       | 36       | 3.62 | 5.33  |

| AES          | 4 K 行  | By sugawara-systems.com | 124            | 67       | 46       | 1.85 | 2.7   |

| SH2          | 10 K 行 | OPENCORES               | 70             | 41       | 23       | 1.71 | 3.04  |

| Multiply_128 | 0.5K行  | Icarus Test Suite       | 167            | 50       | 56       | 3.34 | 2.98  |

| WB_Z80       | 5 K 行  | OPENCORES               | 420            | 124      | 120      | 3.39 | 3.5   |

|              |        |                         |                |          | 平均       | 2.75 | 4.39  |

| PLL          | 20 行   | atlera_mf.v PLL 単体      | 36             | 6        | 2        | 6    | 18    |

注1)デザインが大きすぎて、コンパイルできない。

| Ver1.29B | Ver1.40H | Modelsim |  |

|----------|----------|----------|--|

| 1        | 2.75     | 4.39     |  |

### 5. 考察

1) 一部 Modelsim よりも速いベンチは、あるが、総じて Modelsim が、50% 速い。

特に、PLL 等の Trival な記述では、Modelsim は、圧倒している。逆にインスタンス数が大きい記述(A0)では、Veritak も健闘 している。

- 2) ModelsimAltera 版は、僅か300インスタンス程度で、制限がかかる。

- 3) 10 万インスタンスでは、階層 View 等の表示はできなくなる。メモリも700 MB 以上食っているが、シミュレーションは可能。

- 4) 今回は、Save なしでの比較になっているが、圧縮機能については改善は殆どされていないため、実質2倍程度と推定。

- 5)ダイレクトコンパイル方式とされる Modelsim に対して、Veritak は、Interpreter 方式であり、順当な結果と考えられる。 Veritak の特徴は、全波形 Save にあり、全波形 Save の比較では、その差は、縮小すると思われる。

- 6) AthronXP1.2GHz で見ると、また別な結果(改善比は大きくなる傾向)になる。

注2)コンパイルエラーにはならないが、極端に速度が落ち、計測不能

注3)階層 Viewer が使えない.. の Message はでるがシミュレーションは可能